本文作者:JonathanDodge,P.E.,Mike Zhu, Shusun Qu ,Mike Tian

随着Al工作负载日趋复杂和高耗能,能提供高能效并能够处理高压的可靠SiCJFET将越来越重要。我们将详细介绍安森美(onsemi)SiC cascode JFET,内容包括Cascode(共源共栅)关键参数和并联振荡的分析,以及设计指南。本文为第一篇,聚焦Cascode产品介绍、Cascode背景知识和并联设计。

简介

大电流操作通常需要直接并联功率半导体器件。出于成本或布局的考虑,并联分立器件通常是优选方案。另一种替代方案是使用功率模块,但这些模块实际上也是通过并联芯片实现的。本文总结了适用于所有并联电压栅控型功率半导体(如SiC JFET cascode、SiC MOSFET、Si MOSFET、IGBT等)的通用最佳实践方案。并联Cascode等高增益器件尤其具有挑战性。遵循这些实践方案有助于成功实现 SiC JFET cascode的并联工作。

Cascode背景知识

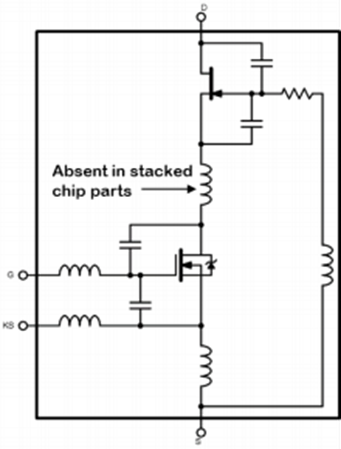

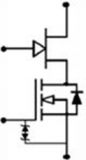

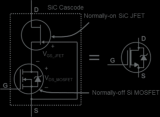

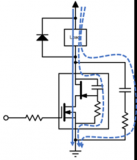

如图 1 所示,cascode 结构是由一个常开 SiC JFET(碳化硅结型场效应晶体管) 与一个低压 Si MOSFET (硅金属-氧化物半导体场效应晶体管)串联而成。JFET的 栅极直接连接到 MOSFET 的源极,JFET 的栅极电阻是 JFET 芯片的一部分。

MOSFET 漏极-源极电压是 JFET 栅极-源极电压的反相,从而使cascode 结构呈现常关特性。正如《Cascode入门》中所述,Cascode与其他功率晶体管的主要区别在于,一旦 VDS超过 JFET 的阈值电压,就没有栅极-漏极电容。 这是因为 JFET 没有漏极-源极电容,因此Cascode结构的开关速度极快。 这一特性与寄生电感问题相结合,是Cascode并联工作中需要解决的核心问题。

图 1 带杂散阻抗的Cascode结构

并联的挑战

静态电流失配

静态电流失配是指并联器件在开关瞬态稳定后,并联器件之间的电流不匹配现象。对于具有热不稳定性(如负温度系数导通电阻的旧式硅二极管或穿通型IGBT)的器件尤其值得关注。如果各个器件导通电阻的变化(分布)足够小(即经过分选的器件),并且为了弥补不可避免的电流失配而留有裕量,则具有负温度系数的器件可以成功并联。

有一个广为流传的误解,认为正温度系数导通电阻能强制均流,从而有利于并联。实际上,正温度系数仅确保热稳定性。现代功率半导体(包括 SiC JFET、SiC MOSFET、场截止 IGBT 等)的参数分布较窄,这进一步强化了人们对于正温度系数在均流方面具有强大作用的看法,但决定静态均流的是参数分布和共同的散热装置。

动态电流失配

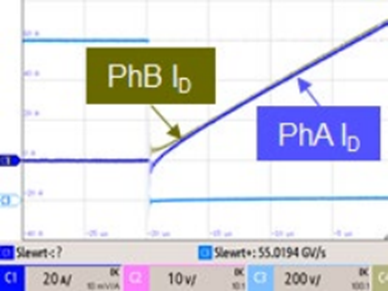

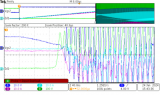

图2 阈值电压失配导致的动态电流失配

动态电流失配是由MOS栅控器件和JFET器件固有的器件间阈值电压变化、电流环路的不对称性以及栅极驱动器之间传播时延差异(如果适用的话)所引起的。阈值电压较低的部件会较早导通、较晚关断,因此会产生更多的硬开关损耗。在开关频率非常高的情况下,这种情况更加令人担忧。

图2显示了两个并联cascode电路在导通时的动态失配。电流失配迅速减小是典型的现象,因为稳态均流主要由RDS(on)决定。在计算中,使用数据表中RDS(on)和RθJC的最大值,可以为并联时的静态和动态电流失配提供安全裕量。

并联设计还有哪些挑战?后续推文我们将继续介绍。

-

安森美

+关注

关注

33文章

2131浏览量

95808 -

JFET

+关注

关注

3文章

202浏览量

23544 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

SiC

+关注

关注

32文章

3847浏览量

70065 -

Cascode

+关注

关注

0文章

6浏览量

7215

原文标题:SiC JFET并联难题大揭秘,这些挑战让工程师 “头秃”!

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

安森美SiC Combo JFET的静态特性和动态特性

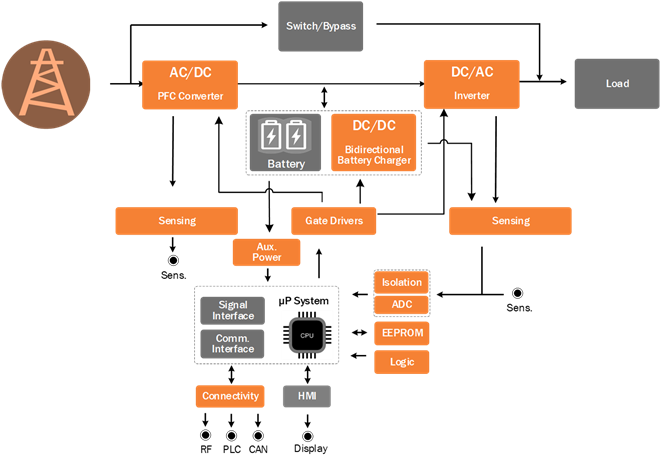

安森美丰富的SiC方案解决新一代UPS的设计挑战

安森美SiC Combo JFET技术概览和产品介绍

安森美半导体在功率SiC市场的现状与未来

安森美半导体将重点发展哪些领域的SiC技术?

安森美大手笔投资捷克,扩建SiC功率器件制造工厂

安森美1.15亿美元收购Qorvo碳化硅JFET技术业务

安森美收购碳化硅JFET技术,强化AI数据中心电源产品组合

安森美完成对Qorvo碳化硅JFET技术的收购

安森美SiC cascode JFET并联设计的挑战

安森美SiC JFET和SiC Combo JFET产品组合介绍

安森美SiC Cascode JFET与SiC Combo JFET深度解析

安森美SiC Cascode JFET的背景知识和并联设计

安森美SiC Cascode JFET的背景知识和并联设计

评论