来源:超能网

最近一段时间,围绕国产的麒麟950处理器及高通的骁龙820处理器产生了很多争论,华为经过K3V2、麒麟910、麒麟920及麒麟930系列处理器的洗礼,在麒麟950处理器上已经成熟起来,这款处理器号称三项世界第一——首个商用A72 CPU核心、首个16nm FinFET Plus工艺以及首个商用Mali-T880 GPU核心。不过麒麟950在很多方面也很保守,GPU只有MP4四核,远低于三星Exynos 8890的MP12,基带方面还停留在Cat6级别,也大幅落后骁龙820,ISP方面就更不如骁龙820了。

在此之前,国外权威网站Anandtech借着小米手机5简单比较了麒麟950与骁龙820的性能,初步测试显示麒麟950的能效比很强大,甚至大幅领先骁龙820,部分CPU性能测试中也超越了骁龙820,只不过在GPU性能测试中麒麟950就远远不如了,这点跟我们之前的分析是差不多的,麒麟950在GPU方面的保守使得其性能都没有超过上代骁龙810的水平。

如何评价麒麟950的技术水平?继而引出了麒麟950处理器是否意味着国产手机处理器能达到甚至超越了国际一流水平的骁龙820/Exynos 8890处理器的问题。最近这个话题在微博、微信及其他社交媒体上讨论的很热烈,嘲讽麒麟950不行的人有很多(不管是出于什么动机),不过自发支持华为或者华为发动的水军势力也不弱,双方激烈斗争了很多回合了。

华为官方也在各路媒体出了很多文章引导舆论,前两天在微博上发表了一篇长文,解释了华为手机是如何率先量产16nm FinFET Plus工艺的。虽然是官方软文,不过很多内容值得一看,介绍了处理器设计与生产之间的关系以及简单的处理器研发、制造流程。

以下是华为手机的原文,大家可以参考下,也是个学习的过程。

Mate8上搭载了华为自主研发的重磅级芯片麒麟950。是业界首款商用台积电16nm FinFET Plus技术的SoC芯片。该技术相比20nm工艺,性能提升40%,功耗节省60%。那么为什么华为要选择16nm FinFET Plus工艺呢?16nm FinFET Plus工艺是台积电的技术,要领先也是人家台积电领先,跟你华为有什么关系?这样领先的制造工艺,可以给你华为用,也可以给别的厂商用,华为有什么可领先的呢?下面就来为大家揭秘这其中的真相。

◆ 芯片工艺如何选择 关键看能效比

麒麟950为何要选择16nm FinFET Plus工艺?毕竟在当时16nm FinFET Plus工艺并不成熟也不稳定,没有量产的依据可循,投资还那么庞大。我们假设以28纳米为基础,20纳米用传统的晶体管架构走下去,集成度还OK,是28纳米的1.9倍,但是功耗只能降到75%。而16nm FinFET技术,正好解决了28nm以下的漏电问题,功耗只有28nm的30%,性能可以提升两倍。这是很完美的一个工艺。所以华为芯片做出了通过技术创新突破瓶颈的选择:开始了16nm FinFET Plus工艺的技术突破之旅。

◆ 芯片能否量产 关键看前端设计水平

芯片生产链,主要分为前端设计、后端制造及封装测试,最后才投向手机厂商。不同的厂商负责不同的阶段,环环相扣。

前端设计是整个芯片流程的“魂”,从承接客户需求开始,到系统架构设计、方案设计,再到编码、测试、布局布线,最终输出图纸交给代工厂做加工。华为主要负责的就是这个阶段。成功开发一款SoC芯片,有数百个IP,这些IP都需要提前大半年时间定制,都要在同一时间点同一种工艺下集成,对前端设计人员要求极大。一旦工艺出现变化,哪怕是从16nm FinFET变换成16nm FinFET Plus,所有的IP都需要重新定制,有的时候,新工艺库中某个参数变更,布局布线就要来回修改几十次。这些工作都需要前端设计工程师对新工艺一定要有正确的理解和判断,否则不可能高质量按时完成。

后端制造是整个芯片流程的“本”,拿到图纸以后,台积电就开始光刻流程, 16nm FF+工艺的基本生产周期要4~5个月左右。 封装测试是整个芯片流程的“尾”,台积电加工好的芯片是一颗颗裸核,外面没有任何包装。裸核是不能集成到手机里的,需要外面加封装,用金线把芯片和PCB板连接起来,这样芯片才能真正的工作。一般封测周期在1个月左右。

介绍到这里,就基本上可以说清楚芯片是如何量产出来的了。一颗芯片能在哪个工艺下量产,除了代工厂要具备芯片加工制造的能力以外,设计厂商也需要具备芯片在同种工艺下的设计能力。就像房地产公司要开发一座房子,是用砖头盖还是用木头盖,盖成别墅还是小木屋,这些都是房地产设计公司决定的,而不是建筑公司决定的,建筑公司只掌握着工匠技术。这就能解释,为何华为敢说自己麒麟950是业界首款16nm FinFET Plus工艺下量产的SoC芯片了。

◆ 结语

大部分的手机用户最关心的是性能和功耗问题,是否流畅,是否耗电。这些体验跟CPU的选择、工艺的选择是密切相关的。对于旗舰产品来说,过硬的性能和能效比是最重要的!华为非常在意消费者的感受,并希望通过自己过硬的技术能力,不断挑战自己,突破自己,以使得产品能达到甚至突破消费者的预期。当然这也解释了为什么不是所有厂商都能在第一时间采用台积电16nm FinFET Plus这样顶尖的制造工艺的原因。

发布评论请先 登录

易灵思2026技术研讨会圆满举办,16nm 钛金系列重塑FPGA效能边界

旋极星源基于22nm工艺完成关键IP发布与验证

芯片封装等领域清洁除尘工艺解决方案

1.4nm制程工艺!台积电公布量产时间表

2nm芯片量产狂欢下,一个被忽视的“测不准”危机

元服务交易评价

华邦电子推出先进 16nm 制程 8Gb DDR4 DRAM 专为工业与嵌入式应用而生

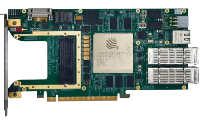

【PCIE725G】青翼凌云科技基于 PCIe x16 总线架构的 JFM9VU9P FPGA 高性能数据预处理平台(100%国产化)

华为如何评价其最先量产16nm工艺芯片?

华为如何评价其最先量产16nm工艺芯片?

评论