来源:Cadence楷登

近日,Cadence宣布其首款基于 Arm 的系统级小芯片(Chiplet)开发成功并流片,这是一项突破性成就。这项创新标志着芯片技术的关键进步,展现了 Cadence 致力于通过其芯片架构和框架推动行业领先解决方案的承诺。

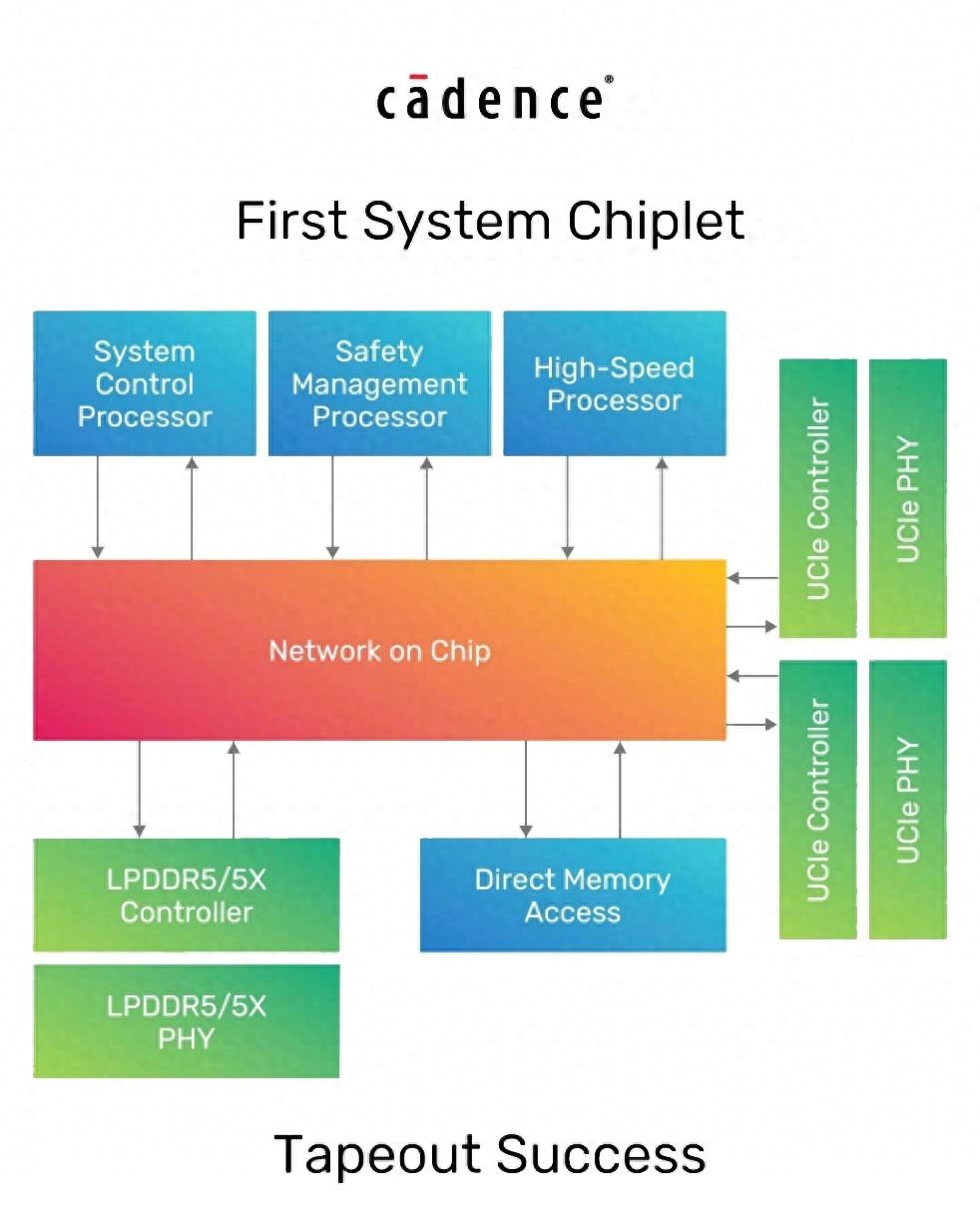

第一个系统级 Chiplet

Cadence 成功制作了业界首款系统级小芯片的原型、设计并流片。该芯片将处理器、系统 IP 和内存 IP 集成在一个封装中,通过通用芯片互连标准 (UCIe™)接口进行互连。该芯片与 Arm 共同开发,符合 Arm 的芯片系统架构(CSA),该标准可确保互操作性并加快芯片的上市时间。

系统小芯片包括管理整个多芯片组 SoC 的资源和功能的功能。该芯片组具有系统处理器、安全管理处理器、Cadence 控制器以及用于 LPDDR5 和 UCIe 的 Cadence PHY IP 等组件,是 Cadence 创新的体现。该芯片组采用 Cadence Janus NoC 技术,可为 UCIe IP 提供高达 64GB/s 的峰值带宽,为 LPDDR5 IP 提供高达 32GB/s 的峰值内存带宽。

与 Arm 携手,共同推进 Chiplet 生态系统

2024 年 3 月,Cadence 和 Arm 正式建立长期合作关系,以提供基于芯片的参考设计和尖端软件开发平台。此次合作将 Cadence 强大的 IP 和 EDA 解决方案与 Arm 先进的 IP 技术相结合,大大降低了设计复杂性并加快了客户的产品上市时间。为进一步的发展奠定了基础,为客户提供了一个全面的开发平台,以实现极佳的性能和效率。

此次合作的核心战略是投资 Arm CSA,从而实现供应商之间更大的组件重用。Cadence 是 CSA 的积极贡献者,正在开发符合此标准的芯片。这些标准允许小芯片(包括 Arm计算子系统(CSS)和 Cadence 系统芯片)实现规模化并加快上市时间。

先进的 IP 技术创新

凭借数十年的 IP 和子系统设计专业知识,硅解决方案事业部可提供高价值解决方案来解决客户挑战。将功能抽象为小芯片 IP 可帮助客户更快地将创新推向市场。Cadence 掌握的先进封装和互连技术可实现可扩展的高性能解决方案,从而提高效率并推动技术进步。

利用 Chiplet 技术改变行业

从单片 SoC 转向基于小芯片的设计,其驱动力在于提高设计效率、缩短平台更新周期以及优化功率、性能和面积(PPA)指标。小芯片支持多代工厂业务模式,在同一封装内集成跨代工厂工艺技术。随着技术密度扩展放缓,芯片对于克服摩尔定律限制和工艺掩模版限制至关重要。新的封装和互连解决方案(包括 2.5D 和 3D 封装以及 UCIe 等芯片到芯片接口)支持这种变革性方法,为客户提供了加速创新和市场准备的途径。

结语

Cadence 在小芯片技术方面的开创性工作代表了半导体行业的重大进步。Cadence 通过创新的架构、强大的 IP 和战略合作伙伴关系,为效率、可扩展性和性能树立了新的标杆。这些发展满足了高性能计算、汽车和数据中心行业不断变化的需求,并帮助客户克服设计挑战并加快产品上市时间。Cadence 始终致力于突破技术界限,塑造小芯片生态系统的未来。

-

芯片

+关注

关注

463文章

54441浏览量

469433 -

ARM

+关注

关注

135文章

9588浏览量

393692 -

Cadence

+关注

关注

68文章

1029浏览量

147347 -

chiplet

+关注

关注

6文章

499浏览量

13650

发布评论请先 登录

Cadence推出专为新一代语音AI与音频应用打造的 Tensilica HiFi iQ DSP

Cadence在Arm Neoverse上扩展其EDA产品组合

Cadence 推出 ChipStack™ AI Super Agent,开辟芯片设计与验证新纪元

Cadence推出高可靠性LPDDR5X 9600Mbps内存IP系统解决方案

Cadence推出全新完整小芯片生态系统

解构Chiplet,区分炒作与现实

2025 Cadence 中国技术巡回研讨会即将开启 ——系统设计与分析专场研讨会(上海站)

Cadence携手NVIDIA革新功耗分析技术

Cadence推出LPDDR6/5X 14.4Gbps内存IP系统解决方案

Cadence推出基于Arm的系统Chiplet

Cadence推出基于Arm的系统Chiplet

评论