ASIC(Application-Specific Integrated Circuit,应用特定集成电路)集成电路性能优化是一个复杂而关键的过程,涉及多个层面的技术和策略。以下是一些关键的优化方法:

一、电路设计优化

- 流水线技术 :通过将复杂的计算任务分解为多个简单的子任务,并在不同的时钟周期内并行处理,可以显著提高电路的性能。

- 并行处理技术 :利用多个处理单元同时处理数据,提高数据处理速度和吞吐量。

- 数据重用技术 :通过缓存和预取等技术,减少数据的重复访问,提高数据访问效率。

- 减少无用操作 :如减少开关和振荡频率等无用操作,可以降低芯片的功耗。

二、时钟管理优化

- 时钟门控 :在不需要时钟信号时,通过关闭时钟门控来减少功耗。

- 时钟域隔离 :将不同的时钟域进行隔离,以避免时钟信号之间的干扰和冲突。

- 时钟频率控制 :根据实际应用需求,合理调整时钟频率,以平衡性能和功耗。

三、芯片制造工艺优化

- 选择先进的制造工艺 :如高速工艺、超高速工艺等,以提高芯片的性能和集成度。

- 优化布线和封装 :合理的布线和封装设计可以减少信号延迟和功耗,提高芯片的稳定性和可靠性。

四、算法和架构优化

- 优化算法 :通过算法优化,减少逻辑复杂度和计算量,提高电路的性能。这包括选择合适的算法、优化算法参数等。

- ASIC架构设计 :合理的系统架构设计,包括模块划分、通信方式等,可以提高整个系统的性能。例如,通过改进芯片的内部结构,可以提高芯片的性能和扩展性。

五、软硬件协同优化

- 硬件/软件协同设计 :通过优化硬件和软件之间的交互方式,提高整个系统的性能。这包括合理的任务调度、数据缓存、软硬件接口优化等。

- 利用仿真工具进行验证 :使用仿真工具对ASIC芯片进行验证,找到可能的性能瓶颈,并进行优化和改进。这有助于在设计早期发现并解决问题,降低后续的开发成本和时间。

六、针对特定应用场景的优化

- 定制化设计 :针对特定应用场景进行定制化设计,以实现更高的性能和效率。例如,在高性能存储系统中,通过优化数据存储和管理、数据访问和处理等算法,提高系统的吞吐量和降低延迟。

- 考虑功耗和成本效益 :在优化过程中,需要综合考虑功耗和成本效益。虽然ASIC加速技术的开发成本较高,但在大量生产后,其成本效益通常较高,且功耗较低。

综上所述,ASIC集成电路性能优化是一个综合性的过程,需要从电路设计、时钟管理、制造工艺、算法和架构、软硬件协同以及针对特定应用场景等多个方面进行综合考虑和优化。通过合理的优化策略和技术手段,可以显著提高ASIC集成电路的性能和效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

集成电路

+关注

关注

5464文章

12686浏览量

375742 -

asic

+关注

关注

34文章

1278浏览量

124951 -

振荡频率

+关注

关注

1文章

24浏览量

16124

发布评论请先 登录

相关推荐

热点推荐

探索 ADE7753:单相多功能计量集成电路的卓越性能

探索 ADE7753:单相多功能计量集成电路的卓越性能 在电子计量领域,精准度与可靠性是衡量一款集成电路优劣的关键指标。今天要为大家详细介绍的 ADE7753 单相多功能计量集成电路,

行芯科技亮相IIC 2026国际集成电路展览会暨研讨会

近日,全球集成电路领域的年度标杆盛会——2026国际集成电路展览会暨研讨会(IIC 2026)在上海圆满落幕。

集成电路制造中薄膜生长设备的类型和作用

薄膜生长设备作为集成电路制造中实现材料沉积的核心载体,其技术演进与工艺需求紧密关联,各类型设备通过结构优化与机理创新持续突破性能边界,满足先进节点对薄膜均匀性、纯度及结构复杂性的严苛要求。

探索MAX20430:四输出迷你电源管理集成电路的卓越性能

探索MAX20430:四输出迷你电源管理集成电路的卓越性能 在电子设备设计中,电源管理是至关重要的一环,尤其是在对安全性要求极高的应用场景。今天我们来深入了解Analog Devices推出

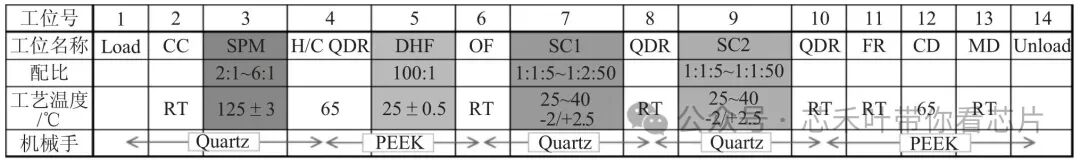

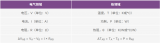

集成电路制造中常用湿法清洗和腐蚀工艺介绍

集成电路湿法工艺是指在集成电路制造过程中,通过化学药液对硅片表面进行处理的一类关键技术,主要包括湿法清洗、化学机械抛光、无应力抛光和电镀四大类。这些工艺贯穿于芯片制造的多个关键环节,直接影响器件

FAN7711 镇流器控制集成电路:设计与应用指南

FAN7711 镇流器控制集成电路:设计与应用指南 引言 在电子照明领域,镇流器控制集成电路起着至关重要的作用。FAN7711 作为一款专为荧光灯设计的镇流器控制集成电路,凭借其独特的性能

功率集成电路应用中的通用热学概念

单芯片功率集成电路的数据手册通常会规定两个电流限值:最大持续电流限值和峰值瞬态电流限值。其中,峰值瞬态电流受集成功率场效应晶体管(FET)的限制,而持续电流限值则受热性能影响。数据手册中给出的持续

PDK在集成电路领域的定义、组成和作用

PDK(Process Design Kit,工艺设计套件)是集成电路设计流程中的重要工具包,它为设计团队提供了与特定制造工艺节点相关的设计信息。PDK 是集成电路设计和制造之间的桥梁,设计团队依赖 PDK 来确保设计能够在晶圆厂的工艺流程中正确制造。

AI芯片,需要ASIC

电子发烧友网报道(文/李弯弯) 2025年,全球AI芯片市场正迎来一场结构性变革。在英伟达GPU占据主导地位的大格局下,ASIC(专用集成电路)凭借针对AI任务的定制化设计,成为推动算力革命的新动力

圣邦微电子推出SGM3807高性能电源管理集成电路

圣邦微电子推出 SGM3807,一款专为 DToF 传感器设计的高性能电源管理集成电路(PMIC)。器件集成了同步降压(Buck)转换器和单电感双输出(SIDO)DC/DC 转换器,且具备卓越的电气

如何进行ASIC集成电路性能优化

如何进行ASIC集成电路性能优化

评论