前言

在使用cadence orcad设计硬件原理图的阶段,为了减少一些重复性的工作,我们可以利用脚本工具进行快捷设计。

本文会教大家如何配置这样的工具,并且分享一个我正在用的小工具,

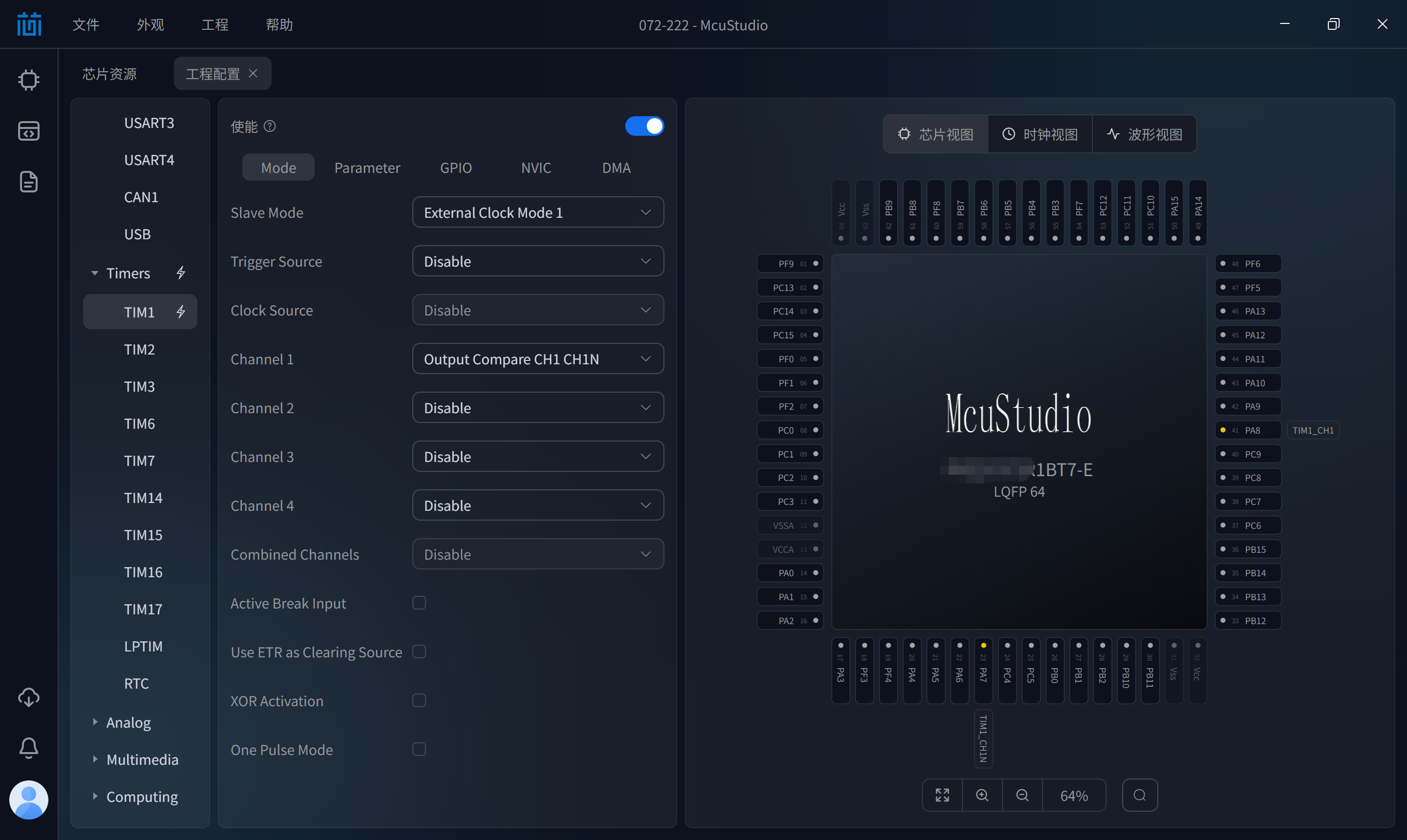

安装方法

1)capEasyCAD.tcl文件放到Cadence安装路径下的【*CadenceSPB_16.6toolscapturetclscriptscapAutoLoad】

2)capsym.olb和EasyCAD 文件文件放到Cadence脚本路径下【CadenceSPB_DATA】

使用方法

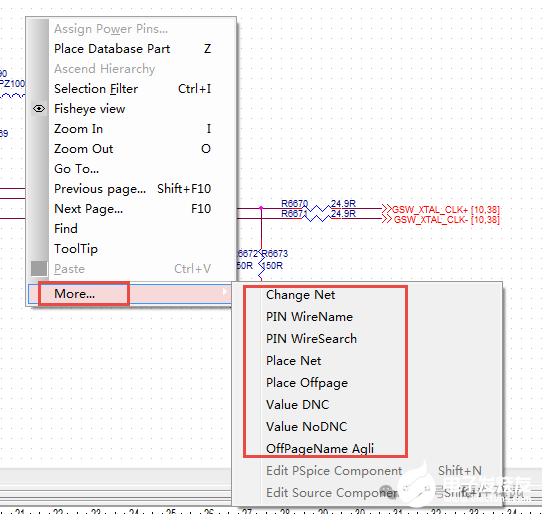

在图纸页面右键可看到当前支持的功能

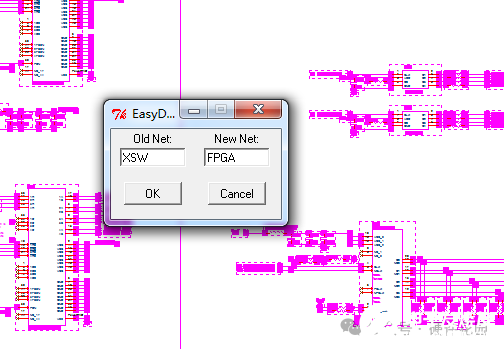

1)【Change Net】--批量修改网络名称

选中需要修改的部分,比如将网络名出现XSW字符全部替换为FPGA,OK后完成替换。

此功能建议慎用!如果使用此功能,修改完成之后需要将原理图关闭并且除DSN以外的文件全部删掉,然后再打开此页并全部选中按回车键打开网络部分。从而完成原理图更新。

2)【PIN WireName】--批量生成pin脚的网络名称

批量选中需要生成网络的pin脚,右键执行【PINWireName】,pin上会自动增加与名称一致的网络。

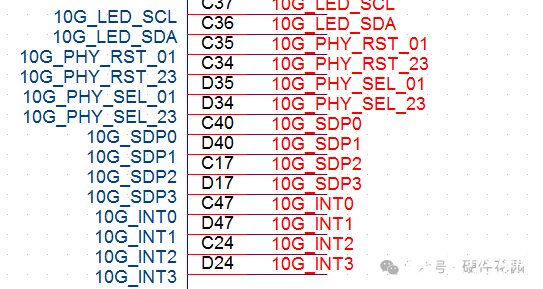

3)【PIN WireSearch】--批量查找生成引脚的网络名称

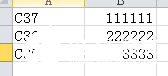

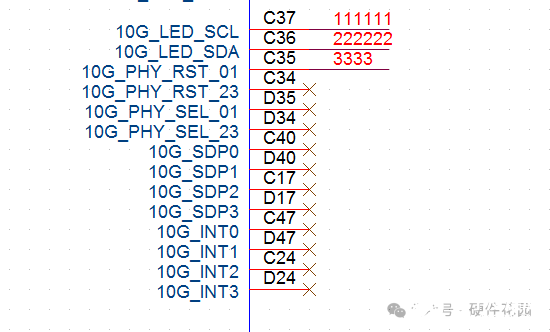

首先制作一个excel表格,比如C37需要生成11111,C36需要生成22222等,制作完成后框选这部分数据,复制!

回到原理图中,批量选中需要生成网络的pin脚,右键执行【PINWireSearch】,pin上会自动查表,并生成对应的网络。

4)【Place Net】--批量生成网络名称

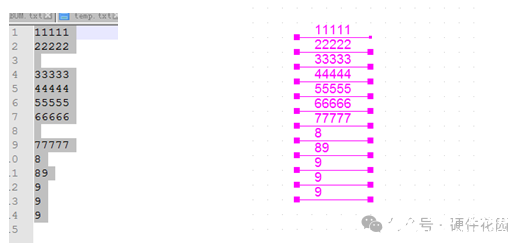

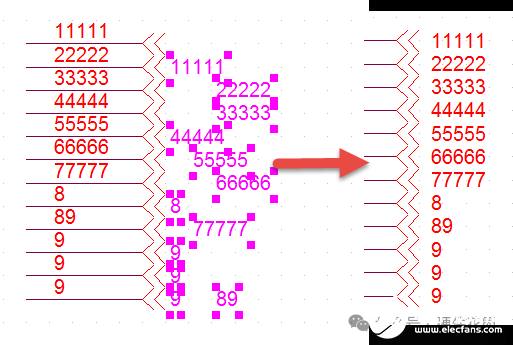

首先制作一个网络名称的列表,可以是excel也可以是txt。框选并复制!

回到原理图中,选择一页左侧有足够空白的图纸,右键执行【Place Net】,可以看到左侧会自动放置网络,待网络消失后,已复制到剪切板,回到需要放置的图页,粘贴网络。

5)【Place Offpage】--批量生成offpage

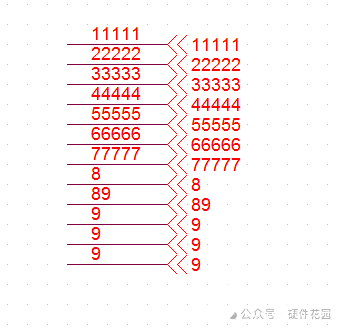

原理图中选中对应的网络线,右键执行【Place Offpage】后会自动生成对应名称的offpage。

如果原理图中选中的是offpage,则会生成与之相反方向的offpage

6)【Value DNC】--将元器件DNC

原理图中选中元器件,可将属性DNC,并保存器件参数保存。与【Value NoDNC】配合使用。

7)【Value NoDNC】--将元器件恢复属性

原理图中选中DNC的元器件,可将DNC之前的属性恢复回来。与【Value DNC】配合使用,手动DNC的无法恢复。

8)【OffPageName Agli】--将offpage的名称对齐

原理图中选中需要对齐的offpage的名称,只能选名称不能选中整个offpage。执行功能,offpage的名称会自动回到原位。如果方向是在左侧,会进行左对齐。

-

原理图

+关注

关注

1356文章

6430浏览量

247334 -

Cadence

+关注

关注

68文章

1029浏览量

147334 -

orcad

+关注

关注

27文章

304浏览量

120579 -

脚本

+关注

关注

1文章

411浏览量

29277

发布评论请先 登录

别再无效加班!IT 运维自动化脚本,砍掉90%重复工作

Claude Code AI编程助手实战指南

告别重复劳动:如何在EASY-EAI-Monster(RK3588)上部署OpenClaw+飞书,为你量身打造“数字员工”

KiCad 10 探秘(一):PCB Design Blocks 来了!原理图与 Layout 完美联动,告别重复布线

MCU工程初始化,到底该不该交给工具?

IBM Rhapsody AI 助手:让系统工程更智能

Cadence电子设计仿真工具标准搭载村田制作所的产品数据

精密平台中重复精度的影响因素有哪些

cadence实用脚本工具分享,实现orcad原理图快捷设计,减少重复性工作

cadence实用脚本工具分享,实现orcad原理图快捷设计,减少重复性工作

评论