易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。

1、ram初始化文件路径是工程路径

在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。

(1)如果文件放在工程目录下,写法如下:

.RAM_INIT_FILE("./ram_init_file.inithex" )

或者.RAM_INIT_FILE("ram_init_file.inithex" )

(2)如在工程目录下新建一个src文件。写法如下:

.RAM_INIT_FILE("./src/ram_int_file.mem")

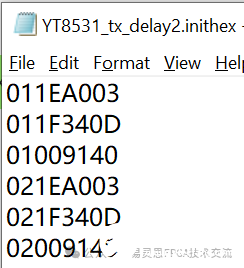

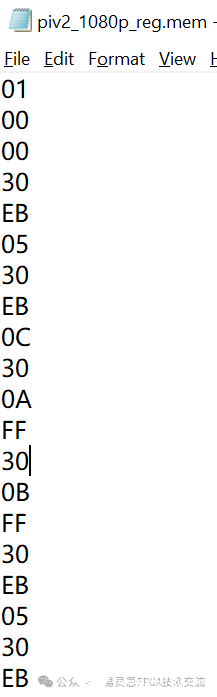

2.初始化文件格式

初始化文件支持.inithex和.mem.都是按顺序以16进制输入数据即可。

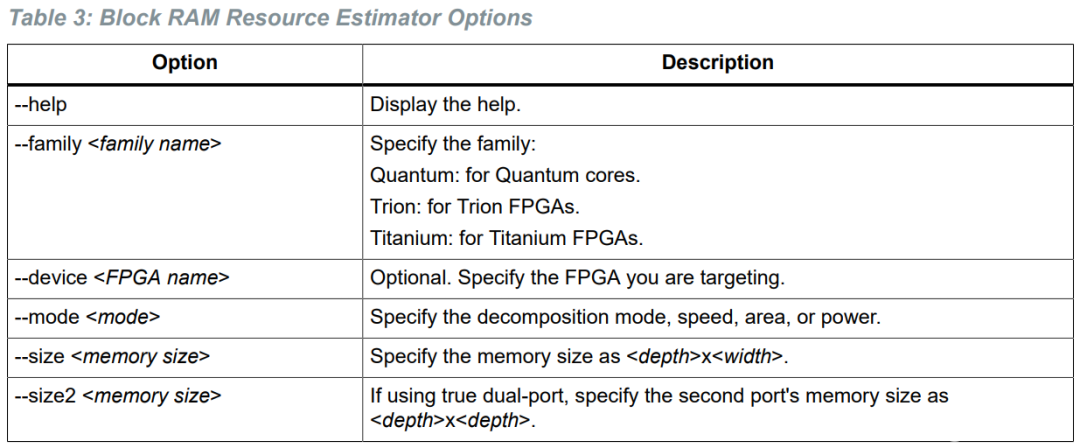

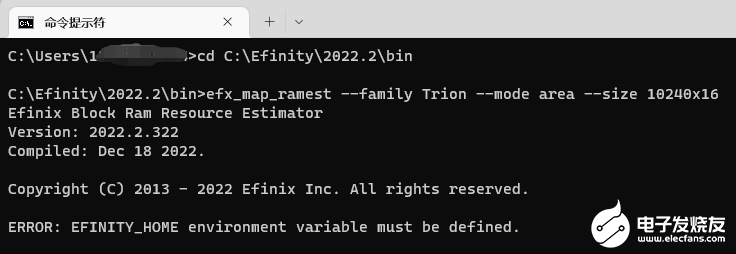

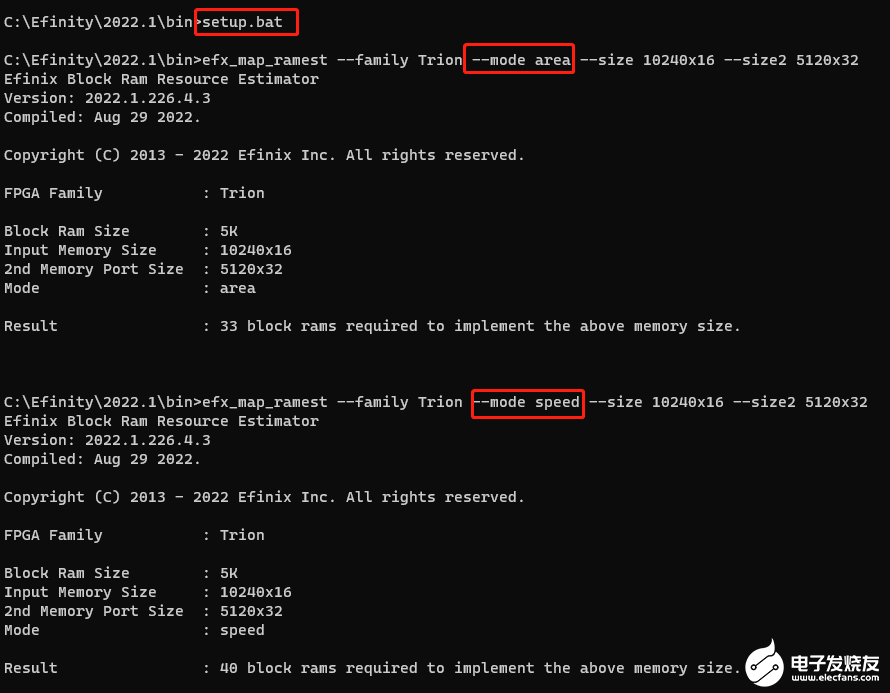

3、在RAM评估器中评估RAM资源

易灵思提供了RAM资源评估器,可以快速帮忙评估RAM资源的使用情况。以下为操作步骤:

(1)把路径转换Efinity路径下的bin文件夹下。

(2)通过以下命令评估

efx_map_ramest --family Trion --mode area --size 10240x16

但是如果直接运行该命令会提示错误。

因为efinity的路径没有写入系统路径,用windows 命令行的时候,需要先运行bin文件夹下的setup.bat来设置环境,然后运行命令,注意不同模式下资源使用量不同。

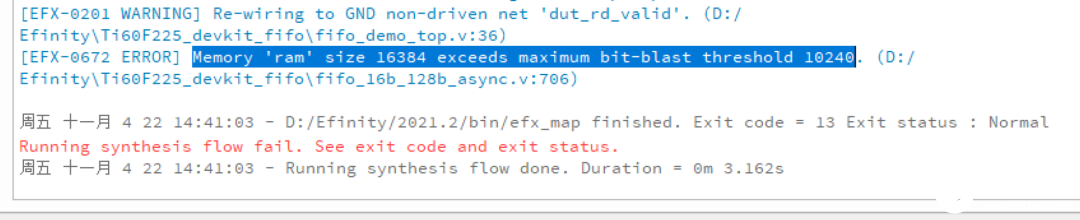

4、大块ram的使用

如果RAM资源使用比较多时,可能会报出以下错误。

解决方案

在工程目录下放置以下文件 文件名:efx_map_settings.ini

并在文件中输入下面语句:max-bit-blast-mem-size = 524300

在2023.1及以后的版本已经不需要上面的ini文件解决方案。

4)RAM使用报错

(1)ERROR: RCLK port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 is constant

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 WCLK port is disabled, but WCLKE is not

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 WCLK port is disabled, but WE is not

ERROR: WDATA[0] port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$12 is not disabled in a disabled mode

ERROR: RCLK port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 is constant

ERROR: EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 WCLK port is disabled, but WE is not

ERROR: WDATA[0] port of EFX_RAM_5K instance u_ddr_rx_buffer/u_wr_fifo/FifoBuff__D$2 is not disabled in a disabled mode

错误原因:FIFO时钟给的是无效的。

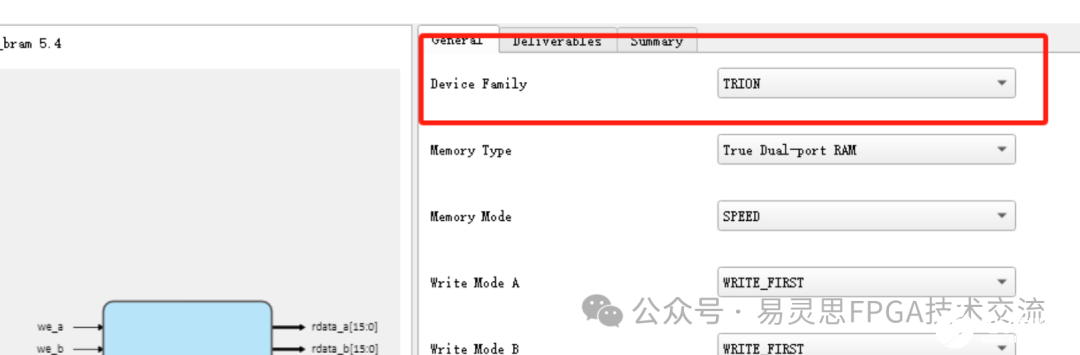

[EFX-0473 ERROR] EFX_DPRAM_5K 'genblkl.dpramsk' illegal instantiation for OPx device. (F:lcvzltestproiectMX efinity proilipltdp ram 16x1024 dlltdp ram 16x1024 d1.y'824)

错误原因:注意器件的family要对应下来。

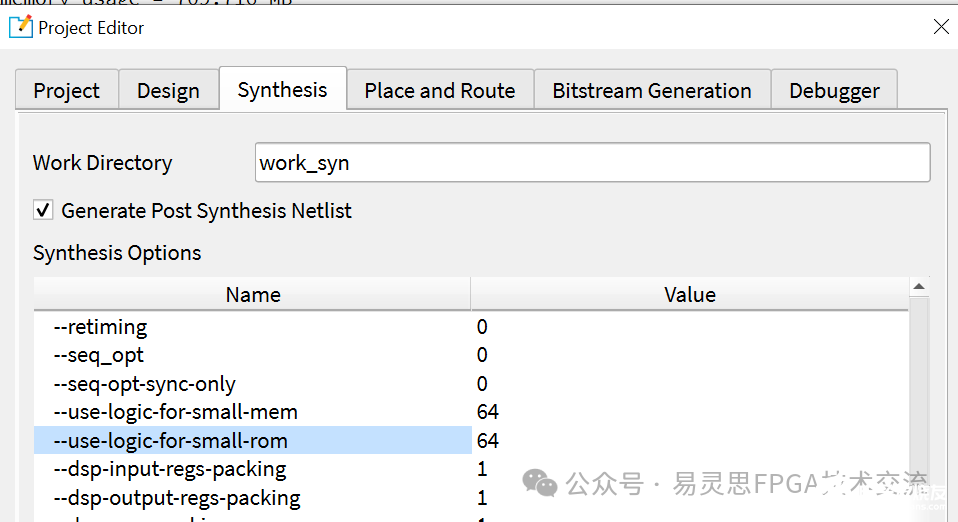

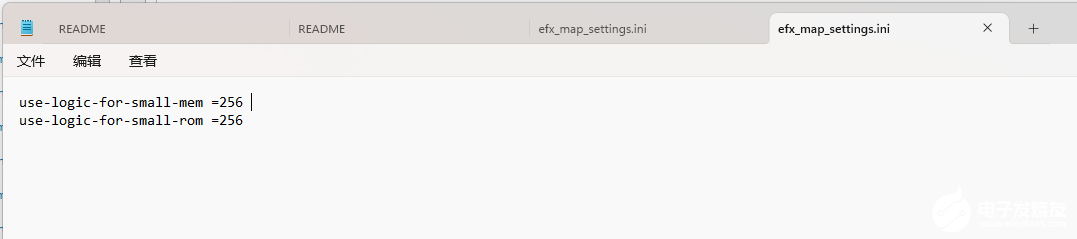

5、如果要把小于256bit的ram综合成register,可以在工程目录下新建一个efx_map_settings.ini文件。并在文件中输入以下两句:

use-logic-for-small-mem=256use-logic-for-small-rom=256

在2023.1及以后的软件提供了相关的选项。

6、RAM综合的其它操作请参考efinity-synthesis.pdf

这里包括对使能,复位等的写法的注意事项。

审核编辑 黄宇

-

RAM

+关注

关注

8文章

1398浏览量

119831 -

易灵思

+关注

关注

6文章

62浏览量

5498

发布评论请先 登录

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

易灵思助力上海集成电路紧缺人才培训项目顺利结课

易灵思2025 FPGA技术研讨会成都站圆满收官

易灵思与思特威第二届机器视觉方案大会圆满收官

睿思芯科灵羽处理器获得国家级权威认可

易灵思与南京大学集成电路学院暑期课程圆满结课

浅谈wsl --update` 命令行选项无效的解决方案

易灵思邀您相约2025上海国际汽车工业展览会

易灵思2025 FPGA技术研讨会北京站圆满结束

国产EDA亿灵思®接入DeepSeek

采用易灵思Ti60F100的Ti60F100I3评估板详解

易灵思RAM使用--Update5

易灵思RAM使用--Update5

评论