共读好书

魏红军 段晋胜

(中国电子科技集团公司第二研究所)

摘要:

论述了 TSV 技术发展面临的设备问题,并重点介绍了深硅刻蚀、 CVD/PVD 沉积、电镀铜填充、晶圆减薄、晶圆键合等几种制约我国 TSV 技术发展的关键设备。

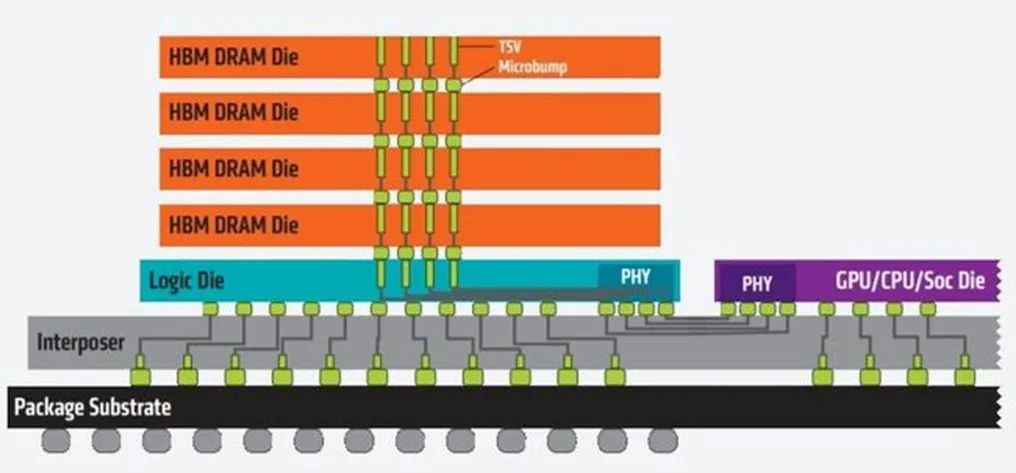

随着半导体技术的发展,特征尺寸已接近物理极限,以往通过减小芯片特征尺寸的方法已无法满足消费类电子产品向更为智能、紧凑及集成化方向发展的需求,基于 TSV 的 3D 封装为业界提供了一种全新的途径,能够使芯片在三维方向堆叠的密度最大,芯片之间的互连线最短,外形尺寸最小,大大改善芯片速度和低功耗的性能。

TSV(through siliconvia) 技术是穿透硅通孔技术的英文缩写,一般简称硅通孔或硅穿孔技术,是 3D 集成电路中堆叠芯片实现互连的一种新的技术解决方案。它是在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,从而实现芯片之间的互连,相对于传统的引线键合(WB)、载带自动焊(TAB)以及倒装芯片(FC),TSV 技术具有的优势:

(1)高密度集成:可以大幅度地提高电子元器件的集成度,减少封装的几何尺寸,满足消费类电子产品对于多功能和小型化的要求;

(2)提高电性能:可以大幅度地缩短电互连的长度,连线长度缩短到芯片厚度,传输距离减少到千分之一,进而降低寄生电容和耗电量;

(3) 实现异质集成:可以把不同的功能芯片(如射频、内存、逻辑、数字和 MEMS 等)集成在一起,实现电子元器件的多功能化;

(4)降低成本:基于 TSV 的 3D 集成技术虽然目前在工艺上的成本较高,但是将来在技术和设备成熟条件下比 2D 封装更具成本效益。基于此,TSV 也被业界称为继引线键合、载带自动焊和倒装芯片之后的第四代互连技术,也被称为终极互连技术。

1 TSV 工艺技术发展面临的设备问题

TSV 技术首先应用于图像传感器,未来还将在逻辑芯片、存储器芯片、CPU 甚至异质集成方面都会得到广泛应用,技术应用领域不断拓展,其发展前景十分光明。可以预知的是,随着 TSV 技术的发展,将会带来新的生产设备群的发展,如深刻蚀设备、铜填充设备、键合机、微检测仪等,同时也意味着大量的传统设备即将淘汰。

通 过 近 几 年 的 发 展 , 国 内 在 深 刻 蚀 、PVD/CVD、晶圆减薄、晶圆键合等设备领域积累了一定经验,并有了一定突破,但与国外最高水平相比还有很大差距。用于 TSV 制程的关键设备依赖少数国外企业,存在成本高、交货周期长、应对市场变化反应较慢的情况。国内设备厂商设备的各项经济技术指标如能达到国外设备同等或更高的水平,将可能被优先采用,市场前景广阔。

2 TSV 制程关键工艺设备

TSV 制作工艺包括以下几步:通孔制作;绝缘层、阻挡层和种子层的沉积;铜填充;通过化学机械抛光去除多余的金属;晶圆减薄;晶圆键合等。每一步工艺都有相当的技术难度,在通孔制作步骤,保持孔的形状和控制角度非常重要,通过Bosch 工艺来实现深孔刻蚀;在沉积绝缘层、阻挡层和种子层时,需要考虑各层的均匀性和粘附性;铜填充时必须避免空洞等缺陷,这样填充的铜可以在叠层器件较高的温度下保持正常的电性能;一旦完成了铜填充,则需要对晶圆进行减薄;最后是进行晶圆键合。

TSV 制作流程会涉及到深刻蚀、PVD、CVD、铜填充、微凸点及 RDL 电镀、清洗、减薄、键合等二十余种设备,其中通孔制作、绝缘层 / 阻挡层 /种子层的沉积、铜填充、晶圆减薄、晶圆键合等工序涉及的设备最为关键,在某种程度上直接决定了 TSV 的性能指标。

2.1 深硅刻蚀设备

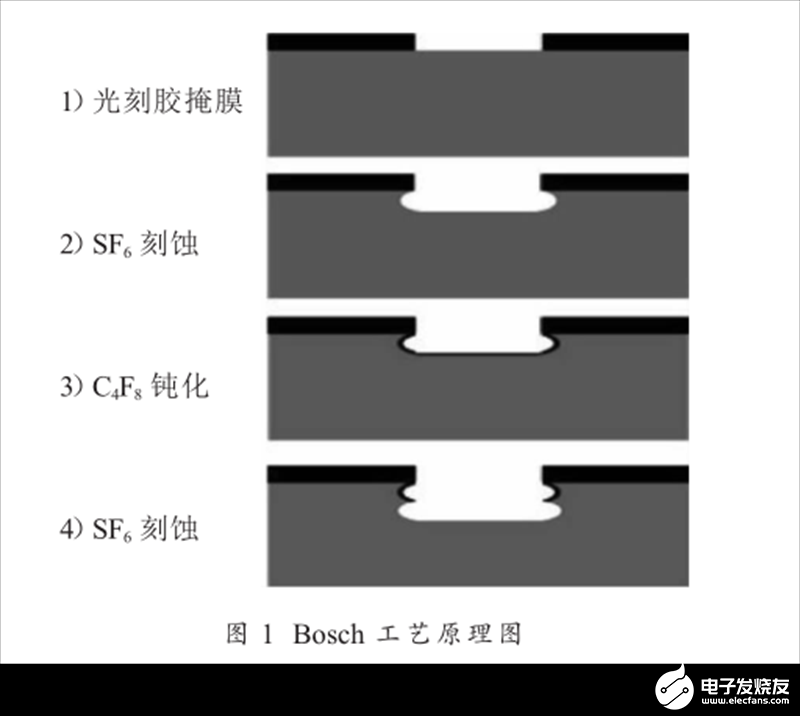

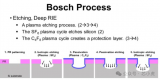

通常情况下,制造硅通孔(经常穿透多层金属和绝缘材料) 采用深反应离子刻蚀技术(DRIE),常用的深硅刻蚀技术又称为“Bosch(博氏)”工艺,有最初发明该项技术的公司命名。

如图 1 所示,一个标准 Bosch 工艺循环包括选择性刻蚀和钝化两个步骤,其中选择性刻蚀过程采用的是 SF 6 和 O 2 两种气体,钝化过程采用的是 C 4 F 8 气体。在 Bosch 工艺过程中,首先利用 SF 6等离子体刻蚀硅衬底,接着利用 C 4 F 8 等离子体作为钝化物沉积在硅衬底上,在这些气体中加入 O 2等离子体,能够有效控制刻蚀速率与选择性。因此,在 Bosch 刻蚀过程中很自然地形成了贝壳状的刻蚀侧壁。

目前深硅刻蚀设备主要由美国应用材料、泛林半导体等设备厂商控制。从国内看,近年来在国家科技重大专项支持下,中微半导体、北方微电子等厂家研制的深硅等离子刻蚀机可以投入硅通孔刻蚀的研发及量产中。尤其 DSE200 系列刻蚀机是北方微电子公司于 2012 年推出的首款深硅等离子刻蚀机,该刻蚀机能实现高达 50:1 的硅高深宽比刻蚀,并同时实现优良的侧壁形貌控制、稳定的均匀性、极高的刻蚀选择比。

2.2 PVD/CVD 沉积设备

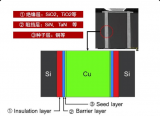

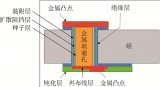

硅通孔形成后,通过等离子体增强化学气相沉积法(PECVD)在硅孔内表面沉积一层绝缘材料 SiO 2 ,工艺温度低,在 100~400℃进行沉积,是TSV 孔绝缘的主流技术之一。今年来ICP-PECVD新型等离子气相增强化学沉积设备被引入进行TSV 孔绝缘层的填充,与常规 PECVD 不同之处在于,其射频功率通过电感耦合至工艺腔室,配合耦合至反应室衬底的射频源可以提高反应离子的方向性,典型的 ICP-PECVD 工艺腔设计如图 2 所示。ICP-PECVD 沉积 SiO 2 的工艺温度低至 20~100 ℃,反应离子浓度高,有助于提高对 TSV 孔的填充效率。

绝缘层做好后,通过物理气相沉积法(PVD)沉积金属扩散阻挡层和种子层,为后续的铜填充做好准备。如果填充材料为多晶硅或者钨,则不需要种子层。

后续的电镀铜填充要求 TSV 侧壁和底部具有连续的阻挡层和种子层。种子层的连续性和均匀性被认为是 TSV 铜填充最重要的影响因素。根据硅通孔的形状、深宽比及沉积方法不同,种子层的特点也各有不同,种子层沉积的厚度、均匀性和粘合强度是很重要的指标。

2.3 电镀铜填充设备

很多成本模型显示,TSV 填充工艺是整个工艺流程中最昂贵的步骤之一。TSV 的主要成品率损耗之一是未填满的空洞。电镀铜工艺作为最合适的硅通孔填充技术受到业内的普遍关注,其关键技术在于 TSV 高深宽比(通常大于 10:1)通孔的全填充电镀技术。

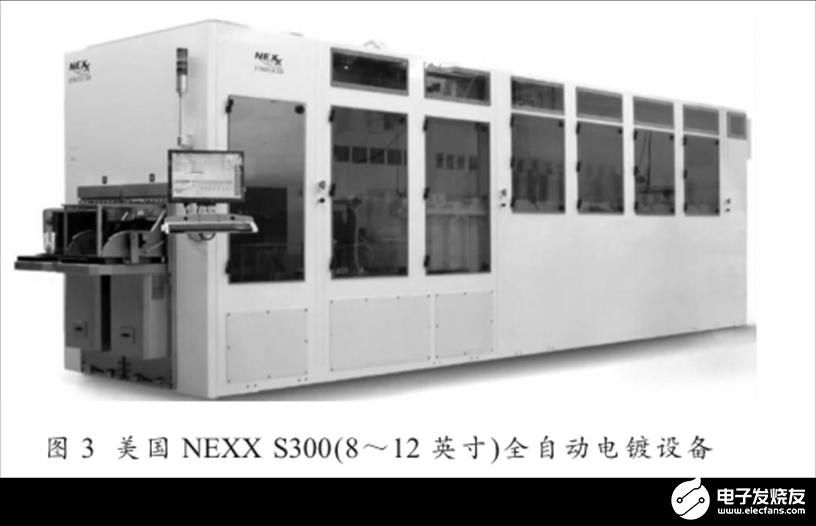

国外有诸多公司已经成功研发该项目技术并已形成成熟产品,包括 NEXX、TECHNIC、Semitool等公司。尤其是美国 NEXX 公司是先进封装领域的专用设备供应商,其中 Stratus S200 (4~8 英寸)、S300(8~12 英寸)全自动电镀设备已应用于全球各大封装厂家的 12 英寸及以下规格的晶圆量产生产中,可用于 TSV、凸点、UBM、RDL、铜互连等制程。见图 3。

NEXX 公司系列电镀设备销往全球,其中亚洲封测厂家占 75%。据了解国内封装龙头企业长电、富士通等的产线上都在使用 Stratus 系列设备。该系列设备采用剪切电镀方式,具有镀层均匀、结构紧凑、易于扩展等优点,为封测厂家提供了质量稳定、生产效率高、占地小的一款自动设备。

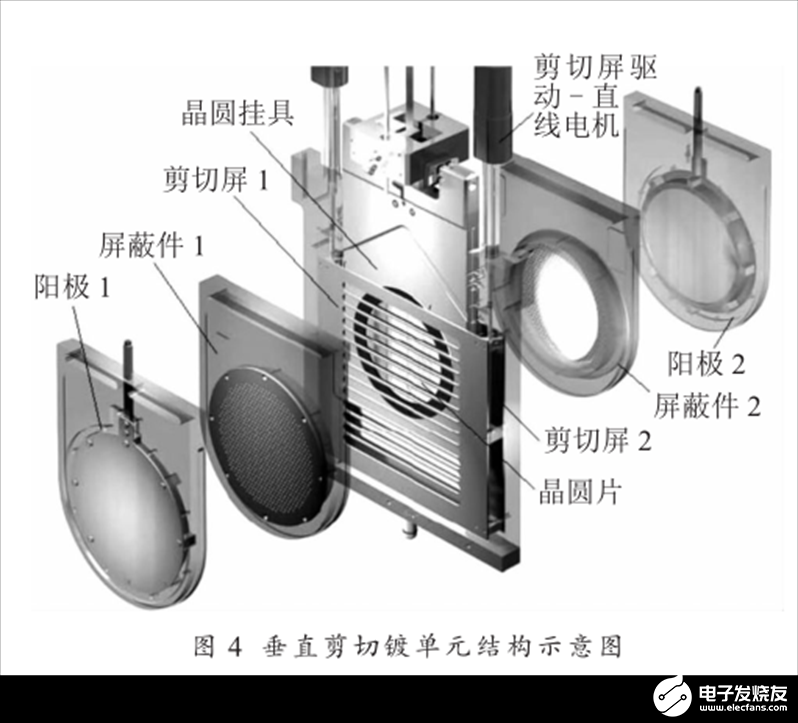

垂直剪切镀单元作为该设备的核心部分(见图 4),主要包括阳极、屏蔽件、晶圆夹具、剪切屏及驱动电机等。整体单元框架上分别布置以上各件的安装导槽、提高镀层均匀性的剪切屏、直流导电夹紧机构。各个部件主体均采用氟塑料材质板,单元整体为用螺栓、密封件将各个部件连接组合。

目前国内研究机构在 TSV 单项技术上取得一些研究结果,但是对于电镀相关工艺设备几乎并无厂家涉及,只有中国电子科技集团公司第二研究所在进行 TSV 铜填充工艺技术的研究,并有相关实验设备交付客户使用。

2.4 晶圆减薄设备

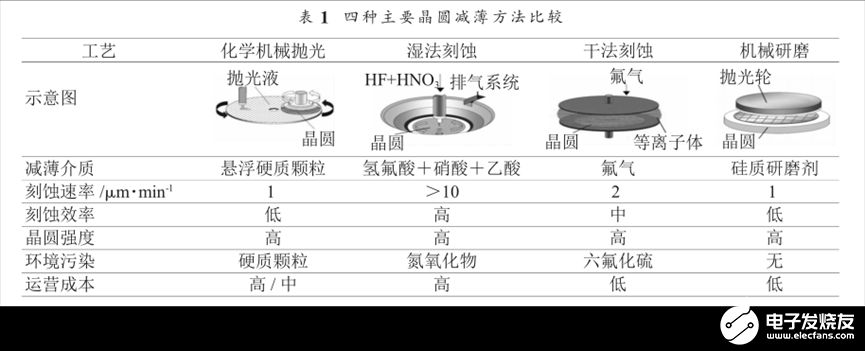

TSV 要求晶圆减薄至 50 μm 甚至更薄,要使硅孔底部的铜暴露出来,为下一步的互连做准备。目前晶圆减薄可以通过机械研磨、化学机械抛光、湿法及干法化学处理等不同的加工工序来实现,通过它们之间有机的结合,并优化这几道工序的比例关系,保证晶圆既能减薄到要求的厚度,又要有足够的强度。目前四种主要晶圆减薄方法对比见表 1。

在要求<50 μm 这个厚度上,晶圆很难容忍减薄过程中的磨削对晶圆的损伤及内在应力,其刚性也难以使晶圆保持原有的平整状态,同时后续工艺的晶圆传递、搬送也遇到了很大的问题。目前业界的主流解决方案是采用一体机的思路,将晶圆的磨削、抛光、保护膜去除、划片膜粘贴等工序集合在一台设备内,晶圆从磨片一直到粘贴划片膜为止始终被吸在真空吸盘上,始终保持平整状态,从而解决了搬送的难题。

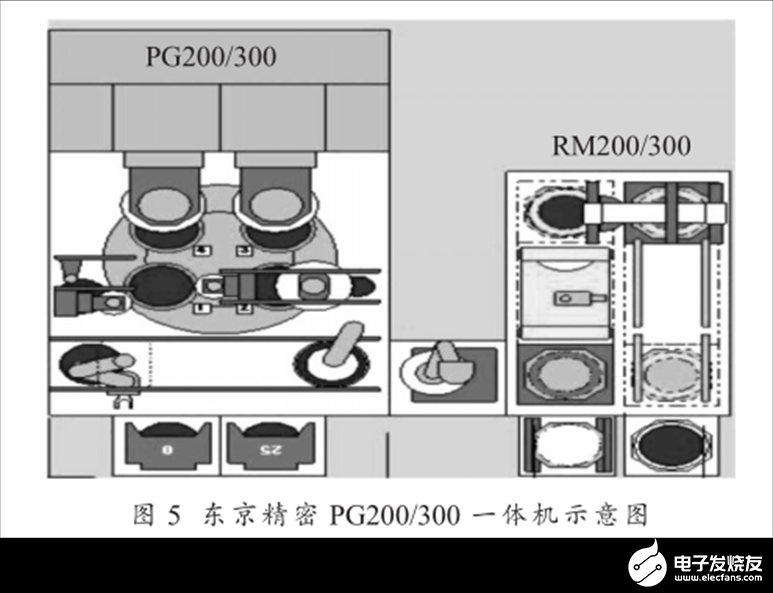

图 5 是东京精密公司的一体机PG200/300 的基本配置示意图。图中 PG 部分是磨片和抛光的集成体。通过一个带有 4 个真空吸盘的大圆盘回转台 360°顺时针旋转,使晶圆在不用离开真空吸盘的情况下就可以依次送到粗磨、精磨、抛光等不同的加工工位,完成整个减薄过程。

减薄好的晶圆从 PG 处转移到 RM 处,它是通过一个多孔陶瓷吸盘来完成。RM 部分主要是完成保护膜的去除和划片膜的粘贴。由于保护膜的剥离需要在晶圆的正面动作,所以必须将晶圆进行反转。由于晶圆厚度很薄,翻转难度很大。东京精密公司把传统剥膜工艺的后续工艺—— — 贴膜工艺前移,利用划片膜粘贴到框架上所具有的平整性和张力来给晶圆提供支撑,从而解决这一问题。

2.5 晶圆键合设备

晶圆键合最初是为 MEMS 制造工艺而开发,主要作为晶圆级覆盖技术。现在晶圆键合不仅用于覆盖 MEMS 晶圆,而且也用于堆叠具有不同功能的晶圆,通过 TSV 实现晶圆的 3D 堆叠。

目前晶圆键合主要有直接氧化物键合、阳极键合、粘接键合、基于焊料的键合、金属 - 金属直接键合、超声键合、玻璃介质键合等等。但是,因为CMOS 器件热预算的缘故,与 TSV 互连的 CMOS晶圆兼容的键合工艺仅仅局限于直接氧化物键合、金属键合(Cu-Cu 或 Cu-Sn-Cu)、粘接键合和这几种方法的组合。其中 Cu-Cu 直接键合与其它键合方法对比有种种优点:电阻率较低、抗 EM 较好、互连 RC 延迟减少,可以同时实现机械和电学的接触界面。

不过,可靠地 Cu-Cu 键合对于大多数应用仅从高温、高压和长工艺时间产生,主要是因为它有形成自然氧化物的倾向,对器件可靠性有不利影响。现在,工艺温度高是 Cu-Cu 直接键合的主要瓶颈之一,因为它给器件可靠性及制造良率产生负面影响。另外,高温下对晶圆之间的对准精度也产生了不利影响。

基于此,领先地晶圆键合设备供应商奥地利EVG 公司开发了光学对准、低温 Cu-Cu 热压键合工艺,对准精度达到了亚微米。

3 结束语

据 Yole 预测,从 2014 年到 2020 年,TSV 的年增长率会达到48%,可以预见 TSV 市场孕育巨大商机,相关的设备及材料市场面临爆发式增长机会。在此情况下,我们必须科学分析、冷静面对TSV 技术发展带来的历史机遇,制定科学的发展规划,加大 TSV 关键工艺设备的投入力度,抓住半导体先进封装技术发展的新机遇。

审核编辑 黄宇

-

芯片

+关注

关注

462文章

53534浏览量

459098 -

封装

+关注

关注

128文章

9139浏览量

147889 -

TSV

+关注

关注

4文章

136浏览量

82380

发布评论请先 登录

在电子制造的高精度领域中,芯片引脚的处理工艺

TSV技术的关键工艺和应用领域

基于TSV的减薄技术解析

TSV以及博世工艺介绍

基于TSV的3D-IC关键集成技术

半导体新建项目洁净室工艺设备泊苏防微振平台施工流程

TSV三维堆叠芯片的可靠性问题

先进封装中的TSV/硅通孔技术介绍

TSV 制程关键工艺设备技术及发展

TSV 制程关键工艺设备技术及发展

评论