什么是TSV

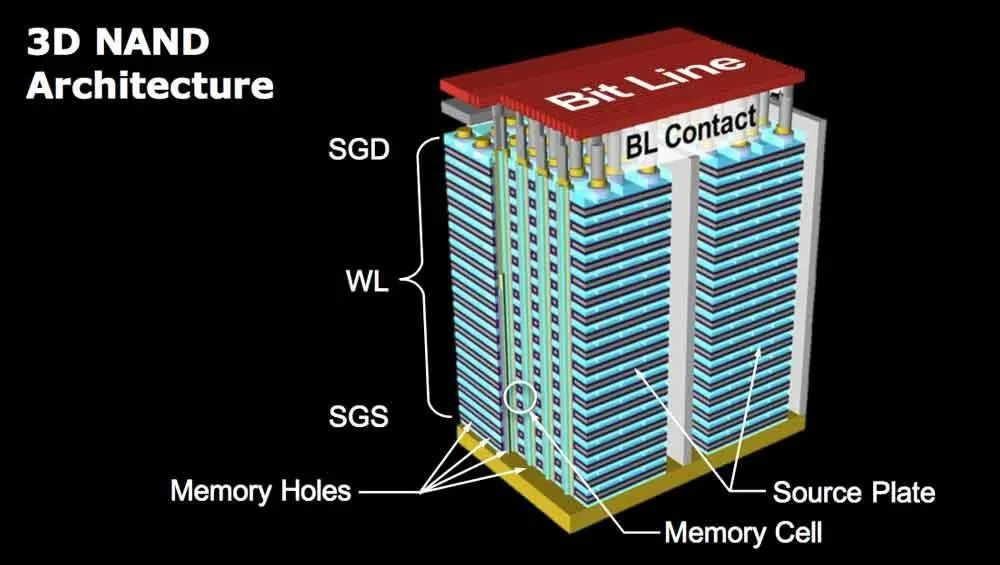

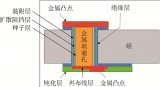

TSV(Through-Silicon Via)是一种先进的三维集成电路封装技术。它通过在芯片上穿孔并填充导电材料,实现芯片内、芯片间以及芯片与封装之间的垂直连接。TSV 技术可以将不同功能的芯片堆叠在一起,从而提高集成度、降低功耗,并缩小芯片封装的体积。TSV 技术被广泛应用于各种领域,如微处理器、存储器、传感器等,是推动集成电路制造技术向三维方向发展的重要技术之一。

1

TSV制造关键工艺流程

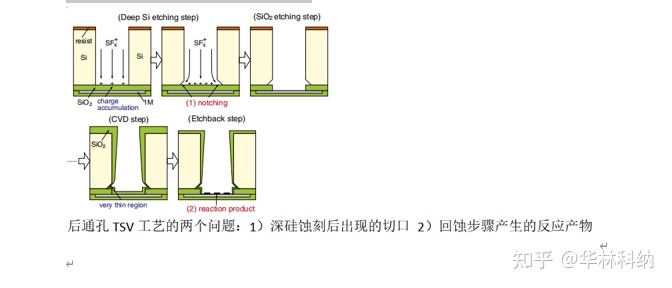

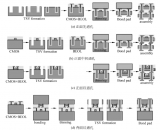

TSV制造的主要工艺流程依次为:深反应离子刻蚀(DRIE)法行成通孔,使用化学沉积的方法沉积制作绝缘层、使用物理气相沉积的方法沉积制作阻挡层和种子层。选择一种电镀方法在盲孔中进行铜填充,使用化学和机械抛光(CMP)法去除多余的铜。而一旦完成了铜填充,则需要对晶圆进行减薄,最后是进行晶圆键合整体工艺路线会根据特定需求对典型工艺进行变动。

2

TSV关键工艺设备及特点

对应TSV生产流程会涉及到深孔刻蚀,PVD、 CVD、铜填充、微凸点及电镀、清洗、减薄、键合等二十余种设备,其中深孔刻蚀、气相沉积、铜填充、CMP去除多余的金属、晶圆减薄、晶圆键合等工序涉及的设备最为关键。

①深孔刻蚀设备

深孔刻蚀是TSV的关键工艺,目前首选技术是基于Bosch工艺的干法刻蚀。深反应等离子刻蚀设备就是感应耦合高密度等离子体干法刻蚀机(Inductively Coupled Plasma Etcher),它采用半导体刻蚀机的成熟技术,独特设计的双等离子体源,实现了对腔室内等离子体密度的均匀控制,满足硅高深宽比刻蚀工艺的要求。具有稳定可靠的工艺性能、宽阔的工艺窗口和良好的工艺兼容性,用于晶片的高深宽比刻蚀。

②气相沉积设备

气相沉积设备主要用于薄膜电路表面的高低频低应力氧化硅等薄膜淀积。设备具有低温TEOS工艺沉积氧化硅薄膜,应力易调控,适用于薄膜电路制造中保护膜层的沉积。设备应具有预真空室、基片传送模块以及工艺模块等,传片及工艺过程自动化。

绝缘层做好后,通过物理气相沉积法(PVD)沉积金属扩散阻挡层和种子层,为后续的铜填充做好准备。后续的电镀铜填充要求TSV侧壁和底部具有连续的阻挡层和种子层。种子层的连续性和均匀性被认为是TSV铜填充最重要的影响因素。根据硅通孔的形状、深宽比及沉积方法不同,种子层的特点也各有不同,种子层沉积的厚度、均匀性和粘合强度是很重要的指标。

③铜填充设备

深孔金属化电镀设备用于新一代高频组件高深宽比通孔填孔电镀铜工艺,解决高深宽比微孔内的金属化问题,提高互联孔的可靠性。TSV填孔镀铜工序是整个TSV工艺里最核心、难度最大的工艺对设备的要求比较高,成熟的用于TSV填孔镀铜的设备价格昂贵。

④减薄抛光设备

一旦完成了铜填充则需要对晶圆进行减薄抛光。TSV要求晶圆减薄至50μm甚至更薄,要使硅孔底部的铜暴露出来,为下一步的互连做准备。目前晶圆减薄可以通过机械研磨、化学机械抛光、湿法及干法化学处理等不同的加工工序来实现。但晶圆很难容忍减薄过程中的磨削应力,其刚性也难以使晶圆保持原有的平整状态,同时后续工艺的晶圆传递、搬送也遇到了很大的问题。目前业界多采用一体机的思路,将晶圆的磨削、抛光、贴片等工序集合在一台设备内。

3

TSV的应用和优势

TSV的应用之一是,它允许将由不同部分组成的复杂处理器分离在几个不同的芯片上,并具有以下附加优点:垂直连接允许更多数量的连接,这有助于实现更大的带宽,而无需额外的带宽,很高的时钟频率会增加数据传输期间的功耗。

例如,在将来我们将看到CPU和GPU的最后一级缓存将不在芯片上,它们具有相同的带宽,但存储容量却是原来的几倍,这将大大提高性能。我们也有使用FSV来通信Lakefield SoC的两个部分的Intel Foveros示例,带有系统I / O所在的基本芯片的计算芯片。

将处理器划分为不同部分的原因是,随着芯片的变大,电路中错误的可能性越来越大,因此没有故障的优质芯片的数量会增加。他们可以使用的更少,而那些做得好的人必须支付失败者的费用。这意味着从理论上减小芯片的尺寸会降低总体成本,尽管稍后我们将看到情况并非完全如此。

第二个应用程序与占用的空间有关,能够垂直堆叠多个芯片的事实大大减少了它们占用的面积,因为它们不会散布在板上,其中最著名的示例是将HBM内存用作某些图形处理器的VRAM,但是我们还有其他示例,例如三星的V-NAND存储器,将多个NAND闪存芯片彼此堆叠。

其他鲜为人知的选择是逻辑和内存的组合,其中内存位于处理器的顶部,最著名的示例是宽I / O内存,这是几年前出现在智能手机中的一种内存,包括SoC顶部的存储器通过硅互连。

2022年3月9号,苹果公司推出的M1 ULTRA处理器,这款性能爆表的处理器中,多个CPU使用带TSV的Silicon interposer进行集成的。如今,无论是AI/AR/VR中用到的传感器,图像传感器,堆叠存储芯片以及高性能处理器,都越来越离不开TSV。

TSV这项并不为人熟知的技术,正在硬件的底层深深的影响着人类的生产生活方式。

审核编辑:刘清

-

集成电路

+关注

关注

5446文章

12465浏览量

372675 -

晶圆

+关注

关注

53文章

5344浏览量

131685 -

图像传感器

+关注

关注

68文章

2051浏览量

131915 -

芯片封装

+关注

关注

13文章

604浏览量

32080 -

TSV技术

+关注

关注

0文章

17浏览量

5777

原文标题:工程师必备 | 一文解锁TSV 制程工艺及技术

文章出处:【微信号:MDD辰达行电子,微信公众号:MDD辰达半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

TSV工艺流程与电学特性研究

一文看懂TSV技术

一文详解硅通孔技术(TSV)

半导体工艺几种工艺制程介绍

TSV关键工艺设备及特点

TSV的工艺流程和关键技术综述

TSV 制程关键工艺设备技术及发展

TSV以及博世工艺介绍

一文解锁TSV制程工艺及技术

一文解锁TSV制程工艺及技术

评论