云天半导体突破2.5D高密度玻璃中介层技术

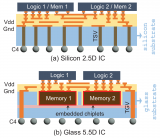

随着人工智能的兴起,2.5D中介层转接板作为先进封装集成的关键技术,近年来得到迅猛发展。与硅基相比,玻璃基(TGV)具有优良的高频电学、力学性能、工艺流程简化和成本低等优势,并能实现光电合封,是理想的芯粒三维集成解决方案。

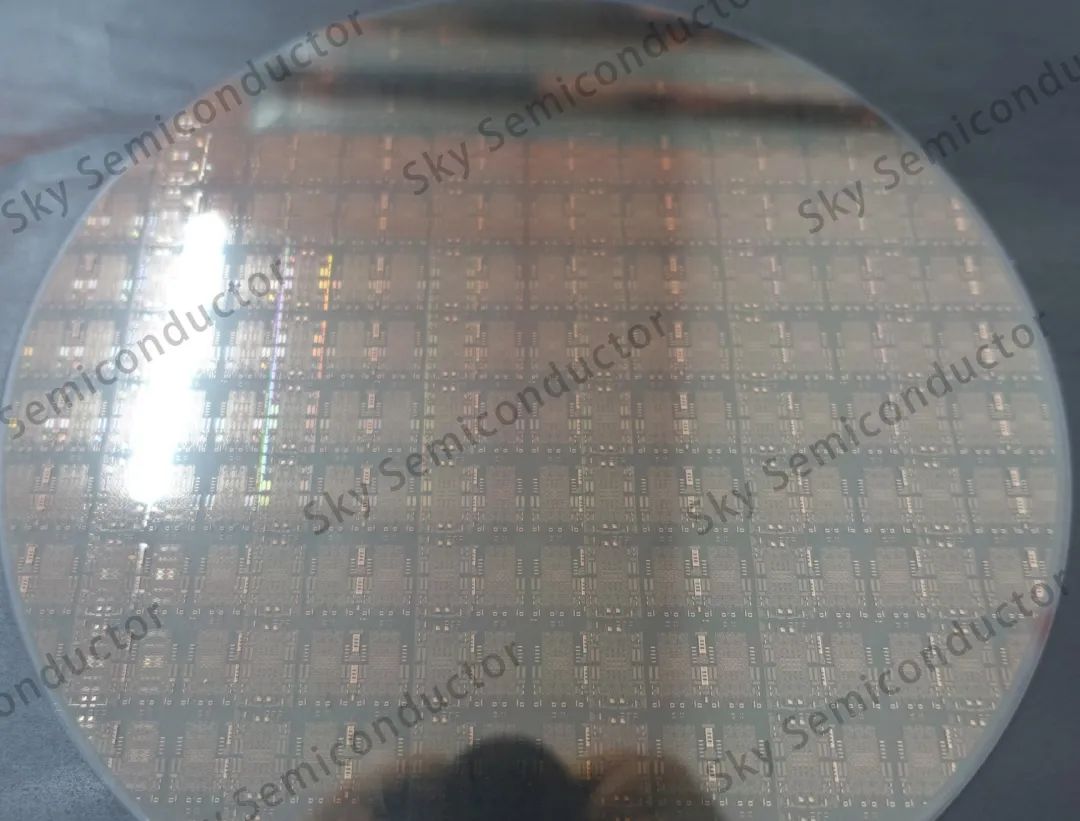

图1 封装面积为2700mm2的TGV转接板

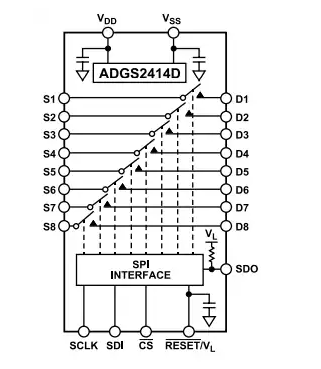

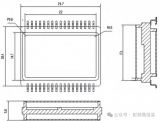

近年来,厦门云天半导体科技有限公司致力于研发玻璃通孔及其集成技术,开发了高精度、高深宽比玻璃孔制备技术、高性能玻璃基IPD技术,并实现了规模化量产。面向高性能芯粒集成需求,云天半导体成功研发了高密度玻璃转接板技术。大尺寸TGV转接板样品如图1所示,该玻璃转接板面积为2700mm2(60mm×45mm),厚度为80μm,TGV开口直径25μm,实现8:1高深宽比的TGV盲孔无孔洞填充。金属布线采用无机薄膜介质材料,实现3层RDL堆叠,通过调试干法刻蚀参数、优化CMP抛光能力实现细间距RDL,其中最小L/S可达1.5/1.5μm(如图2)。并通过多场reticle拼接技术可满足大尺寸转接板制备,其中拼接精度可控在100nm以内(如图3)。电性测试结果表明基于玻璃基的无机RDL结构较有机RDL损耗降低10%。

图2 多层RDL堆叠晶圆

图3 细长RDL拼接

基于玻璃基板的综合性能以及近期Intel发布的未来发展规划,业界高度重视玻璃基板技术发展和产品应用。云天半导体的高密度玻璃中介层技术未来将助力AI等应用的CPU、GPU产品的先进封装。

云天半导体

-

半导体

+关注

关注

339文章

31248浏览量

266601 -

人工智能

+关注

关注

1820文章

50335浏览量

266974 -

CMP

+关注

关注

7文章

162浏览量

27902

原文标题:云天半导体突破2.5D高密度玻璃中介层技术

文章出处:【微信号:today_semicon,微信公众号:今日半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高密度配线架面板

高密度叠层母排 (Laminated Busbar) 杂散电感优化指南

MPO分支光缆:高密度光纤布线的核心组件

2D、2.5D与3D封装技术的区别与应用解析

Kioxia研发核心技术,助力高密度低功耗3D DRAM的实际应用

EMI滤波高密度D-Sub连接器技术解析与应用指南

哪种工艺更适合高密度PCB?

TGV产业发展:玻璃通孔技术如何突破力学瓶颈?

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

Analog Devices Inc. ADGS2414D高密度开关数据手册

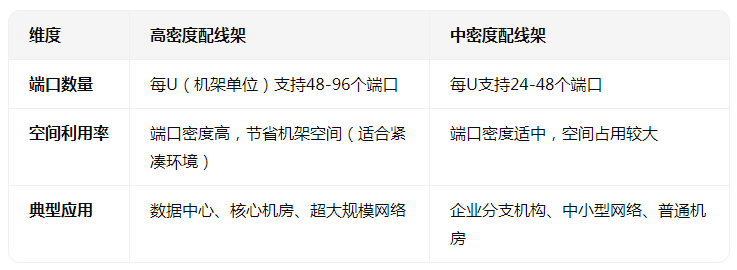

高密度配线架和中密度的区别

基于叠层组装和双腔体结构的高密度集成技术

云天半导体突破2.5D高密度玻璃中介层技术

云天半导体突破2.5D高密度玻璃中介层技术

评论