本文转发连云港杰瑞电子有限公司的臧艳丽等发表在《电子工艺技术》上的“基于叠层组装和双腔体结构的高密度集成技术”,文中基于芯片堆叠和多层HTCC管壳开发了一款产品,在此予以介绍,供大家学习。

01双腔产品结构设计

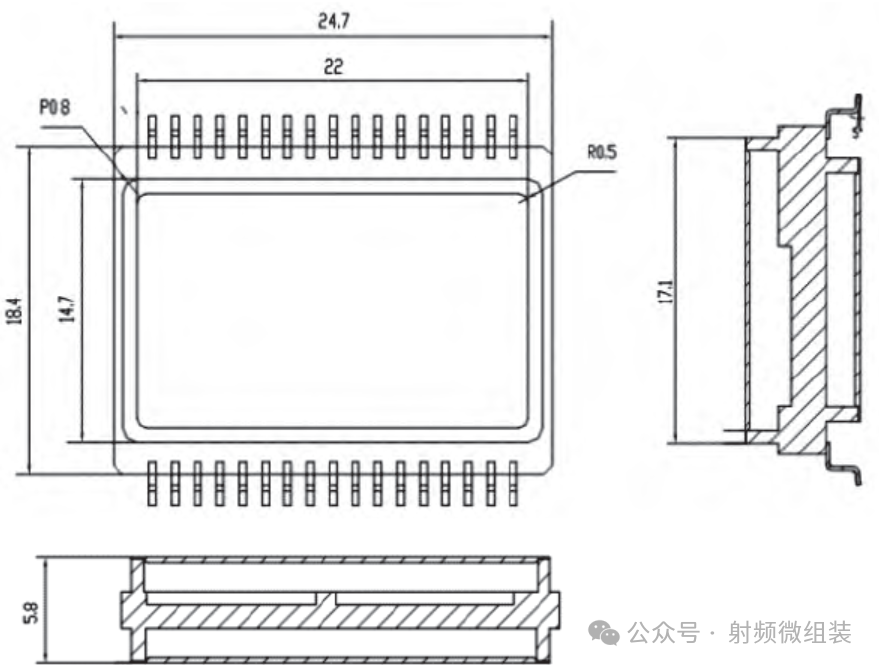

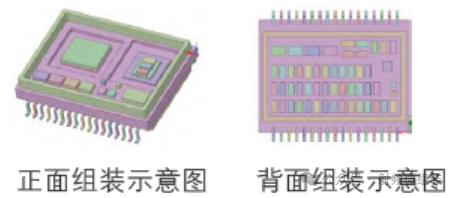

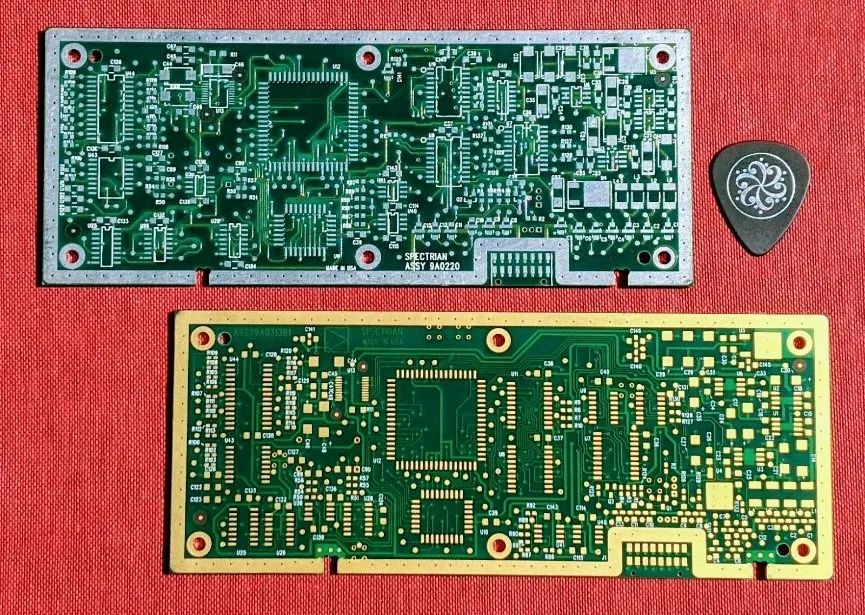

产品集成11颗芯片,58个无源元件,采用双面陶瓷管壳作为载体,进行双层芯片叠装和组装,实现高密度集成。壳体工艺采用高温多层陶瓷共烧工艺,可以最大限度地增加布线密度和缩短互连线长度,从而提高组件密度和信号传输速度。如下图所示,腔体内部设计两层深腔,留有多层芯片叠装的立体组装空间,设计两层台阶键合区域,便于空间键合走线实现电气连接。陶瓷基板上设计电路,通过金丝键合实现电气互连。双面组装完成后进行双面平行封焊,最后进行引脚成型。

02关键工艺技术

1)三维芯片堆叠技术

芯片堆叠结构有三种典型的叠装方式:1)小芯片叠装大芯片的金字塔式;2)芯片两侧出键合线的十字交叉式;3)同尺寸的芯片通过垫片叠装的悬臂梁式。前两种芯片堆叠方式难度不大,本部分重点分析悬臂梁式芯片叠装。

该技术难点主要有三个:1)芯片与垫片粘接、芯片与芯片粘接材料的选择,既要具有较高粘接强度又要具有缓冲结构应力的能力,以适应芯片叠装的应用;2)控制芯片与芯片间粘接胶量,避免溢出胶污染到键合区,需要采用自动粘接设备;3)空间键合难度大,叠层芯片组装的垂直空间极为有限,因此要求键合线必须具有尽可能低的弧高,采用反向键合的工艺方法,适当的时候使用等离子清洗避免洇胶影响键合质量。

2)一体化双面腔体组装技术

该技术可实现高密度模块的组装,双面安装元器件,实现立体组装,较单腔模块体积可缩小1/3以上,双面腔体密封,耐环境应力可靠性高。该技术主要有两个工艺难点:1)双面腔体元器件的粘接、键合工艺;2)双面腔体封焊技术。封焊技术目前有激光封焊、平行缝焊、真空熔焊等,根据所选择的工艺和腔体材料的不同,选择合适的封焊技术。

3)后引脚成型技术

引脚作为电气连接和结构支撑的用途,设计类似芯片小外形封装,两侧出引脚数量34根,引脚材料采用柯伐合金材料。产品通过引脚与印制板实现电气连接,整个大腔体依靠引脚支撑存在风险,设计增加背面腔体也起到结构支撑作用。如果采用背面同步焊接的方式,引脚成型过程需要确保引脚底面与底层腔体盖板面共平面,需要定制专门的工装,背面腔与引脚的共面性要求高度差小于0.1 mm,这对引脚成型过程的控制要求更高。另一种方式采用侧面打胶加固,此方法对引脚底面和底层腔体的共面性要求不高,引脚成型工艺更容易实现。

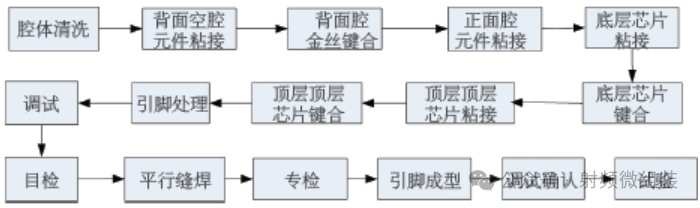

03芯片叠层和双腔体工艺设计

1)客户使用工艺性设计

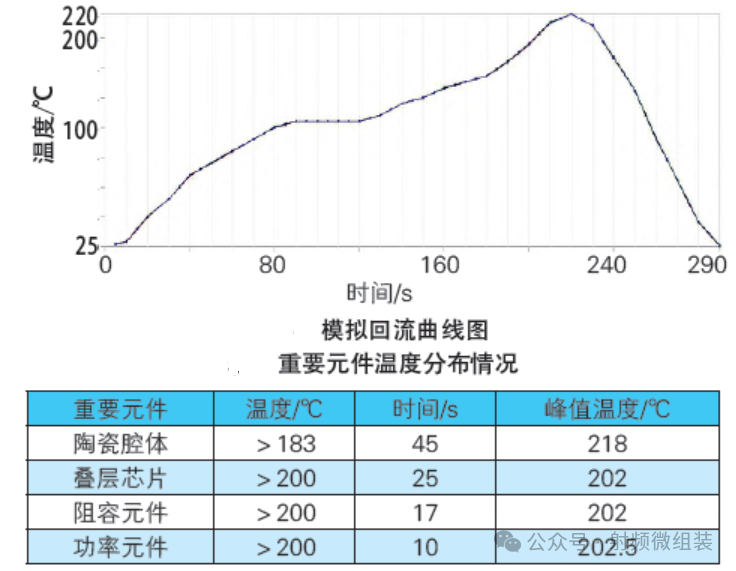

客户使用的是采用贴装的方式将转换器组装到印制板上,通过34根引脚与印制板实现电气连接,背面盖板表面镀镍,通过Sn63Pb37与印制板表面焊接固定,焊料共晶温度点183 ℃,侧面点胶加固,背面盖板和引脚同时起固定支撑作用。

模拟回流焊接曲线如下图所示,经过回流焊接过程各重要器件温度分布情况见下表。

通过温度分布结果显示:芯片、元器件超过200 ℃的时间均控制在25 s以内,双腔体封装后的产品经过回流焊接,温度分布对元器件影响不大,产品元件的可耐受峰值温度和时间可控。

2)可靠性预测分析

高密度集成封装中,芯片叠层技术是封装中的薄弱点,因为芯片、垫片、陶瓷管壳三种材料热膨胀系数存在差异,硅芯片又属于脆性材料,粘接材料的选择是提高芯片堆叠可靠性的基础,通过查阅相关文献,选择低应力粘接材料,匹配真实的产品数据进行了温度冲击、机械冲击、恒定加速度模拟分析,可靠性试验模拟结果见下表。通过预测模拟分析结果显示:1)在经受-65~150 ℃温度循环试验时,每种材料由于收缩程度不一致,芯片叠装结构内部会产生内应力,2层芯片堆叠结构的最大应力100MPa,硅的破坏强度较高,在5~10GPa,实际损坏强度远低于理论强度,只有30%~70%,,按照30%的破坏强度,受到的应力依然是小于芯片材料的强度值,不会出现芯片开裂的问题,芯片翘曲变形最大是在最顶层,变形量最小是在最底层。

2)机械冲击条件1500g ,0.5ms的条件作用于模型结构,芯片受到最大等效应力5.83MPa小于Si芯片的损坏强度;恒定加速度5000g ,Y2方向时间1min,芯片受到的等效最大应力5.57MPa远小于芯片的损坏强度,芯片间的绝缘胶在机械冲击和恒定加速度条件下,对芯片有缓冲作用,芯片受到的应力远小于芯片的破坏强度。

基于真实的产品数据进行了温度冲击、随机振动、恒定加速度模拟分析,结果证明该产品的低应力粘接胶和结构能够满足产品的使用要求。

-

芯片

+关注

关注

462文章

53534浏览量

458953 -

无源元件

+关注

关注

1文章

1293浏览量

17401 -

芯片堆叠

+关注

关注

0文章

19浏览量

14837 -

陶瓷基板

+关注

关注

5文章

261浏览量

12317

原文标题:基于叠层组装和双腔体结构的高密度集成技术

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

器件高密度BGA封装设计

高密度印制电路板(HDI)简介

高密度电路板的塞孔制程

探讨高密度小间距LED屏工艺

高速高密度PCB设计的关键技术问题是什么?

高密度PCB(HDI)检验标准

Cyntec高密度uPOL模块的特点

什么是高密度DDR芯片

高密度封装失效分析关键技术和方法

基于叠层组装和双腔体结构的高密度集成技术

基于叠层组装和双腔体结构的高密度集成技术

评论