据最新消息,全球显示领导厂商群创光电近日成功拿下欧洲半导体大厂恩智浦的面板级扇出型封装(FOPLP)大单。恩智浦几乎包下了群创所有相关的产能,并计划在今年下半年开始量产出货。

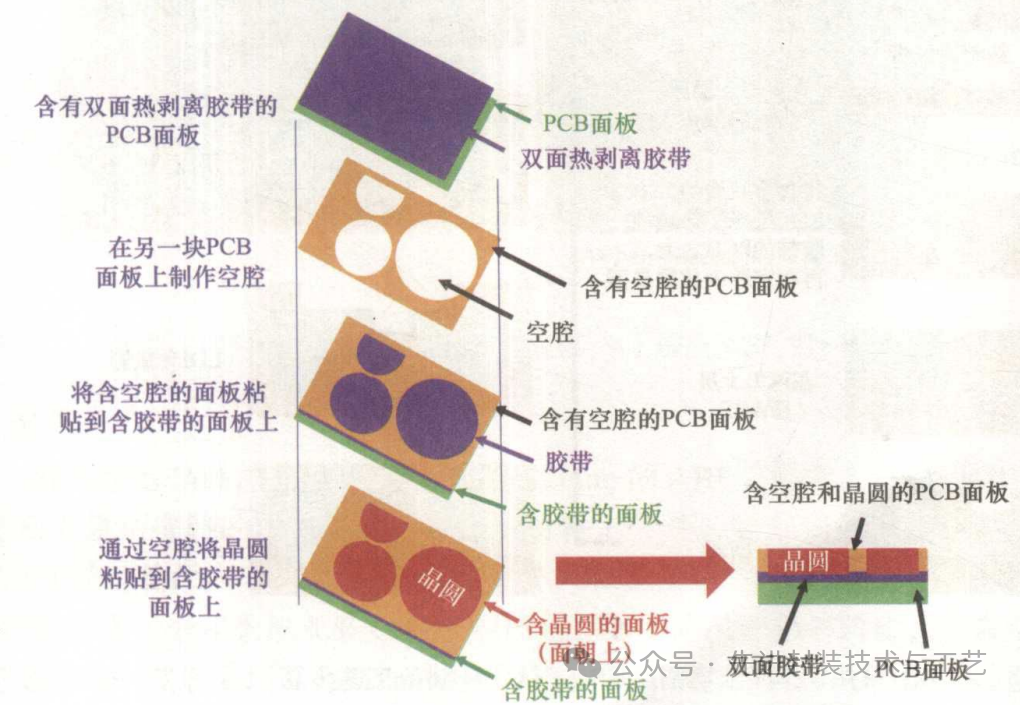

这一重大突破标志着群创在面板级扇出型封装技术领域取得了重大进展。经过八年的布局和研发,群创成功将Chip-First制程应用于其扇出型封装技术中,并成功打入了恩智浦等国际大厂供应链。

群创的面板级扇出型封装技术具有多项优势,能够实现更高的集成度和更小的封装尺寸,同时提高了芯片的可靠性和性能。这一技术的应用将为半导体产业带来革命性的变革,尤其是在5G、物联网、人工智能等新兴领域的应用前景广阔。

此次恩智浦的大单将进一步巩固群创在全球半导体封装市场的地位。为了满足市场需求,群创计划启动第二期扩产计划,为2025年扩充产能投入量产做好准备。

未来,群创将继续加大在面板级扇出型封装技术领域的研发投入,不断推动技术创新和产业升级,为全球半导体产业的发展作出更大的贡献。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

恩智浦

+关注

关注

14文章

6129浏览量

154765 -

封装

+关注

关注

128文章

9339浏览量

149057 -

群创光电

+关注

关注

1文章

27浏览量

10195

发布评论请先 登录

相关推荐

热点推荐

中科创达与恩智浦共同打造面向下一代汽车中央计算架构的参考设计方案

2026年4月26日,在北京国际汽车展览会上,中科创达宣布与恩智浦半导体合作,基于恩智浦S32N5与S32J100产品组合,共同打造面向下一

恩智浦i.MX 8ULP推出工业级新品:9.4×9.4mm封装,适合超低功耗智能边缘系统

新品速递 恩智浦日前推出采用9.4 × 9.4mm封装的i.MX 8ULP系列工业级型号,将该系列的应用范围从商用级i.MX 8ULP应

恩智浦携手COMPREDICT加速边缘AI在汽车应用落地

恩智浦携手COMPREDICT将边缘AI带入汽车应用领域,降低车辆物料清单 (BoM) 成本,助力汽车制造商与一级供应商加速迈向更智能、软件驱动出行的转型。

恩智浦CES 2026参展精彩纷呈

恩智浦的展馆中,有哪些不容错过的“芯”看点?今天,我们跟随恩智浦执行副总裁兼中国事业部总经理李晓鹤先生的探展脚步,一起去划重点!

安富利荣获恩智浦多个奖项

日前,在恩智浦(NXP)2025 GC DFAE培训大会颁奖典礼上,安富利多位现场应用工程师凭借卓越的技术支持能力和杰出的解决方案支持能力,荣获恩智浦2024年度大中华区代理商DFAE

扇出型封装材料:技术突破与市场扩张的双重奏

电子发烧友网综合报道,从台积电InFO封装在苹果A10芯片的首次商用,到中国厂商在面板级封装领域的集体突围,材料创新与产业链重构共同推动着一场封装

发表于 06-12 00:53

•1636次阅读

启扬智能受邀参加2025恩智浦技术峰会

2025年5月14日恩智浦创新技术峰会在上海举行,本次峰会聚焦前沿性的赋能技术,覆盖汽车电子架构、ADAS、汽车电气化、车载信息娱乐系统、智能工业、电力和能源管理、智能家居、医疗保健等热门应用,启扬

米尔诚邀您参加2025恩智浦NXP峰会

2025年恩智浦创新技术峰会暨技术日研讨会焕新登场!一场流动的技术盛宴,走进行业重镇,展示前沿技术,解锁创新方案,助力锐意进取的你,轻松应对未来的技术挑战!目前,恩智浦创新技术论坛(上

消息称群创拿下恩智浦面板级扇出型封装大单

消息称群创拿下恩智浦面板级扇出型封装大单

评论