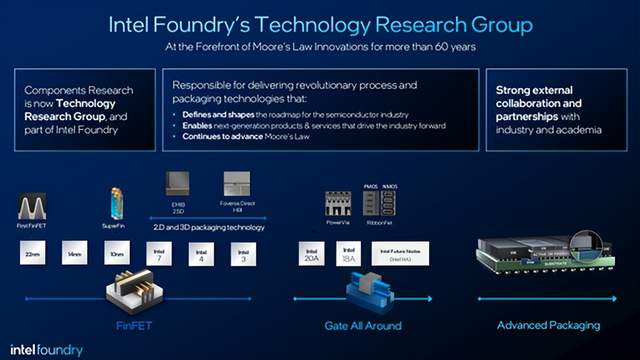

1 月 25 日讯息显示,英特尔已实现基于先进封装科技的大规模量产,包括创新的 Foveros 3D 封装技术。这项技术,由英特尔于新墨西哥州 fab 9 工厂进行深度革新与升级后正式投产后披露。英特尔公司首席运营官 Keyvan Esfarjani 称:“这类尖端封装技术使英特尔脱颖而出,助益客户在提升芯片性能、缩小尺寸以及增强设计灵活性等方面掌握竞争优势。”

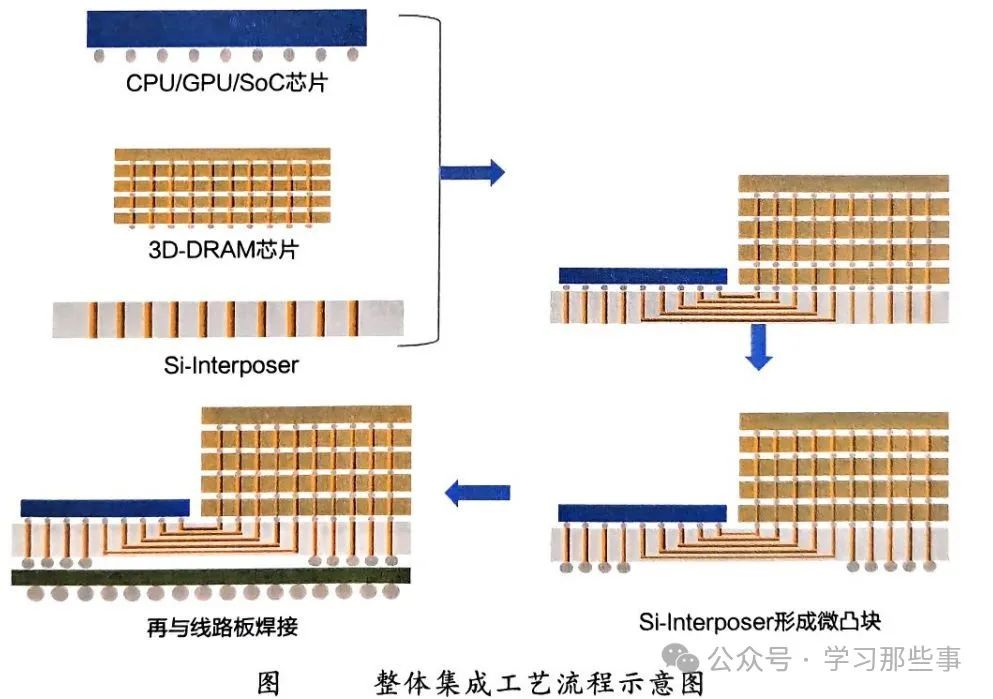

众所周知,整个半导体领域正迈进一个同时整合多个‘芯粒’(Chiplets,也被称为‘小芯片’)在同一封装中的多元时代。基于此,英特尔的 Foveros 及新型 EMIB(嵌入式多芯片互连桥接)等高级封装解决方案被誉为能将一万亿个晶体管融于单一封装之内,且有望在2030年后助力延续摩尔定律。

具体来讲,Foveros 3D先进封装技术在处理器制造过程中,能以垂直角度替代传统的水平堆叠计算模块。更重要的是,Foveros赋予了英特尔及其合作伙伴将各类芯片混合在一起,从而达到优化成本和能源效率的目的。

英特尔甚至透露,预计至2025年,旗下Foveros3D封装产能将有四倍增长。

-

芯片

+关注

关注

462文章

53535浏览量

459148 -

英特尔

+关注

关注

61文章

10275浏览量

179311 -

半导体

+关注

关注

336文章

29985浏览量

258288 -

封装

+关注

关注

128文章

9140浏览量

147894

发布评论请先 登录

18A工艺大单!英特尔将代工微软AI芯片Maia 2

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

3D集成赛道加速!混合键合技术开启晶体管万亿时代

下一代高速芯片晶体管解制造问题解决了!

英特尔先进封装,新突破

英特尔持续推进核心制程和先进封装技术创新,分享最新进展

英特尔18A与台积电N2工艺各有千秋

一文详解2.5D封装工艺

详细解读英特尔的先进封装技术

英特尔IEDM 2024大晒封装、晶体管、互连等领域技术突破

半导体未来三大支柱:先进封装、晶体管和互连

英特尔3D封装工艺进入量产,集成万亿晶体管

英特尔3D封装工艺进入量产,集成万亿晶体管

评论