什么是掩模版

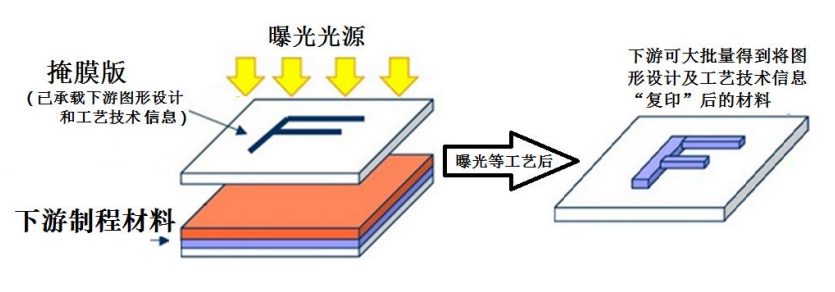

掩模版(Photomask)又称光罩、光掩模、光刻掩模版、掩膜版、掩膜板等,是光刻工艺中关键部件之一,是下游行业产品制造过程中的图形“底片”转移用的高精密工具,是承载图形设计和工艺技术等知识产权信息的载体。掩模版用于下游电子元器件制造业批量生产,是下游行业生产流程衔接的关键部分,是下游产品精度和质量的决定因素之一。

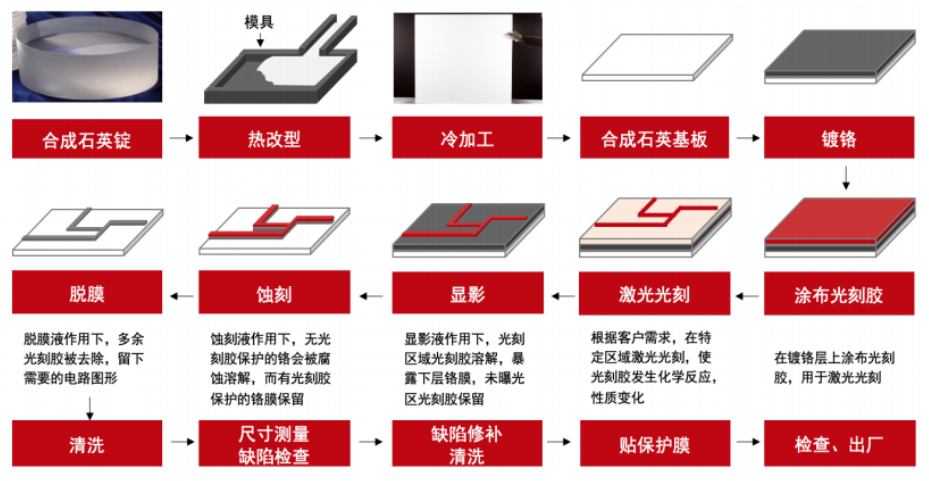

掩模版(石英)的制造过程掩模版的工作原理

作为光刻复制图形的基准和蓝本,掩模版是连接工业设计和工艺制造的关键,掩模版的精度和质量水平会直接影响最终下游制品的优品率。

资料来源:清溢光电招股说明书

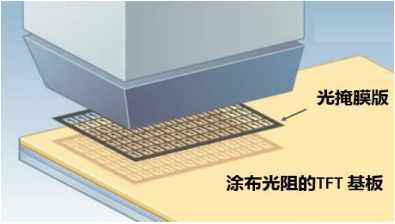

以TFT-LCD制造为例,利用掩模版的曝光掩蔽作用,将设计好的TFT阵列和彩色滤光片图形按照薄膜晶体管的膜层结构顺序,依次曝光转移至玻璃基板,最终形成多个膜层所叠加的显示器件。

以集成电路为例,其制造过程需要经过多次曝光工艺,利用掩模版的曝光掩蔽作用,在半导体晶圆表面形成栅极、源漏极、掺杂窗口、电极接触孔等。

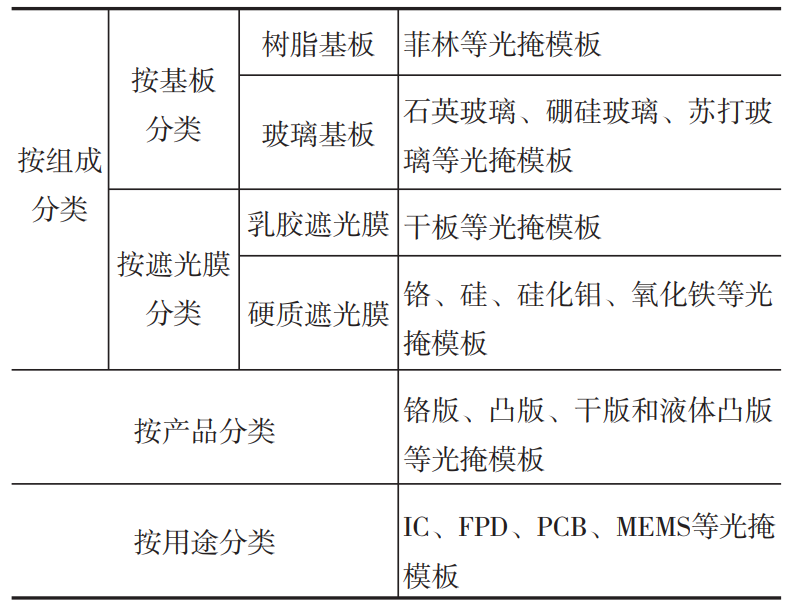

掩模版的分类

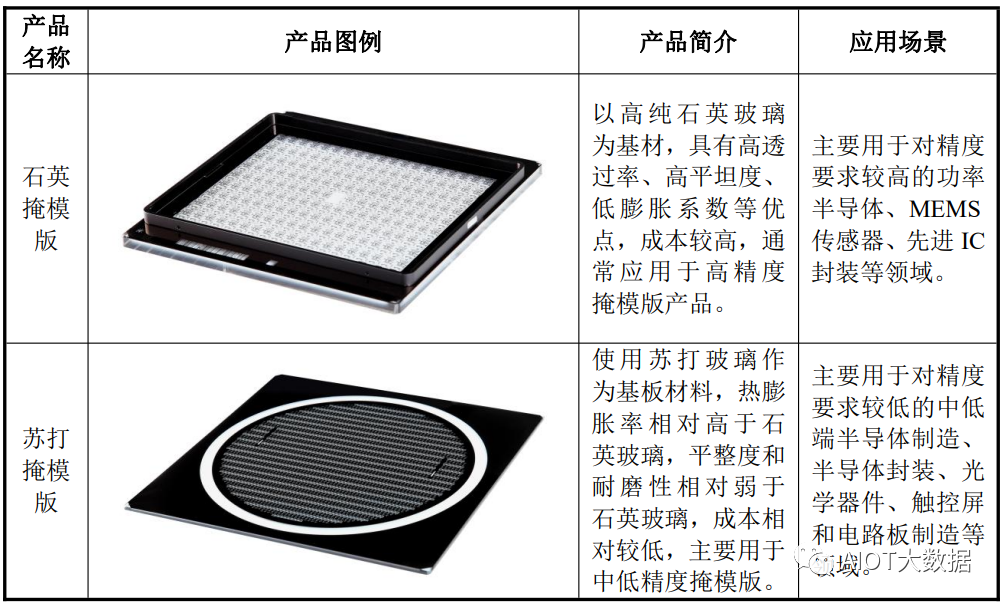

按光掩模版基板材料可分为透明树脂基板和透明玻璃基板。透明树脂基板易于大型化,但是易变形,相较而言玻璃基板更为常用,按照玻璃材质又可细分为合成石英光掩模版、硼硅玻璃光掩模版和苏打(钠钙玻璃)光掩模版三类。

按光掩模版遮光膜材料可分为乳胶遮光膜与硬质遮光膜两大类。硬质遮光膜又可细分为铬、硅、硅化钼、氧化铁四类,其中铬质材料具有涂覆均一性好、刻蚀精度高、且无毒无污染的优点,应用最为广泛。

按光掩模版的用途可分为铬版、凸版、干版和液体凸版四类。其中,铬版主要由铬质遮光膜与石英基板组成,由于其精度高、耐用性好,广泛应用于微电子制造领域。

石英掩模版使用石英玻璃作为基板材料,透光率高,热膨胀系数低,比苏打玻璃更平整耐磨,使用寿命更长,主要用于高精度掩模版;苏打掩模版用苏打玻璃作为基板材料,由于材料的原因,各方面性能都劣于石英掩模版,主要用于中低精度掩模版;树脂基板由于透光率一般,不耐用,精度低,主要用于PCB掩膜。

掩模版是集成电路制造过程中的图形转移工具或者母板,也就是半导体芯片的母板,承载着图形信息和工艺技术信息。掩模版的作用是将承载的电路图形通过曝光的方式转移到硅晶圆等基体材料上,从而实现集成电路的批量化生产。掩模版广泛应用于半导体、平板显示、电路板、触控屏等领域。

半导体掩模版市场需求分析

根据SEMI最新的《世界晶圆厂预测报告》(WorldFabForecast),预计全球2021年至2023年将新建84座大型芯片制造工厂,总投资额超5,000亿美元;以新能源汽车为代表的细分市场持续推动半导体需求增长,在高需求背景下预计2022年新增33家工厂、2023年新增28家工厂。《世界晶圆厂预测报告》显示,2021年至2023年,中国大陆预计将建设20座支持成熟工艺的大型芯片制造工厂。

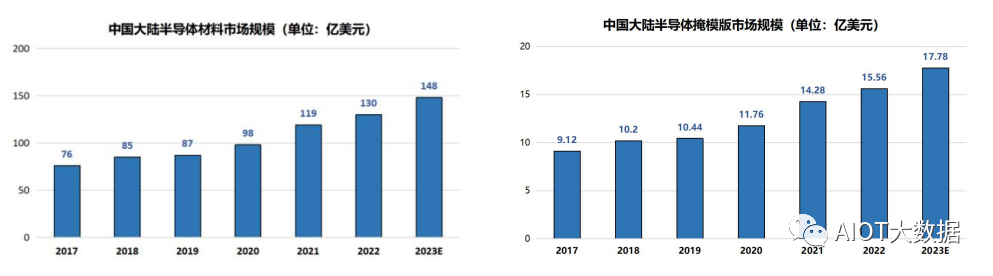

根据SEMI数据、CEMIA数据,全球半导体材料市场规模呈现稳步增长态势,从2017年469亿美元增长至2022年的727亿美元,年复合增长率为9.16%,预计2023年规模为794亿美元;中国大陆半导体材料市场规模快速增长,从2019年为87亿美元增长至2022年的129.7亿美元,年复合增长率为14.24%,预计2023年规模为148.2亿美元,增速远超全球半导体材料市场。

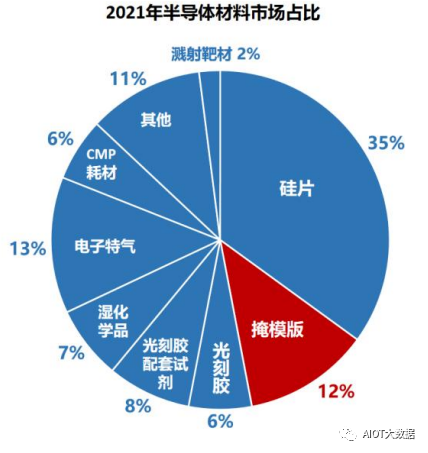

根据SEMI数据,作为半导体材料的重要组成部分,掩模版占半导体材料市场规模的比例约为12%,仅次于硅片和电子特气,具体情况如下:

由此推算,2023年全球半导体掩模版市场规模为95.28亿美元,2023年中国半导体掩模版的市场规模约为17.78亿美元。未来随着半导体行业容量的持续上升,半导体掩模版市场规模将不断提升。

国内第三方掩模版市场

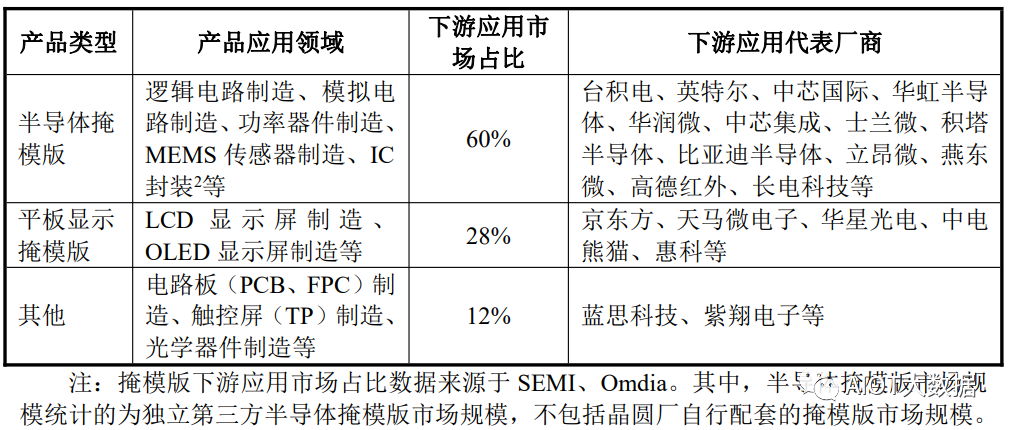

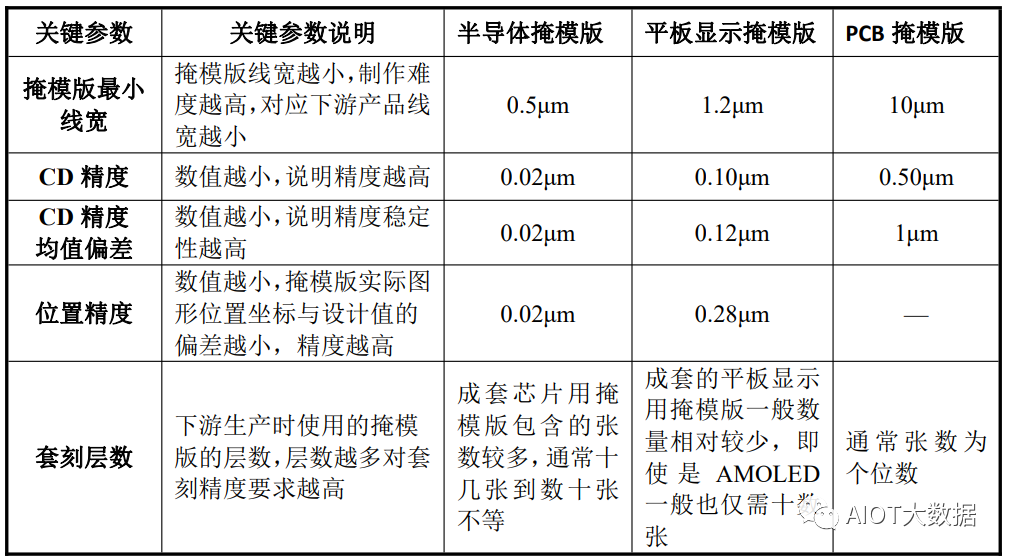

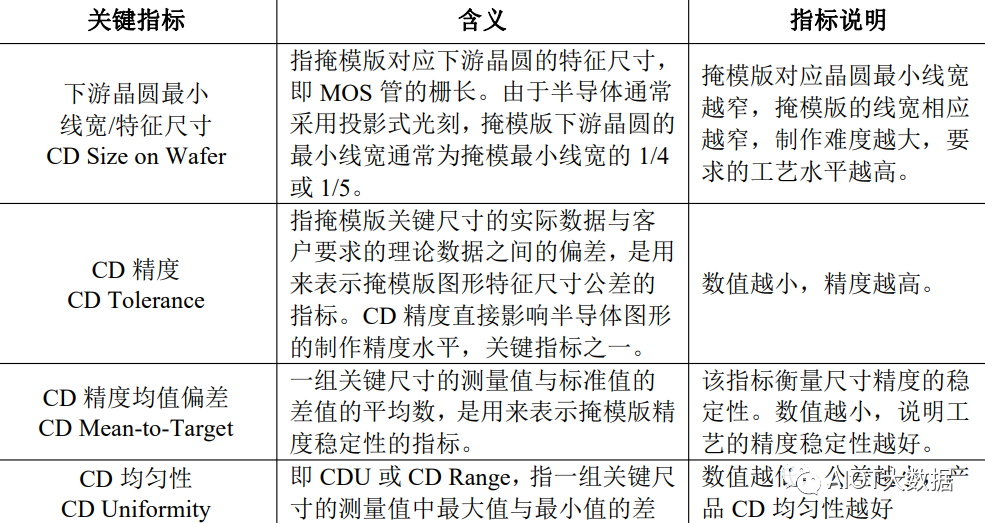

相比较而言,半导体掩模版在最小线宽、CD精度、位置精度等重要参数方面,均显著高于平板显示、PCB等领域掩模版产品。

(半导体为130nm工艺节点半导体掩模版关键参数,平板显示为高精度TFT-Array掩模版关键参数)

国产特色半导体掩模版产业链

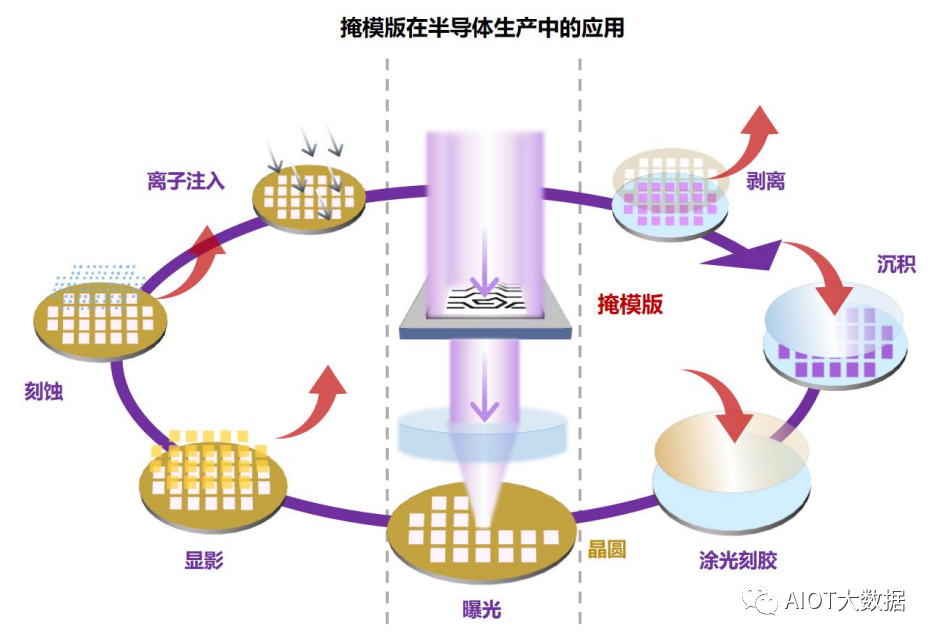

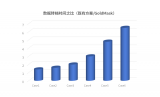

掩模版是半导体制造工艺中的关键材料,用于半导体制造的光刻环节。半导体制造的光刻是指通过曝光工序,在晶圆表面的光刻胶上刻画出电路图形,然后通过显影、刻蚀等工艺流程,最终将电路图形转移到晶圆上的过程。

掩模版在半导体生产中的应用如下图所示:

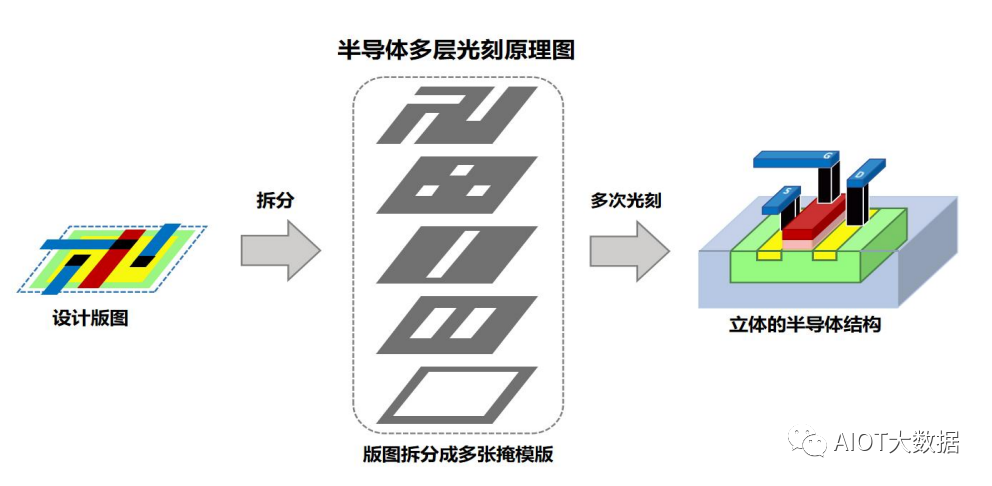

半导体器件和结构是通过生产工艺一层一层累计叠加形成的,芯片设计版图通常由十几层到数十层图案组成,芯片制造最关键的工序是将每层掩模版上的图案通过多次光刻工艺精准地转移到晶圆上(如下图所示)。半导体光刻工艺需要一整套相互之间能准确套准的、具有特定图形的“光复印”掩模版,其功能类似于传统相机的“底片”。掩模版是半导体制造工艺中最关键的材料之一,其品质直接关系到最终产品的质量与良率。

普通掩模版产品根据基板材质的不同主要可分为石英掩模版、苏打掩模版两类:

半导体掩模版的生产涉及CAM、光刻、检测三个主要环节,具体包括版图处理、图形补偿、曝光、显影、刻蚀、清洗、缺陷检验、缺陷修补、参数测量、贴光学膜等多项复杂工艺,对补偿算法、制程能力、精度水平、缺陷管控具有严格要求,技术壁垒较高。

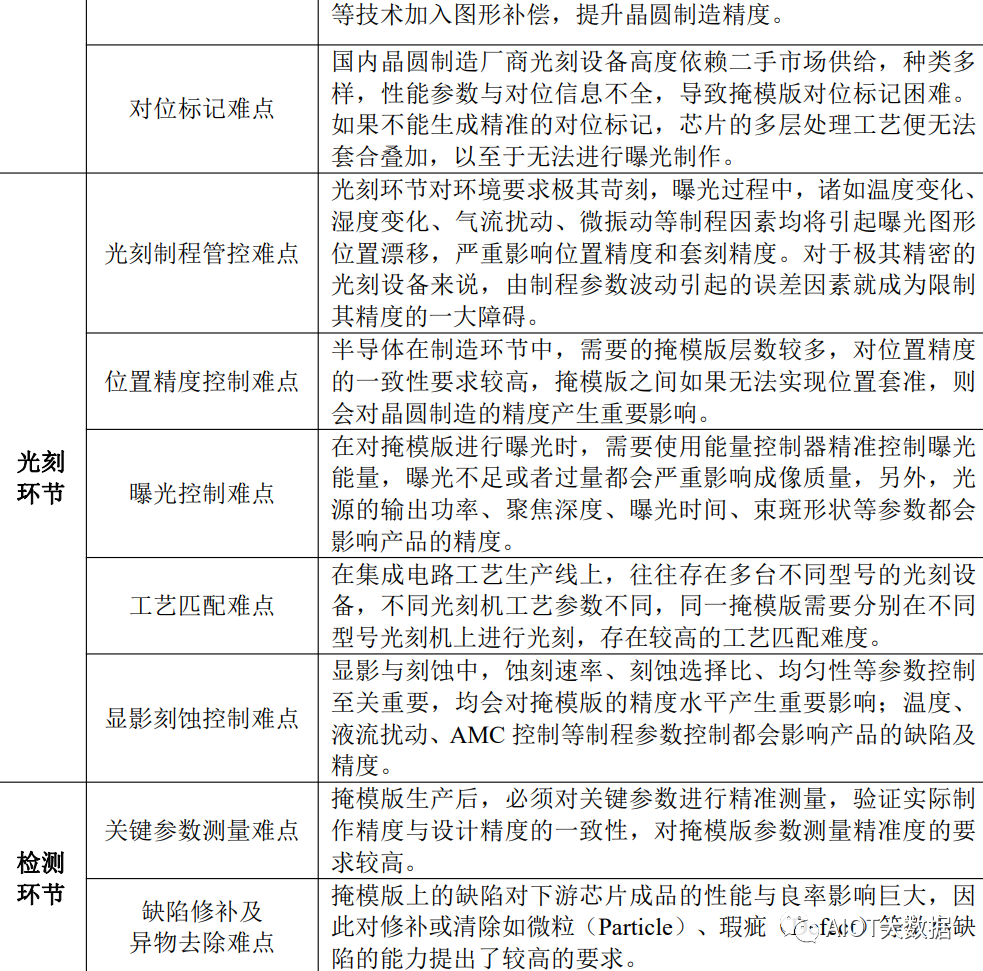

独立的第三方半导体掩模版生产商,需要根据上游芯片设计公司(Fabless)提供的设计版图,及下游晶圆制造厂商(Foundry和IDM)提供的制作工艺要求,设计并制作出同时满足芯片设计公司和晶圆制造厂要求的、用于晶圆加工的半导体掩模版。掩模版是上游芯片设计公司与下游晶圆制造厂商的中间桥梁,是芯片制作过程中至关重要的一环,因此独立第三方半导体掩模版厂商既需要快速理解并转换上游芯片设计要求,又要充分了解下游晶圆制造工艺需求,制作出适配下游光刻机的掩模版。

当前国内芯片设计公司使用的EDA软件多样,各家公司设计图档缺乏统一标准,存在大量非标准化设计;下游光刻机台二手设备流通普遍,型号众多,不同光刻机的对位要求、工艺要求不同,相应信息不全。在这种情况下,第三方半导体掩模版厂商需要有较强的上下游匹配能力。

半导体掩模版行业高度依赖专有技术,具有鲜明的“Know-How”特点,进入门槛较高。第三方半导体掩模版行业的进入门槛不仅体现在设备投入与人才投入,更是体现在专有技术积累上,这些专有技术是公司多年来针对不断升级的客户需求的技术创新成果,是上万次各类试验的数据结晶,这也正是第三方半导体掩模版厂商的核心竞争力,但往往该类技术不易于以专利形式保护。专有技术形成了第三方半导体掩模版厂商享有的技术红利,同时也构成了半导体掩模版较高的行业壁垒。

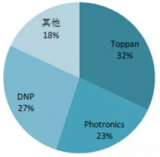

半导体掩模版作为半导体制造关键材料之一,由于其技术壁垒较高,国内市场长期由国际大厂所占据,如美国Photronics、日本Toppan、日本DNP等,国内厂商市场影响力尚低。

另外当前国内半导体产业的软件、设备及关键材料等产业链环节均不完善。就半导体掩模版而言,上游芯片设计公司使用的EDA软件多样,存在大量非标准化设计;下游晶圆制造厂商的核心设备,如光刻机同样存在型号多、二手设备普遍等特点。从掩模版制造的核心原材料和设备来看,高精度半导体掩模版核心原材料石英基板仍被日韩企业垄断,设备仍主要依赖进口。

晶圆制造客户认证流程

掩模版作为下游晶圆制造厂商(Foundry和IDM)光刻环节极其重要的设计图案转移工具,是晶圆制造光刻环节不可或缺的光学模具,对晶圆制造和芯片产品品质影响巨大。因此,下游晶圆制造厂商对掩模版厂的要求较为严格,一般情况下,晶圆制造厂商对掩模版工厂的验证和供应商评估期在6至12个月甚至更长,准入流程及持续考察评估主要如下:

①签订NDA协议(保密协议)。

由于掩模版的生产涉及芯片设计方案机密,晶圆制造厂商需评估第三方掩模版供应商的信息安全管理体系和能力,并与其签订NDA协议。

②需求与能力评估。

主要考察掩模版厂的制版能力是否满足晶圆制造厂商的制版等级需求,主要考核掩模版厂工艺的关键指标,如关键尺寸(CriticalDimension,CD)、关键尺寸精度均值偏差(CDMean-to-Target)、关键尺寸公差(CDTolerance)、位置精度(Registration)、套刻精度(Overlay)、缺陷尺寸(DefectSize)等。

③双方工艺的匹配。

主要根据晶圆制造厂商的实际光刻工艺需求,验证掩模版厂制造工艺和关键指标的测量方式是否与晶圆制造厂商相匹配。不同的晶圆制造厂商在光刻环节中的光刻设备、光刻胶、OPC工艺选择不同,光刻工艺和设备调校习惯不同,同时晶圆制造厂商与掩模版厂的测量系统也存在差异,因此晶圆制造厂商需要实地考察掩模版厂的制造工艺、实际测量并验证掩模版的精度水平,以保证两者光刻工艺的匹配,并消除因测量方式不同导致的系统性的精度误差。

④数据处理验证。

这一环节是对掩模版的数据处理和JDV(制版图形的在线检查)确认环节进行验证。不同的芯片设计公司和晶圆制造厂商的数据设计的格式与规范存在差异,与掩模工厂之间的数据传输方式、JDV数据确认方式都需要进行验证和确认。掩模工厂和设计公司需要分别对数据处理环节进行可行性及准确性验证,并且在这个过程中评估信息安全管理是否符合要求。

⑤掩模版测试样品评估。

掩模版工厂设计一些标准化的、含有特定评估测试图案的掩模版样品,提供给晶圆制造厂商进行样品评估。晶圆制造厂商根据实际样品测试结果来实测掩模版的关键指标是否达到要求。

⑥产品测试与验证。

对掩模版厂提供的掩模版成品进行流片测试。产品测试与验证是一个长期跟踪、全流程考察的过程,通常掩模工厂的验证和供应商评估期在6至12个月甚至更长,对于产品的验证会持续追踪到最终芯片的可靠性和功能测试。

⑦品质体系审核。

晶圆制造厂商同样需要对掩模工厂的品质控制体系进行审核,ISO9001(质量管理体系认证)、ISO14001(环境管理体系认证)、ISO27001(信息安全管理体系)等品控体系审核通过后才可纳入合格供应商。

上述认证周期一般在6至12个月甚至更长,工艺节点越高的掩模版产品认证周期越久。晶圆制造厂商审核通过后才可纳入合格供应商名单,建立起正式的合作关系。由于下游客户对半导体掩模版厂商要求高、认证周期长,双方建立合作关系后,不会轻易更换供应商,合作稳定性较好。

同时掩模版承载着芯片设计方案和图形信息,涉及芯片设计方案机密,第三方掩模版工厂必须建立一套严密的安全控制机制,避免信息泄露,从而保障客户的知识产权。

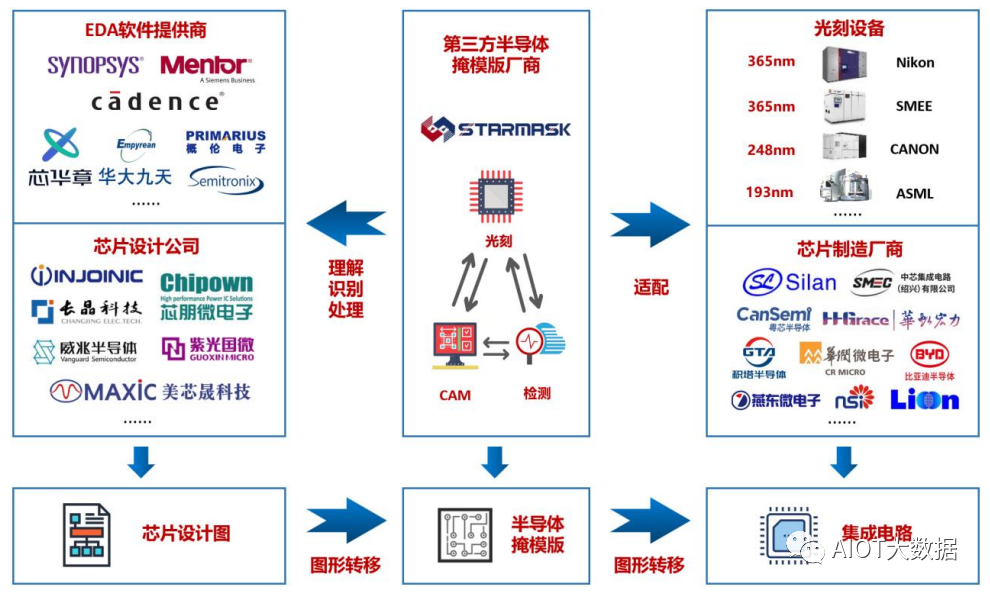

掩模版的工艺流程图

1、建立客户合作关系,客户下达订单,并将客户文件(设计版图)、规格书发送给公司。

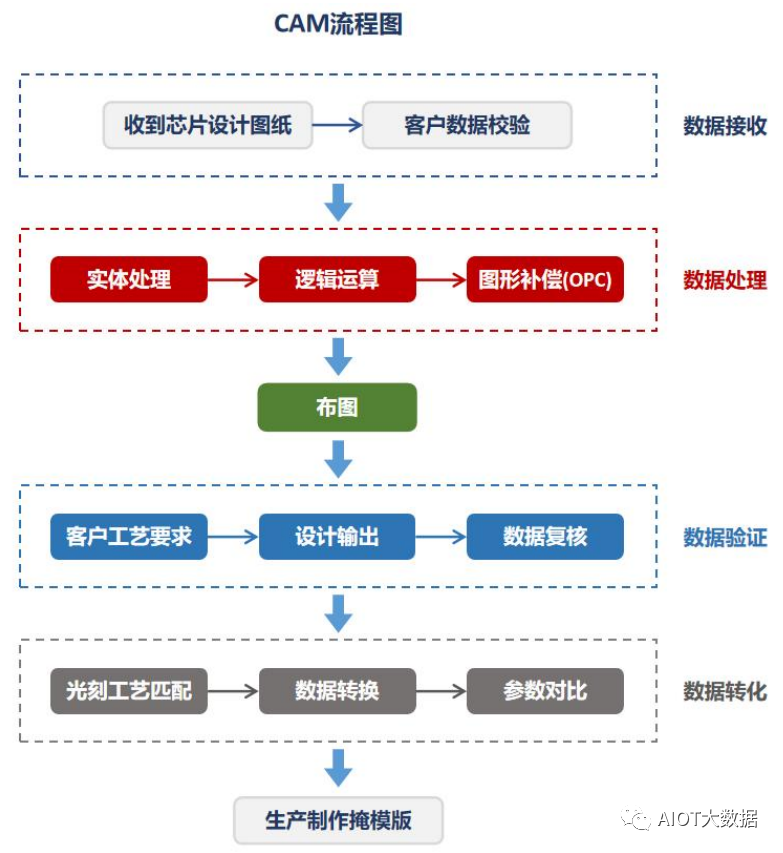

2、CAM:收到客户芯片设计版图及规格书后,通过专业设计软件将客户的版图进行数据分层、实体处理、逻辑运算、OPC等处理,并对处理过的版图数据进行数据检查和JDV(制版图形的在线检查)确认,最后按照相应的工艺参数将文件格式转换为掩模版光刻设备专用的数据形式。

3、光刻:通过光刻机对掩模基材进行直写光刻,完成客户图形曝光。掩模版制造通常采用正性光刻胶,通过曝光作用使目标区域的光刻胶内部发生交联反应,从而进行图像转移。

4、显影:将曝光完成后的掩模版显影,以便进行蚀刻。在显影介质的作用下,经过曝光区域的光刻胶会溶解,而未曝光区域则会保留并继续保护遮光膜层。

5、蚀刻:对遮光膜层进行蚀刻,保留图形。在蚀刻介质的作用下,没有光刻胶保护的区域会发生化学反应,而有光刻胶保护的区域的遮光膜则会保留。

6、脱膜:光刻胶的保护功能已经完成,脱膜工序通过脱膜液去除多余光刻胶。

7、清洗:将掩模版正、反面的污染物清洗干净,为缺陷检验做准备。

8、关键参数测量:对掩模版关键尺寸(CDSize)、CD精度(CDTolerance)、位置精度(Registration)、套刻精度(Overlay)等关键参数进行测量,判定尺寸的准确程度。

9、AOI扫描:对照客户技术/品质指标,使用自动光学检测设备(AOI)检测掩模版制版过程产生的缺陷并记录坐标及相关信息。

10、缺陷修补:利用激光物理作用或化学反应相结合的方式,修复掩模版在生产过程产生的瑕疵(Defect)、微粒(Particle)等缺陷。

11、STARlight扫描:对掩模版制版过程附着的微粒(Particle)进行检查。

12、贴Pellicle膜:在掩模版上贴合Pellicle膜,避免微粒污染掩模版表面,降低下游客户制造过程中微粒造成的不良率。

13、最终检查:对掩模版做最后的检测工作,以确保掩模版符合品质指标。

14、对掩模版进行包装,然后发货。

核心技术主要涉及上述流程中CAM版图处理、光刻(包括曝光、显影、刻蚀及清洗环节)及检测(包括关键参数测量、缺陷修补等出货前的检测环节)三大环节,从而保证产品的精度和品质水平。

半导体掩模版行业概况

半导体掩模版生产厂商可以分为晶圆厂自建配套工厂和独立第三方掩模厂商两大类。由于28nm及以下的先进制程晶圆制造工艺复杂且难度大,各家用于芯片制造的掩模版涉及晶圆制造厂的重要工艺机密且制造难度较大,因此先进制程晶圆制造厂商所用的掩模版大部分由自己的专业工厂内部生产,如英特尔、三星、台积电、中芯国际等公司的掩模版均主要由自制掩模版部门提供。

对于28nm以上等较为成熟的制程所用的掩模版,芯片制造厂商为了降低成本,在满足技术要求下,更倾向于向独立第三方掩模版厂商进行采购。根据贝恩咨询发布的《中国半导体白皮书》,全球晶圆制造代工收入中28nm以上制程的收入占比约为55.38%,占据晶圆代工大部分收入。

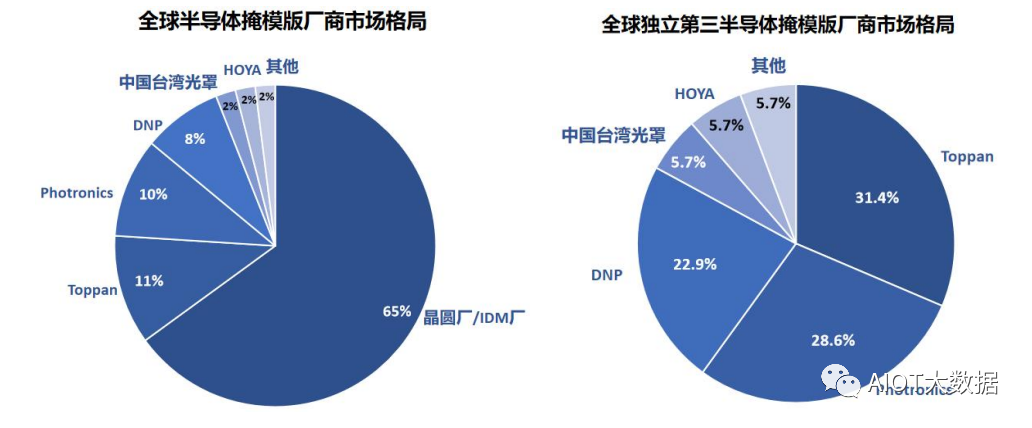

根据SEMI数据,在全球半导体掩模版市场,晶圆厂自行配套的掩模版工厂规模占比65%,独立第三方掩模厂商规模占比35%,其中独立第三方掩模版场主要被美国Photronics、日本Toppan和日本DNP三家公司所控制,三者共占八成以上的市场规模,市场集中度较高。

由于半导体掩模版具有较高的进入门槛,国内半导体掩模版主要生产商仅包括中芯国际光罩厂、迪思微、中微掩模、龙图光罩、清溢光电、路维光电、中国台湾光罩等。中芯国际光罩厂为晶圆厂自建工厂,产品供内部使用;清溢光电、路维光电产品以中大尺寸平板显示掩模版为主,半导体掩模版占比较低。龙图光罩是国内屈指可数的第三方半导体掩模版厂商,工艺水平、出货量及市场占有率居国内企业前列。

技术难度

掩模版是将虚拟的电子设计图形批量转化为芯片实体电路图形的核心工具,是决定半导体制程水平和良率的关键因素之一。随着半导体的制程工艺的不断提升、芯片设计的不断复杂,掩模版的研发、生产、制造难度也显著提升。

1、CAM环节:高制程节点下晶圆曝光存在图形失真,需要对掩模版图形进行光学补偿,存在较高的技术难度

随着掩模版线缝水平的不断提升,下游晶圆在使用光刻机曝光时光学效应影响越发显著,会出现实际光刻图案与芯片设计图案失真变形的现象,严重影响芯片的性能与良率。为解决上述问题,提高晶圆曝光的分辨率与精度,需要在CAM环节对掩模版图形进行二次加工(OPC),通过图形补偿来抵消图形偏差,使得曝光后的图形满足设计要求。图形补偿(OPC)技术具有较高的技术难度,对图形特征点识别、运算速度、补偿准确度都有较高的要求。

(1)CAM版图处理重要性

CAM版图处理是掩模版生产制造的重要环节,是芯片设计版图到掩模版图案的图像转移起点,本质是图形数据的转换与处理。半导体掩模版厂商需要获取芯片设计公司提供的芯片设计版图和晶圆制造厂商提供的制版要求,根据两者信息转换成可以被掩模版光刻机识别的掩模版图形,这一制造转换过程需要计算机辅助进行,即计算机辅助制造(CAM)。CAM版图处理的主要工序包含两个层面:

①上游客户芯片设计版图数据的校对、实体处理、逻辑运算、工艺补偿、布图、验证;

②根据下游晶圆制造厂商工艺需求的解读及实现,生成提供给客户端的JDV(JobDeckView)数据;结合内部制造能力,出具提供给掩模版制造环节的掩模制作数据、AOI检测数据及量测信息等。因此,CAM版图处理是掩模版制造的起点,这一工序对掩模版的制造至关重要,如果CAM版图处理无法满足客户需求或出现设计偏差则直接导致掩模版制造失败。CAM版图处理的主要流程如下图所示:

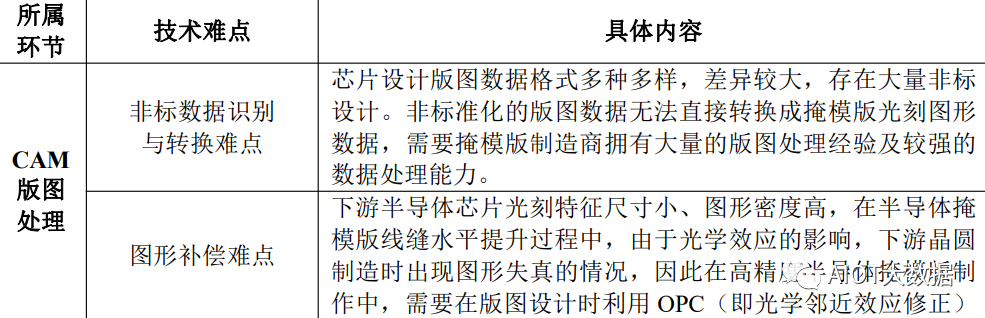

(2)CAM版图处理技术难点

CAM版图处理阶段主要有以下难点:

①原始芯片设计版图存在大量非标准化数据,无法直接进行图形转换。不同上游领域的芯片设计公司使用的EDA软件不同且设计习惯不同,导致提供的数据格式多种多样,差异较大,存在大量非标设计。非标准化的版图数据无法直接转换成掩模版图形,需要掩模版制造商拥有快速识别并转换成光刻机可识别图形数据能力。

②半导体掩模版图形补偿难度大。随着下游半导体芯片制程节点的提升,掩模版的线缝越来越窄,在半导体掩模版线缝水平提升过程中,由于光学衍射效应的影响,掩模版用于下游晶圆生产时会出现图形失真的情况,因此需要在版图设计中加入OPC图形补偿,提升晶圆制造精度水平。

图形补偿(OPC)技术光学临近效应(OpticalProximityEffect,OPE)是指在曝光过程中,由于透过掩模版上相邻图形之间的光波发生衍射,导致投影到晶圆上的图形和掩模版上的图形不一致的现象。这种图形的不一致主要表现在三个方面:图形拐角的变化、线条宽度的变化和线条顶端的变化,而且随着集成电路特征尺寸不断地减小,这种光刻图形的变形与偏差变得越来越严重,成为影响芯片性能和成品率的重要因素。为了解决光学临近效应,一种有效的解决方案是在掩模图案上增加光学邻近效应修正(OPC)算法,通过改变原芯片掩模版图形的形状来减小光刻图形的偏差。一般来说,当晶圆上的线宽小于曝光波长时,必须对掩模上的图形做光学邻近效应修正。

③下游光刻设备性能参数与对位信息缺失,导致半导体掩模版对位标记困难。国内晶圆制造厂商光刻设备高度依赖二手市场供给,种类多样,性能参数与对位信息不全。每个光刻机设备商的对位标记系统都自成一套,导致掩模版对位标记困难。如果没有精确的对位标记,芯片的多层处理工艺便无法套合叠加,以至于无法进行曝光制作,因此,需要掩模版厂商充分了解下游晶圆制造厂商光刻机性能参数与对位信息,形成自有处理规则确保掩模版对位标记的准确性。

精准对位标记技术下游晶圆制造厂商在光刻曝光环节用到的掩模版对位标记主要包括:A.初对位标记,作为曝光机的对准系统快速定位掩模版的大概位置;B.精对位标记,曝光机在找到初对位标记大概确定掩模版的位置后,根据设计图纸上初对位与精对位标记的相对坐标偏移找到精对位标记,将掩模版的坐标和曝光机的坐标进行高精度对准的标记;C.工作台对位标记,用于掩模版和晶圆的工作台进行对准的标记。每个曝光机设备商的对位标记系统都自成一套,如果没有精确的对位标记,芯片的多层处理工艺便无法套合叠加,以至于无法进行曝光制作。

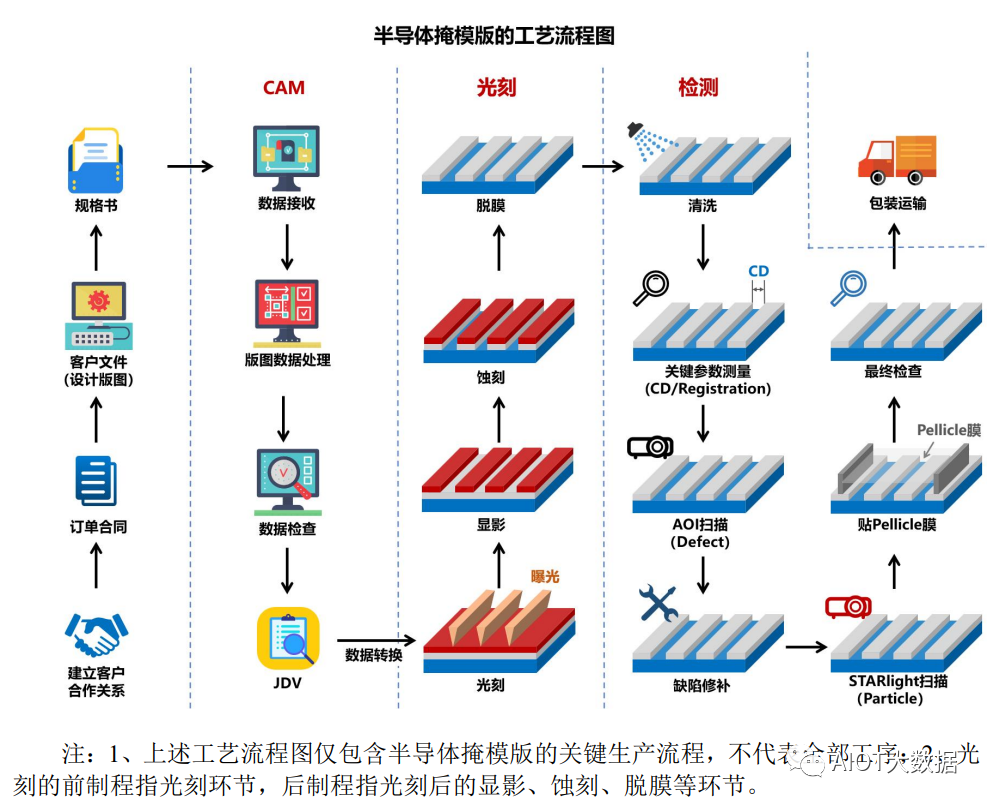

2、光刻环节:光刻环节的技术壁垒在于光刻多环节、多因素的精准控制光刻环节的技术壁垒主要体现在以下两点:

①光刻机作为极其精密的设备,对环境要求极为苛刻,光刻环节中由于环境参数波动引起的误差因素对掩模版的精度水平会产生严重影响,因此能够精细控制各类环境因素波动是掩模版制造的一大难题。

②在使用光刻机对掩模版进行曝光时,曝光能量的控制对掩模版精度水平至关重要,曝光不足或者过量都会严重影响成像质量。

(1)光刻环节重要性

光刻作为掩模版制造的核心工艺,对于掩模版产品的品质影响极其重要。光刻环节主要包括曝光、显影、刻蚀和清洗,光刻是将CAM版图数据转换成激光直写系统控制数据,由计算机控制高精度激光束扫描,利用激光对涂有光刻胶的掩模基板按照设计的图档进行激光直写,从而完成了集成电路信息从CAM设计版图到掩模版图形的转移过程。

光刻环节直接决定了最小线/缝宽、边缘粗糙度、关键尺寸均匀性(CDuniformity)、关键尺寸精度均值偏差(CDmeantoTarget)等图案指标;同时光刻机平台定位的精度也直接决定了掩模版位置精度(Registration)、套刻精度(Overlay)等指标。

(2)光刻环节技术难点

光刻环节并非是对设备的简单运用,而是结合公司长期的自主研发成果积累,对光刻、显影等环节的各个参数及影响因素进行长期系统性研究的综合结果。光刻环节难点在于精度与缺陷控制,涉及多个环节,不同环节之间又会相互影响。公司持续优化光刻工艺,最大化发挥设备性能水平,实现了精度水平与缺陷控制的不断突破。

(3)光刻环节核心技术及具体表征

针对半导体掩模版光刻环节中关于制程管控、套刻精度控制、曝光控制、工艺匹配、显影刻蚀控制等难点,主要有以下核心技术:

①光刻制程管控技术

光刻环节对环境要求极其苛刻,曝光过程中,诸如温度变化、湿度变化、气流扰动、微振动等因素均将引起曝光图形位置漂移,严重影响位置精度和套刻精度。具体来讲,光刻机关键部件会由于空间温度的漂移而产生形变进而导致运动误差,而以能量探测器为代表的测量仪器会受温度、湿度、压力影响,参数异常势必会造成测量结果的误差进而最终影响光刻精度。光刻机在步进过程中,会在其运动区域形成气流冲击,使得光刻机腔体内形成不均匀压力场,同时也会造成平台的微小振动,进而影响位置精度。对于极其精密的光刻设备来说,由环境参数波动引起的误差因素就成为限制其精度的一大障碍。

②位置精度光刻匹配技术

半导体设计版图通常由几十层图案组成,芯片制造的关键工序是将每层掩模版上的图案通过多次光刻工艺精准地转移到晶圆上,因此,半导体掩模版不仅需要能匹配多个不同的光刻机台,半导体掩模版之间也需要能够相互套准。

③曝光精细化控制技术

在对掩模版进行曝光时,需要使用光刻机将掩模基板表面的光刻胶进行感光处理,从而获得预期掩模图形。进行曝光时,需要使用能量控制器精准控制曝光能量,曝光不足或者过量都会严重影响成像质量,光源的输出功率、曝光时间、聚焦深度、束斑形状都会直接影响到掩模产品的精度。

④精准工艺匹配技术

光刻机的匹配使用是指同一掩模版可以分别在不同型号光刻机上进行光刻,而不影响光刻工艺的质量。在集成电路工艺生产线上,往往投入多台光刻设备同时使用,不同光刻机往往规格不同、参数不同。同一掩模版需要分别在不同型号光刻机上进行光刻,存在较高的匹配难度。

⑤显影刻蚀控制技术

显影是指通过化学作用,掩模版上经过激光或电子束曝光区域的光刻胶会溶解,而未曝光区域则会保留并继续保护遮光膜层。蚀刻是显影的下一步工序,是通过蚀刻介质对遮光膜层进行蚀刻,保留图形。在蚀刻介质的作用下,没有光刻胶保护的区域会发生化学反应,而有光刻胶保护的区域的遮光膜层则会保留,这样就形成了掩模版的图案。因此,在显影与刻蚀的环节中,蚀刻速率、刻蚀选择比、均匀性等参数控制至关重要,均会对掩模版的精度水平产生重要影响。同时,显影刻蚀环节对温度、液流扰动、AMC控制等制程参数控制要求极为苛刻。

3、检测环节:掩模版上的各类缺陷通常极为微观,能够精准识别并修补具有较高的技术难度掩模版在制造过程中产生的各种缺陷及各类精度偏差,与生产、传输、储存等环节中出现的污染物,会通过半导体曝光工艺传递到下游芯片上,严重影响芯片的性能与良率,且随着制程的不断提高,对缺陷尺寸的容忍度越来越低。能够精准检测出掩模版上纳米级缺陷,并在不产生二次污染的情况下进行精准修补,技术难度较高。

检测环节核心技术

(1)检测环节的重要性及难点

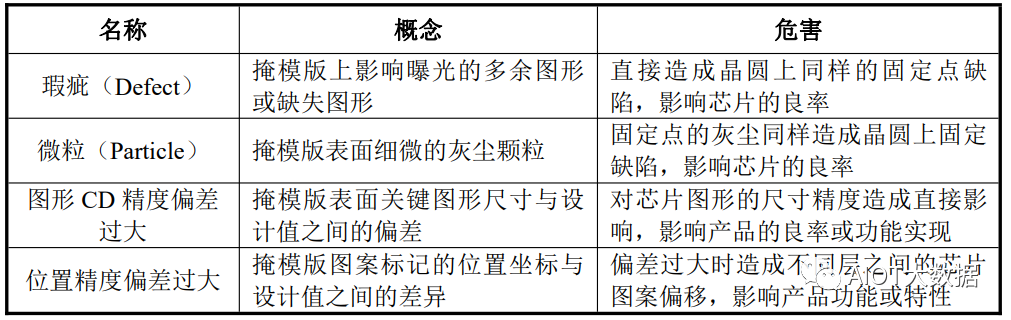

掩模版在制造过程中因生产环境、材料异常等原因产生的各种缺陷及各类精度偏差,与生产、传输、储存等环节中出现的污染物,会通过半导体曝光工艺传递到下游芯片上,并以影响芯片性能与可靠性的缺陷形式存在。掩模版的缺陷主要包括瑕疵(Defect)、微粒(Particle)、图形CD精度偏差过大、位置精度偏差过大等。掩模版生产中主要缺陷及其危害如下表所示:

掩模版的缺陷通常来说是非常微观的(亚微米级别),但由于半导体掩模版线缝和精度要求较高,即使是亚微米级别的缺陷对掩模版的品质也影响巨大,会直接影响到下游芯片成品的性能与良率,因此能够及时、准确地对掩模版上的各类缺陷进行测量,并在不产生二次污染的情况下对缺陷进行精准修补,具备较高的技术难度。

(2)检测环节核心技术及具体表征

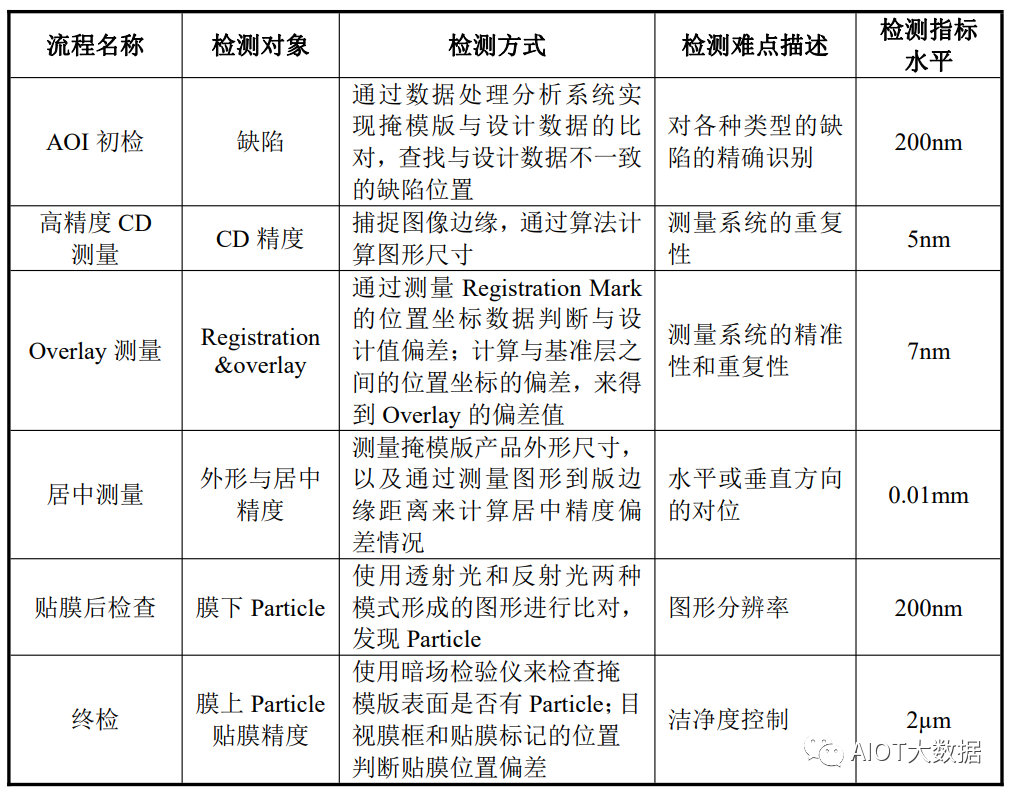

①高精度测量技术

掩模版生产后,必须对关键参数进行精准测量,验证实际制作精度与设计精度的一致性,同时还要对掩模版上的各种缺陷进行检测。公司自研了一系列掩模版精度测量及缺陷检测技术,包括AOI初检、高精度CD测量、Overlay测量、居中测量、贴膜后检查、终检等工序,能够有效地测量出掩模产品的关键参数及瑕疵(Defect)、微粒(Particle)、图形CD精度偏差过大、位置精度偏差过大等缺陷情况。具体检测技术、检测水平如下表所示:

②缺陷修补与异物去除技术

针对在检测环节中检测出的一系列缺陷及异物,利用激光物理作用与蚀刻液化学反应相结合的方式,高效、准确的修复掩模版在生产过程产生的缺陷,有效地消除了激光修复后所产生修复印痕,避免了因缺陷修复所带来的二次损伤。

独立第三方掩模版厂商市场份额将不断增大

半导体掩模版行业具有显著的资本投入大、技术壁垒高、高度依赖专有技术的特点。晶圆制造厂商自行配套掩模工厂,主要是出于制作能力的考量,但随着制程工艺逐渐成熟及第三方掩模版厂商的制作水平的不断提升,自建掩模工厂的诸多弊端逐渐体现,如设备、人工投入巨大,生产环节过于复杂,成本过于昂贵等。第三方半导体掩模版厂商能充分发挥技术专业化、规模化优势,具有显著的规模经济效应。在技术水平、产品性能指标符合要求前提下,独立第三方掩模版厂商对晶圆制造厂商的吸引力不断增加。

由于掩模版承载着芯片设计方案和图形信息,涉及到芯片设计公司的重要知识产权,第三方半导体掩模版厂商作为芯片设计与芯片制造的中间桥梁,能够更好地发挥信息隔离功能,芯片设计公司更倾向于将芯片设计版图交给第三方掩模厂进行掩模生产以保证自身的信息安全。总体来看,随着技术水平不断提高,第三方独立掩模版厂商竞争优势将不断体现,市场份额将持续增加。

半导体掩模版行业具有较高的需求稳定性

由于掩模版产品在半导体生产中起到光刻模具的功能,可多次曝光、重复使用,因此掩模版产品需求不仅依赖于半导体行业的整体规模情况,更依赖于下游半导体行业的产品创新。半导体创新产品越多,掩模版需求量越大。国内半导体掩模版需求推动因素如下:

①半导体产品不断迭代创新:随着我国半导体芯片行业的国产替代推进,技术水平、工艺能力不断进步,芯片设计公司将会不断推出新的产品,对于掩模版的产品需求不断增加。

②半导体掩模版具有部分逆产业周期特性:当半导体行业处于下行周期,晶圆制造厂商的产能利用率不足时,为了提升产能利用率,晶圆制造厂商会向众多的中小芯片设计公司提供晶圆代工服务,从而生产的半导体产品类型亦会增多,相应增加掩模版的需求量;同时当下游需求低迷时,芯片设计公司将通过设计新产品刺激市场,提升销量,新产品也会带来对掩模版的增量需求。

③半导体产品种类繁多,应用广泛:与产品种类较为集中的平板显示行业相比,半导体行业的产品种类繁多、工艺多样、应用广泛,不同类型的产品应用于不同的终端场景,如消费电子、人工智能、汽车电子、新能源、工业制造、无线通信、物联网等,掩模版的需求此消彼长,不容易因某单一行业波动而产生较大的需求影响。综上所述,半导体掩模版行业具有较强抗周期行业特性,需求稳定性较高。

未来发展趋势

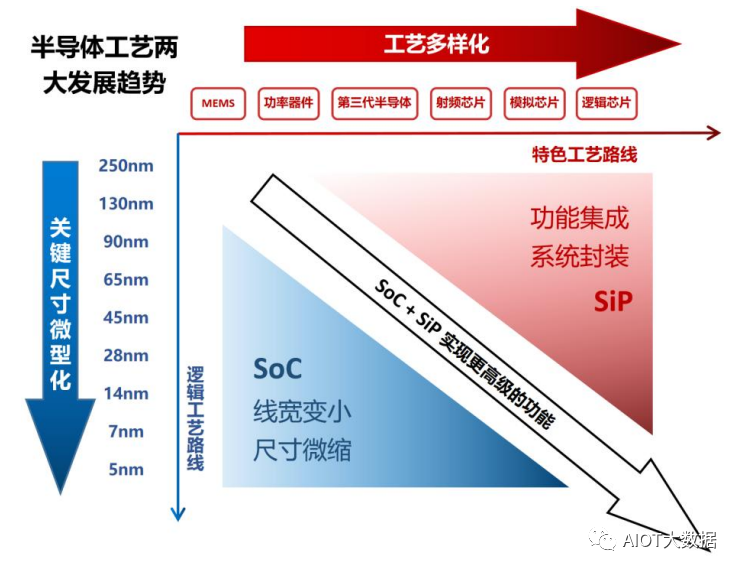

1、逻辑工艺路线和特色工艺路线是半导体发展的两大方向

逻辑工艺路线和特色工艺路线是当今半导体工艺两大方向,代表了两种产品性能提升的方式(线宽缩小与功能集成)。

两者发展趋势如下图所示:

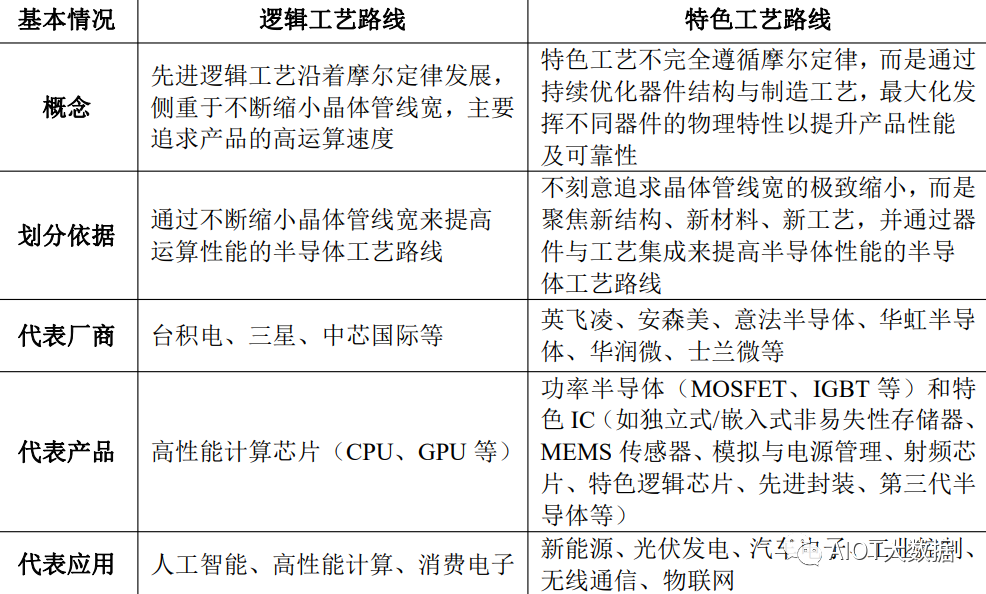

先进逻辑工艺按照摩尔定律的规律,不断追求工艺节点的缩小,从而满足对于算力和速度提高的需求,以及功耗降低的需求;特色工艺路线是指以“超越摩尔定律(MorethanMoore)”为指导,不完全依赖缩小晶体管特征尺寸,而是通过聚焦新材料、新结构、新器件的研发创新与运用,强调定制化和技术品类多元性的半导体晶圆制造工艺。特色工艺通过持续优化器件结构与制造工艺,最大化发挥不同器件的物理特性来提升产品性能及可靠性。特色工艺路线和逻辑工艺路线的相关对比如下表所示:

先进逻辑工艺与特色工艺并非是相互割裂、非此即彼的关系,随着对半导体性能需求的不断提升,先进逻辑芯片也会采用优化器件结构或集成其他工艺模块的特色工艺技术来提升性能,如应用于高性能CPU领域的3D封装技术;特色工艺芯片也会通过适当地缩小晶体管线宽来实现更高的单位性能和能耗比。

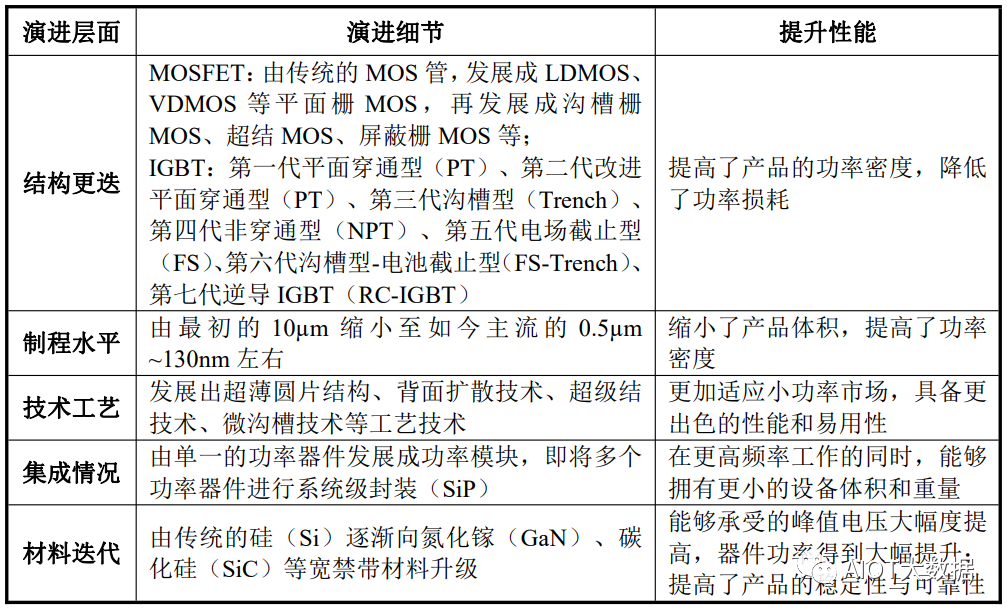

以功率半导体为例,为了提高开关频率和功率密度、降低功耗,功率半导体的制程工艺不断进步,从最初的10μm逐步缩小至目前主流的0.5μm~130nm左右;同时,在器件结构改进方面,功率器件经历了平面、沟槽、超级结等器件结构的变化,进一步提高了器件的功率密度和工作频率;而在材料方面,新兴的第三代半导体功率器件采用了碳化硅、氮化镓材料,进一步提升了器件的开关特性、降低了功耗,也优化了其耐高温、耐高压特性。功率半导体在多年的发展中,将线宽缩小与结构、材料优化相结合,实现了性能的飞跃。

由于摩尔定律不可避免地趋向物理极限,IC制造成本的不断飙升使工艺尺寸的缩小变得愈发艰难。与开支大、折旧多、功能较为单一的逻辑工艺相比,特色工艺有着更强的盈利稳定性和功能多样性。因此,特色工艺路线是未来半导体制造发展的重要方向之一。

以台积电为代表的先进制程巨头也在加快特色工艺布局,根据台积电2022年技术论坛,台积电特色工艺产能占台积电成熟制程产能的比重将会从2018年的45%提升至2022年的63%,与2021年相比,2022年12寸晶圆的特色工艺产能会增长14%;中芯国际也大力布局特色工艺,2018年中芯国际和绍兴国资委等资本共同成立绍兴中芯集成电路制造股份有限公司,专门面向MEMS、MOSFET和IGBT等特色工艺领域,致力于打造综合性特色工艺基地。

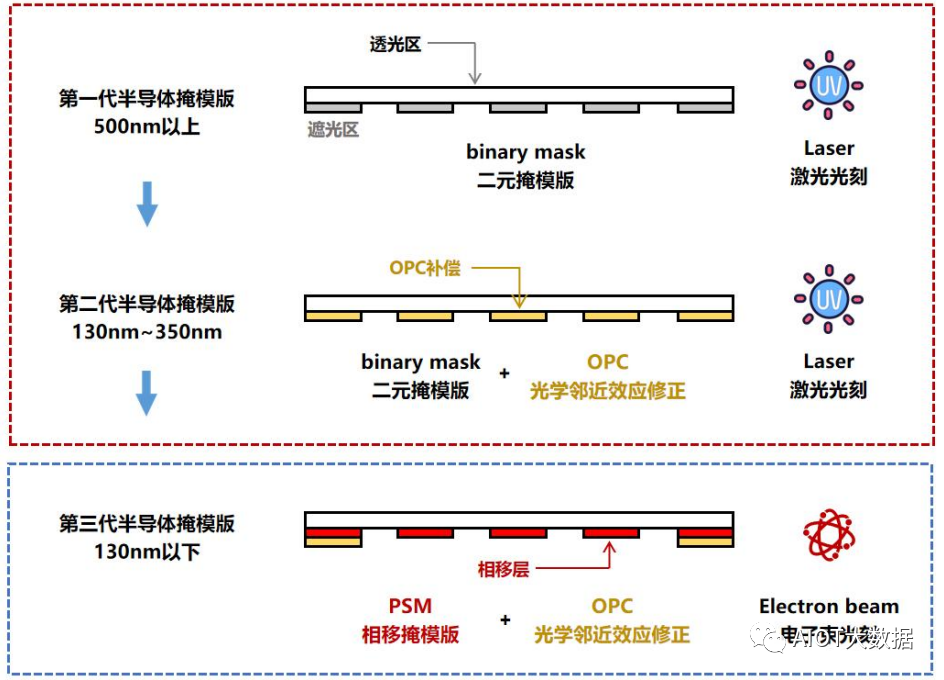

2、半导体掩模版最小线宽及精度随着半导体技术节点的进步而不断提升

半导体产品随着工艺技术进步和性能提升,线宽越来越窄,对上游掩模版的工艺水平和精度控制能力提出了更高要求。为了解决掩模版制作过程中由于线宽逐步缩小带来的诸多难题,以OPC光学邻近效应修正技术、PSM相移掩模版技术、电子束光刻技术为代表的一系列图形分辨率增强技术兴起并快速发展。

3、特色工艺半导体快速发展,对掩模版定制化要求越来越高

特色工艺半导体主要包括功率半导体(含第三代半导体)、MEMS传感器、先进封装、电源管理芯片、模拟芯片等工艺平台,近年来随着新能源汽车、光伏发电、自动驾驶、新一代移动通信、人工智能等新技术的不断成熟,工业控制、汽车电子等半导体主要下游制造行业的产业升级进程加快,特色工艺半导体行业发展迅速。特色工艺不完全依赖缩小晶体管特征尺寸,而是聚焦于新材料、新结构、新器件的研发创新与运用,强调定制化和技术品类多元性。由于下游特色工艺半导体高度定制化,平台繁多、种类庞杂、领域众多,且通常会集成多种功能,这对于第三方掩模版厂商的定制化服务能力提出了更高的要求,掩模版厂商需要有足够的技术储备才能满足快速发展的特色工艺半导体的定制化要求。

4、芯片光刻层数增加,导致掩模版的张数增加,数据处理难度加大,套刻精度控制要求更高

随着终端产品的功能日趋复杂,半导体产品的集成度持续提高,晶圆制造的工艺不断进步。随着芯片堆叠层数的增加,半导体器件与集成电路的电路图也越发复杂,晶圆表面需要光刻的图案由传统的二维电路图像发展成含有多层结构的三维电路图像,这也导致半导体掩模版的张数不断增加,CAM版图处理的难度进一步加大,掩模版的套刻精度控制也更加困难。

面临的机遇

(1)半导体受下游新兴产业推动,产线持续扩张,带来半导体掩模版的大量需求

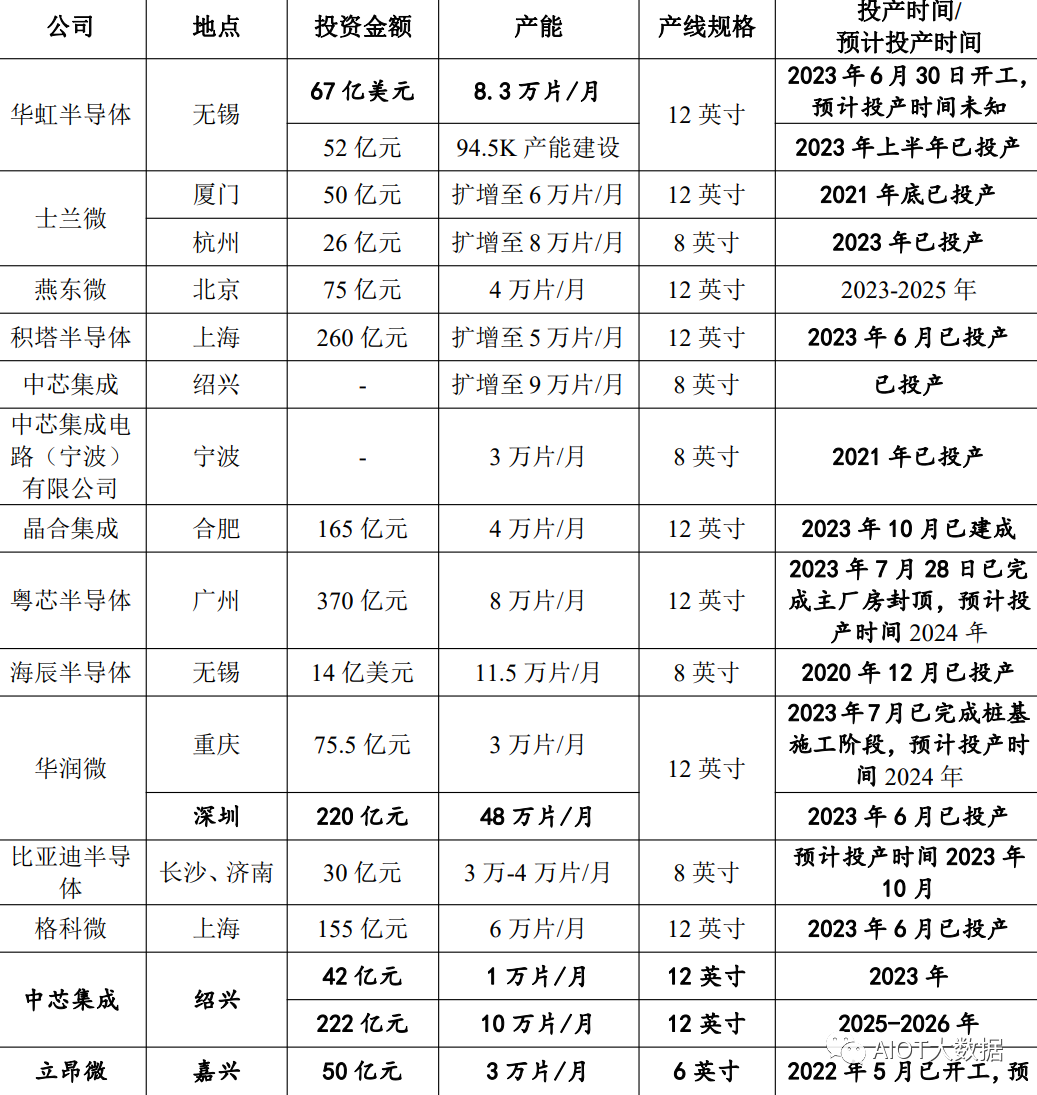

作为半导体行业可重复使用的光刻模板,掩模版产品直接需求与半导体产品的更新迭代与产线扩充息息相关。当半导体产品持续推出新工艺、新结构、新材料等新的芯片设计或者需要产线扩充时,晶圆制造厂商需要使用新的掩模版来进行半导体的大规模生产,此时就会产生开版需求。因此,掩模版的市场需求与半导体更新换代、产线扩充直接相关。近年来受新能源汽车、光伏发电、工业自动化、物联网等下游新兴产业推动,以功率器件为代表的特色工艺半导体发展迅速,不断进行产品迭代,为半导体掩模版创造了大量的市场需求。

以新能源汽车、光伏行业中的关键元件功率器件为例,根据IBS的统计,2021年中国功率器件市场规模约为711亿元,预计2025年市场规模将增长至1,102亿元,年平均复合增长率为11.58%。国内主要特色工艺晶圆厂均在积极扩充产线,带来国内半导体掩模版的配套需求大幅增加。国内主要特色工艺半导体厂商扩产情况如下所示:

上述终端行业的繁荣发展推动了半导体产线的持续扩张,相应持续带来对配套掩模版的大量需求,未来半导体掩模版市场空间广阔。

(2)特色工艺半导体受下游功能需求驱动,不断进行产品更新迭代,带来半导体掩模版的大量需求

特色工艺半导体产品随着下游应用的功能需求不断进行更新迭代。以新能源汽车为例,随着电动汽车的续航不断提升,动力电池能量密度、充电模组的功率越来越高,而单个车辆对半导体的数量、体积等因素有一定的约束,因此功率半导体的功率密度、单位性能也要求越来越高。功率半导体必须通过结构、制程、技术、工艺、集成度、材料等方面的不断进步,来实现功率密度及单位性能的提升。功率半导体的技术演进如下表所示:

半导体的结构、制程、技术、工艺、集成度、材料每发生一次迭代,就需要更换一套新的半导体掩模版。因此,在当前新兴行业的不断驱动下,功率半导体等半导体产品持续进行更新迭代,带来了大量的特色工艺半导体掩模版需求。

(3)半导体掩模版迎来国产替代机遇

半导体产业是信息技术产业的核心,也是经济发展的支柱性产业,在实现制造业升级、保障国家安全等方面发挥着重要的作用,在当前贸易摩擦、半导体产业逆全球化的背景下,加速进口替代已上升到国家战略高度。我国政府从财政、税收、技术、人才、知识产权等多个方面对半导体产业及其关键材料给予了政策支持,为半导体行业创造了良好的经营环境,有力地推动了我国半导体行业的发展。

掩模版作为半导体产业的上游核心材料,技术壁垒高,国内自产率低,长期依赖国外进口,第三方半导体掩模版市场主要被美国Photronics、日本Toppan、日本DNP等国际掩模版巨头所控制。随着新能源汽车、光伏发电、自动驾驶、物联网等新一轮科技逐渐走向产业化,未来十年中国半导体行业尤其是特色工艺半导体有望迎来进口替代与成长的黄金时期。在贸易摩擦等宏观环境不确定性增加的背景下,作为半导体核心原材料的国内半导体掩模版行业发展迎来了历史性的机遇。

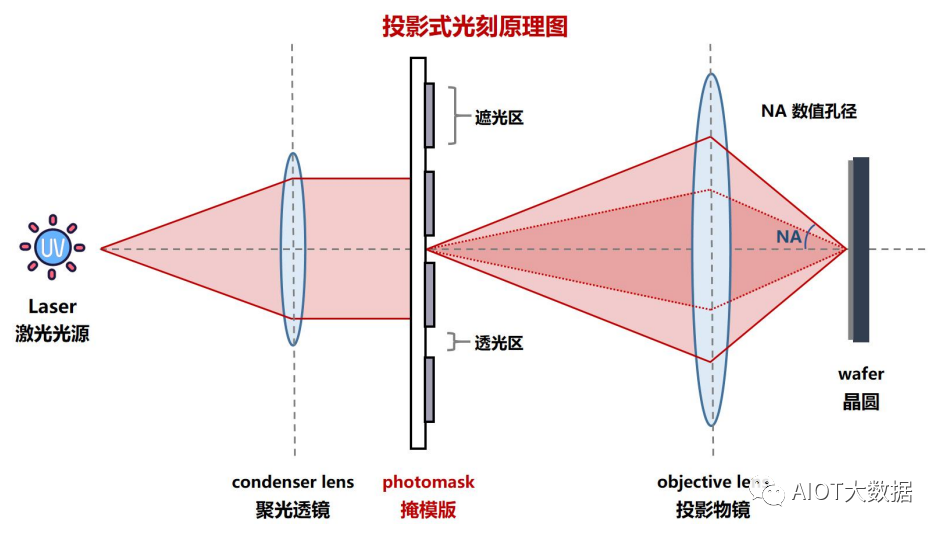

半导体掩模版研发是一个不断探索光学物理极限的过程

半导体生产工艺通常采用投影式光刻方法,在投影式光刻中,激光透过掩模版后,经过投影物镜成像到晶圆的光刻胶表面,通过掩模版对光线的遮挡或透过功能,实现掩模图案向晶圆线路图的图形转移。半导体掩模版的技术演进的过程,正是不断解决极限情况下光的干涉与衍射现象、克服物理极限的过程。

光刻方式通常根据曝光方式分为接触式光刻、接近式光刻、投影式光刻三类。其中,对于曝光面积较大、分辨率要求相对较低的平板显示类产品,通常使用接近式光刻的方法,能够实现掩模图案与基底图案的1:1复制;对于曝光面积相对较小、精度与分辨率要求极为苛刻的半导体类产品,通常使用投影式光刻方法,能够实现掩模图案与基底图案的4:1或5:1复制。

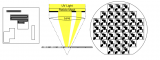

投影式光刻原理如下图所示:

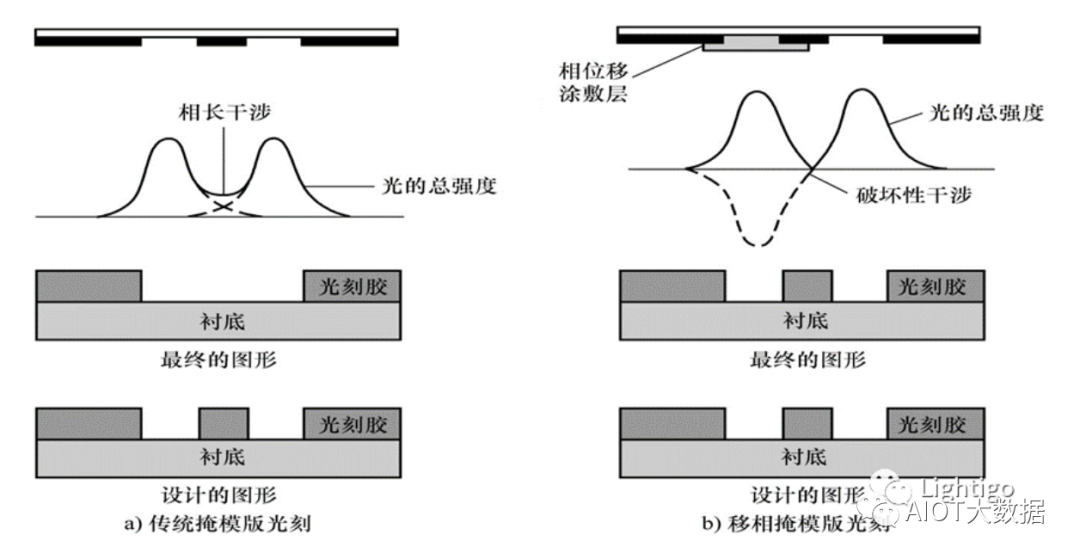

(1)光的衍射会降低曝光图形分辨率,导致CD精度降低

随着掩模版的线宽和线缝越来越小,当尺寸逐渐接近光刻机的波长时,曝光过程中就会出现严重的衍射现象。光的衍射现象是指光在传播过程中,遇到尺寸与波长大小相近的障碍物时,光会传到障碍物的阴影区并形成明暗变化的光强分布情况。这种情况在投影式光刻中尤为明显,激光通过掩模版的透光区和投影物镜后会出现显著的夫琅禾费衍射现象,导致曝光图形边缘的分辨率降低,图案边缘失真严重,CD精度大幅下降。因此,为了提高光刻环节曝光图形的CD精度,必须要对掩模图案进行光学邻近效应修正(OPC)。

夫琅禾费衍射,又称远场衍射,是波动衍射的一种,在场波通过圆孔或狭缝时发生,导致观测到的成像大小有所改变,成因是观测点的远场位置,及通过圆孔向外的衍射波有渐趋平面波的性质。

由于光的衍射造成的图像失真及OPC效果对比情况如下图所示。

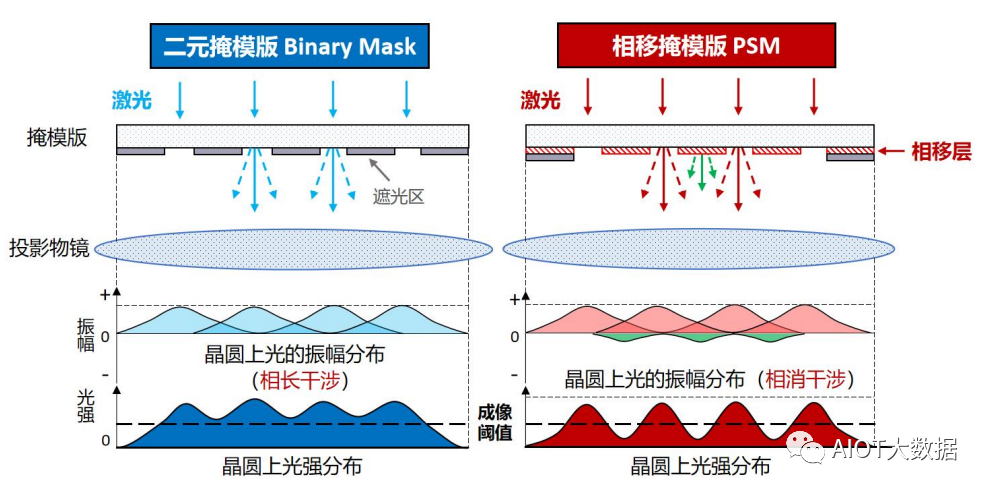

(2)光的干涉会降低曝光图形对比度,导致CD精度降低

随着掩模版图形越来越复杂、线路密度越来越大,掩模版的透光区间距离便越来越短,此时曝光过程中就会出现显著的干涉现象。光的干涉是指两束相干光相遇而引起光的强度重新分布的现象。当掩模版的透光区间位置趋于接近时,从相邻两个透光区射出的光线频率相同、振动方向相近、相位差恒定,形成了相干光。两列或多列相干光在空间相遇时相互叠加,光强在某些区域始终加强,在另一些区域则始终削弱,出现了稳定的强弱分布现象。上述现象会造成晶圆感光时遮光区域仍有曝光、透光区域光强不足的情况,导致整体的对比度降低,CD精度大幅下降,从而严重影响了晶圆的电路图形质量。当半导体的最小线宽小于130nm后,传统的二元掩模版(BinaryMask)会由于光的干涉现象而无法对晶圆进行有效曝光,需要采用相移掩模版(PhaseShiftMask,PSM)来消除曝光光束中的干涉现象,提升CD精度水平。二元掩模版和PSM掩模版的原理如下图所示:

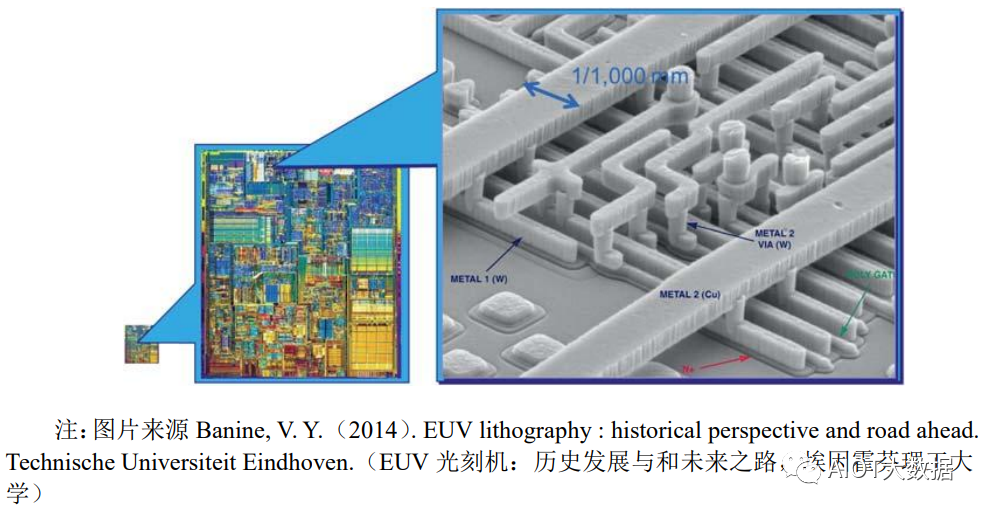

(3)半导体掩模版的套刻层数越来越多,位置/套刻精度控制难度越来越大

随着半导体功能的不断进步,制程能力的不断提升,半导体器件与集成电路的细微电路图也越发复杂,晶圆表面需要光刻的图案由传统的二维电路图像发展成含有多层结构的三维电路图像(如下图所示),这也导致半导体掩模版的层数不断增加,对掩模版的套刻精度也提出了更高的要求。

(4)电子束光刻技术

光刻机的最小分辨率由公式R=kλ/NA决定,其中R代表可分辨的最小尺寸,k是工艺常数,λ是光刻机所用光源的波长。因此,光刻机所用光源的波长越短,分辨率越高。激光光刻中,光的波长已经趋于极限,难以制造更短波长的光刻机,因此为了达到更高的分辨率会使用电子束光刻技术。

电子束光刻是利用电子束在基板上进行直写的光刻技术,相比于激光光刻能够达到更高的分辨率,用于更高端半导体掩模版的制造。目前公司已开展电子束光刻技术研究及刻蚀、涂胶、烘烤、清洗等后制程相关研究工作,已取得一定的技术成果。

(5)PSM相移掩模版技术

随着芯片设计图形的特征尺寸不断缩小,当特征尺寸达到或者接近光刻机激光光源波长的情况下,会出现明显的干涉效应,由于已经达到了曝光的分辨率极限,掩模图案转移到晶圆时会出现丢失和失真的现象,采用PSM技术可以解决这一问题。

PSM相移掩模版技术是一种利用光线的强度和相位来成像,得到更高分辨率的分辨率增强技术,其基本原理是通过改变掩模结构,使得透过相邻透光区域的光波产生180度的相位差,二者发生相消干涉,消除因干涉效应造成的光刻图像边缘模糊现象,提高光刻分辨率。相移掩模版在生产过程需要进行两次光刻图形转移过程,因此相移掩模版的生产周期会成倍增加;第一次光刻图形为主要功能性图形,第二次光刻图形为辅助图形,两层图形之间需要非常高的对位精准度和相位角精准度,存在较高的技术壁垒。

由于PSM相移掩模版制备难度大,通常应用在130nm工艺制程以下节点的集成电路关键层的光刻工艺中,较多应用在90nm节点以下大规模集成电路制造上。

关键指标:

掩模版产品的精度要求是与制程水平息息相关的,随着掩模版制程水平的提高,掩模图案绘制的最小线宽缩小,精度要求(包括CD精度、CD精度均值偏差、CD均匀性、位置精度、套刻精度)也随着线宽的缩小而越来越高,因此,制程水平是衡量掩模版产品技术水平的最关键指标。

半导体掩模版的关键指标参数包括下游晶圆最小线宽(CDSize)、CD精度(CDTolerance)、CD精度均值偏差(CDMean-to-Target)、CD均匀性(CDUniformity/CDRange)、位置精度(Registration)、套刻精度(Overlay)、缺陷尺寸(DefectSize)。

审核编辑:刘清

-

滤光片

+关注

关注

2文章

88浏览量

11448 -

TFT-LCD

+关注

关注

13文章

167浏览量

33180 -

薄膜晶体管

+关注

关注

2文章

31浏览量

10207 -

半导体芯片

+关注

关注

61文章

946浏览量

72813

原文标题:技术前沿:掩模版(光罩MASK)——半导体芯片的母板

文章出处:【微信号:AIOT大数据,微信公众号:AIOT大数据】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

华大九天Empyrean GoldMask平台重构掩模版数据处理方案

龙图光罩90nm掩模版量产,已启动28nm制程掩模版的规划

LCD段码屏铬版掩模版

2025年,全球集成电路(IC)光掩模市场总销售有望达到1508.54百万美元

***的简易工作原理图 掩模版都有哪些种类?

光刻可制造性检查如何检测掩模版质量

什么是掩模版?掩模版(光罩MASK)—半导体芯片的母板设计

什么是掩模版?掩模版(光罩MASK)—半导体芯片的母板设计

评论