2D芯片设计中通常为二阶或三阶的效应,在Multi-Die系统中升级为主要效应。考虑到此类复杂架构中存在许多相互依赖关系,上述现象并不奇怪。例如,一个裸片的散热可能会影响其旁边组件乃至整个系统的性能。此外,由于散热变得更加困难,3D设计中的热和功率传输问题会更加严重。类似地,来自一个小芯片的信号完整性问题(串扰和电磁干扰等)可能会影响整个系统。诸如此类的大量多物理场效应会妨碍Multi-Die系统的性能。

从单片式SoC转变到Multi-Die系统,需要考虑许多新的因素。在Multi-Die这个新领域,开发者无法将封装或单个裸片在整个系统中分开看待。为了获得理想的系统并加速流程收敛,从技术到裸片和封装,都必须着眼于整个系统,而且要在紧密集成的多目标分析的指导下进行协同优化。我们将这种密切配合的方法称为系统技术协同优化(STCO)。

STCO最好从构思系统之初就开始进行。从可行性研究和架构规划,到实现和签核,将多物理场效应考虑在内的裸片/封装全面协同设计方法对于设计成功至关重要。我们将在下文中进一步介绍协同设计和协同优化的重要性。

多个裸片的集成会形成相互依赖关系

为了满足高性能计算(HPC)和人工智能(AI)等工作负载密集型应用对性能、功耗和面积(PPA)的要求,市场对Multi-Die系统的需求日益增长。Multi-Die系统在单个封装中集成了多个包含不同类型电路的裸片,这是一种加速系统功能扩展的有效方法。有了关键性能指标(KPI),开发者就可以相应地规划具体的系统和组件。

单片式SoC中虽然也存在多物理场效应,但通常可以预先建模和分析,并通过设计调整来解决。而对于Multi-Die系统,这些效应不加以解决的话,会对整个系统造成更大的损害。

例如:

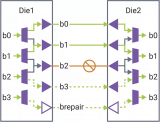

由于众多裸片通过Die-to-Die接口相互通信,系统变得更容易受到电磁干扰(EMI)和串扰等信号完整性问题的影响

散热问题上升为最主要的问题,因为系统中的所有裸片以及它们之间的互连都可能会积聚热量,从而影响系统的性能和/或时序

系统配电网络一方面要减轻EMI等影响,另一方面要提供整个芯片系统所需的电力,因此其鲁棒性至关重要

系统各个裸片的工艺变化会影响系统性能

为了解决这些效应和影响,开发者必须在Multi-Die系统的背景下进行系统分析,检查所有物理方面和相互作用,以验证和优化系统。从电气和热效应到结构力学,多种属性必须一起进行仿真,以识别系统层面的电源和信号完整性影响。为此,需要用到统一的STCO解决方案,以提供全面的设计收敛,使每立方毫米的PPA达到最优水平。

尽早了解设计权衡

STCO开始于开发者设计规划架构之初。在团队确定系统的组件以及应当如何对所有组件进行分区时,团队需要能够进行假设分析以了解设计权衡。当转向实现时,架构的粒度越细,设计收敛到签核的过程就越顺利。在早期设计阶段,可获得的信息有限;但是,系统原型设计有助于回答以下几个问题:需要多少个裸片?裸片应该如何堆叠?系统中新旧节点混用有哪些利弊?配电网络应该如何设计?可能会出现什么样的散热问题?当团队得到一个满足要求的架构时,便可从可行性研究中获取输出,并转入系统规划和原型构建。

新思科技Multi-Die系统解决方案为实现快速的2.5D和3D异构集成提供了一个综合平台以支持STCO方法,帮助回答上述的假设分析问题。该解决方案通过以下两个关键组成部分解决多物理场效应:

新思科技3DIC Compiler Multi-Die/封装协同设计和协同优化平台,提供建模功能和相关数据点,可指导开发系统版图规划以实现目标PPA。3DIC Compiler基于新思科技数字设计系列的Fusion标准单数据模型构建,提供一个完整的架构到签核平台。

设计分析和签核技术,解决静态时序、信号完整性、电源完整性、散热、寄生效应和电迁移/IR压降问题。3DIC Compiler和新思科技签核解决方案与Ansys RedHawk-SC电热多物理场技术相集成,为2.5D/3D Multi-Die系统提供多物理场电源完整性、信号完整性、热完整性和机械应力仿真与分析。

由于Multi-Die系统解决方案的各组成部分紧密集成,开发者可以及早发现并解决问题,实现更高的良率。不同的工具可以用于各个方面的分析,但如果这些工具衔接得不好,就可能会错过重要的“危险信号”,导致开发者可能不得不在接近流片时才发现问题,此时再解决问题所花费的成本要高得多。新思科技不断评估新出现的Multi-Die系统效应,并相应地增强旗下的解决方案。

总结

在Multi-Die系统中,开发者必须从系统的角度解决多物理场效应,设计和优化过程要考虑所有相互依赖关系。通过运用系统技术协同优化方法,并结合集成的可扩展协同设计、分析和签核解决方案,开发者将能够更高效地实现Multi-Die系统的PPA目标。

审核编辑:刘清

-

芯片设计

+关注

关注

15文章

900浏览量

54420 -

电磁干扰

+关注

关注

36文章

2049浏览量

104749 -

人工智能

+关注

关注

1776文章

43899浏览量

230638 -

HPC

+关注

关注

0文章

279浏览量

23419

原文标题:多物理场效应不是事儿!如何轻松搞定高性能Multi-Die系统?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

数据中心CPU芯粒化及互联方案分析-PART2

Multi-Die系统验证很难吗?Multi-Die系统验证的三大挑战

Multi-Die系统,掀起新一轮技术革命!

Chiplet需求飙升 为何chiplet产能无法迅速提高?

降低112G以太网PHY IP集成风险的5种方法

VCS:助力英伟达开启Multi-Die系统仿真二倍速

如何成功实现Multi-Die系统的方法学和技术

SLM:守护高性能计算与数据中心SoC的每一步

设计更简单,运行更稳健,UCIe标准如何“拿捏”Multi-Die系统?

爱“拼”才会赢:Multi-Die如何引领后摩尔时代的创新?

如何轻松搞定高性能Multi-Die系统?

如何轻松搞定高性能Multi-Die系统?

评论