为了满足人工智能(AI)、高性能计算(HPC)、电信、4K视频流媒体等各种高带宽、低延迟应用的需求,超大规模数据中心正在快速发展。此类应用依托新一代Multi-Die系统、AI加速器和机器学习(ML)训练集,对传输速率提出了更高的要求。为满足这一要求,以太网传输速率已从51Tb/s提升至100Tb/s,交换机传输速率也从51Tb/s提升至100Tb/s。

随着数据传输速率不断提高,全球的超大规模数据中心都在部署接口IP采用4级脉冲幅度调制(PAM-4)信号技术的端到端网络基础设施。与不归零(NRZ)信号技术相比,PAM-4能够实现更高的比特率,而波特率只有一半。尽管PAM-4信号技术存在串扰和非线性问题,增加了设计复杂性,但已成为超大规模数据中心和广阔HPC片上系统(SoC)市场上接口IP(包括112G以太网PHY)现行的信号调制方式。

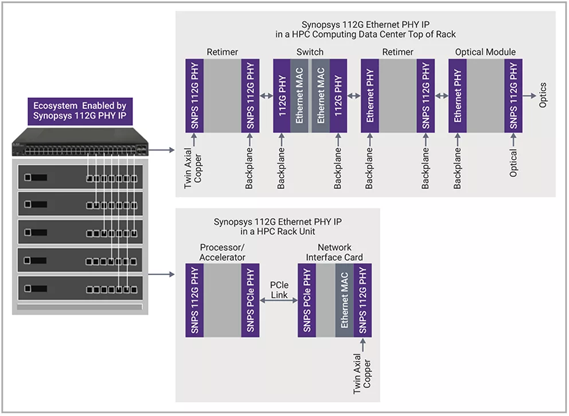

本文将进一步介绍如何在HPC SoC中优化112G以太网PHY IP的实现,并将深入探讨一些公司如何利用112G以太网PHY IP设计各种不同的高带宽网络设备和基础设施,包括AI加速器,服务器、网络接口卡(NIC)、网络和互连结构SOC、光学模块、存储设备以及重定时器。

新思科技高速SerDes IP在全球广泛应用

降低112G以太网PHY IP集成风险的5种方法

优化芯片布局并提高每个芯片边缘的带宽并非易事。芯片设计方面也面临诸多挑战,包括集成多个物理层(PHY)、物理编码子层(PCS)、媒体访问控制器(MAC),还需降低功耗和面积,从而实现更高密度的元件集成。同时,还必须通过策略性路径布线来保持信号完整性,而大量的SerDes通道需要精确实施复杂的电力传输网络。那么,开发者如何才能最大限度降低集成风险,并优化112G以太网PHY IP的功耗、性能和面积(PPA)呢?以下是需要考虑的五个要点:

硅验证的IP与出色的PAM-4信号完整性

112G以太网PHY IP需要经过硅验证,采用PAM-4信号技术,并具有出色的信号完整性。这确保可以通过多个相邻通道实现可靠的高速数据传输。对于需要稳定、高效的数据通信支持高带宽、低延迟应用的服务器SoC来说,这是一个重要的设计考虑因素。

全球生态系统互操作性

112G以太网PHY Ip应当与更广泛的数据中心生态系统实现无缝互操作,从而帮助简化各种硬件组件的集成,同时提升高需求服务器环境中的系统性能和可靠性。

完整的解决方案

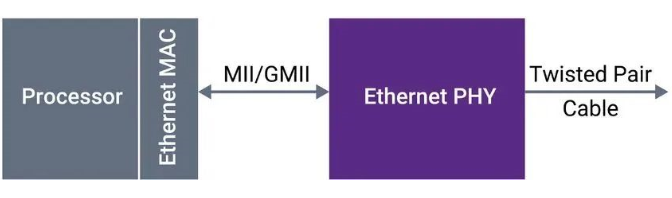

112G以太网PHY IP应当与符合IEEE标准且可配置的MAC、PCS和其他PHY构成完整的解决方案。经验证的PHY IP还应当采用先进的FinFET(鳍式场效应晶体管)工艺,并具备更高的误码率(BER)和出色的性能,以满足HPC、AI和网络SoC应用的需求。

无缝集成

112G以太网PHY IP应当经过全面的封装基板设计研究,包括利用SoC模型在先进的FinFET工艺上进行PHY和MAC/PCS版图规划和布局,助力系统开发者优化PPA并缩短产品上市时间。严格的设计前期分析和规划对于服务器SoC而言必不可少,每一纳秒都至关重要。

优化功耗和面积

PHY和控制器应当针对面积和功耗进行优化,并为短信道提供额外的功耗降低机制。均衡优化能够最大限度地提高HPC SoC效率,为高要求的应用提供强大的性能支持。

加速实现一次流片成功

面对上述挑战,Banias Labs等公司与新思科技密切合作,以尽可能降低112G以太网PHY IP的集成风险。最近,借助新思科技EDA及112G以太网PHY IP解决方案,Banias Labs的光学数字信号处理器(DSP)SoC实现了一次流片成功。其中,新思科技的112G以太网PHY IP解决方案具有延迟低、传输距离灵活的优势,并且在先进的FinFET工艺上达到了成熟水平。

Banias Labs首席执行官Amnon Rom表示:“当前,高性能计算基础设施亟需可信且完整的前沿设计解决方案。借助新思科技的EDA设计套件,我们将具有定制功能的新思科技以太网PHY IP集成到我们的芯片中,提升了系统性能,加快了产品上市速度。”

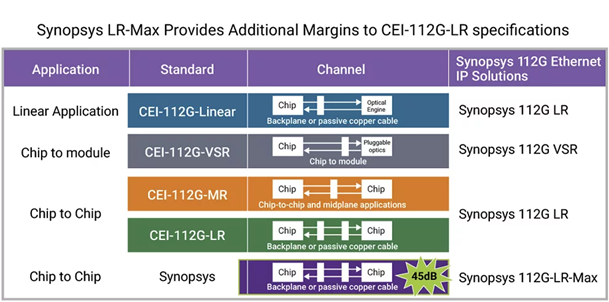

为了帮助Banias Labs等系统开发团队加速实现一次流片成功,新思科技的112G以太网PHY IP支持多种类型的互连,包括Multi-Die、共封装光学元件、近封装光学元件,以及芯片到芯片、芯片到模块和背板的互联,还支持CEI-112G-线性和CEI-112G-XSR+光学接口的长距离(LR)、中距离(MR)和甚短距离(VSR)电通道。

为进一步增强高带宽、低延迟HPC应用的可靠性,新思科技的112G LR-Max PHY IP针对CEI-112G LR规范提供了额外的裕度,与45dB通道的规范相比,误码率(BER)提高了三个数量级,同时每条通道具有独立的数据速率,可支持广泛的协议和应用。

新思科技的112G LR-Max TX超过IEEE和OIF抖动性能规格

驶入快车道:新思科技的112G以太网PHY IP成功融入服务器生态系统

作为全球数据中心生态系统的重要推动力,新思科技的112G SerDes PHY IP与Xilinx、Macom、Samtec、Key Sight、Molex、TE、Amphenol、MultiLane等众多生态系统成功实现互操作。

它可以广泛应用于数据中心生态系统的每个关键组件,包括SoC、NIC、重定时器、交换机和光学模块,充分展示了其稳健性和适应性。事实上,新思科技IP已经针对各种背板、电缆组装配置、环回和光电场景进行了测试,得到了全面的验证。

通往1.6T以太网之路

新一代高带宽、低延迟应用正在生成PB级的海量数据,需要快速准确处理这些数据。这类应用包括汽车ADAS、ChatGPT等生成式AI平台以及智能边缘设备,正在推动超大规模数据中心采用以112G以太网PHY IP为核心构建的端到端网络基础设施,将以太网速度从400G提高到1.6T。速度的提高带来了新的复杂性,芯片开发者们纷纷寻找经硅验证的低风险成熟IP。正因如此,35位客户选择了PAM-4 新思科技高速SerDes IP以加速流片成功。

在1.6T以太网方面,新思科技的224G以太网PHY IP可简化向更高数据传输速率过渡的过程。除了数据速率相对于112G翻倍外,新思科技224G以太网PHY IP的每比特功耗较上一代降低了三分之一,同时通过减少高密度数据中心的电缆和交换机数量优化了网络效率。作为首家展示224G以太网PHY IP的公司,新思科技在台积公司研讨会上的最新224G演示展示了与背板通道成功实现互操作。

结语

在塑造数字未来的高带宽应用中,强大的IP发挥着日益重要的作用。尽管112G以太网PHY IP技术成熟可靠,但在先进制程节点上设计AI加速器、SoC和服务器组件时,仍需优化PPA并最大限度地降低集成风险。

审核编辑:汤梓红

-

以太网

+关注

关注

41文章

5929浏览量

179576 -

soc

+关注

关注

38文章

4517浏览量

227672 -

服务器

+关注

关注

13文章

10097浏览量

90907 -

PHY

+关注

关注

2文章

331浏览量

53810

原文标题:新思科技112G以太网PHY IP:数据中心生态系统的新引擎

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

112G 以太网 PHY 的设计挑战和演进之路

IP101GR 单口PHY以太网收发器芯片

利用低功率以太网节电的两种方法

IP101G 以太网收发网

IP101GR 单口PHY以太网收发器芯片

RK3288搭配以太网PHY芯片需要注意哪些

新思科技收购MorethanIP,进一步扩展DesignWare以太网IP产品组合

什么是以太网PHY?集成式以太网PHY的优势分析

降低112G以太网PHY IP集成风险的5种方法

降低112G以太网PHY IP集成风险的5种方法

评论