近年来,随着摩尔定律的放缓,多芯片系统(Multi-die)解决方案崭露头角,为芯片功能扩展提供了一条制造良率较高的路径。

多芯片系统是将多个专用功能芯片(或小芯片)封装为完整的一体。为了实现更高的布线密度和带宽流量,封装技术已发展到基于硅中介层(带有TSV)或硅桥以及最近的重新分配层(RDL)来创建新的高级封装扇出和高清基板。

多芯片系统还能使产品SKU在性能扩展方面更加灵活,以满足不同的市场需求,通过在同一产品中混合和匹配各种工艺节点来优化每个功能的工艺节点,加快了上市时间并降低了风险。

但是多芯片系统的设计是一项充满挑战的任务,它需要芯片工程师具备多个领域的专业知识和实践经验。

多芯片系统成功的关键:保证可测试性

多芯片系统成功的关键之一是在各种制造和组装阶段保证系统的可测试性,同时确保在实际应用中可靠运行。因为需要采取额外的组装步骤和更复杂的焊球以及封装技术,多芯片系统所需的测试和可靠性程序超越了传统单一的设计。

因此,我们需要先对裸片进行测试,以确保在封装之前就发现所有有缺陷的芯片。如果在组装后才检测到有缺陷的芯片,那整个多芯片系统就要被废弃,这将严重影响成本。

这个测试裸片的过程被称为“已知良好芯片”(KGD)测试。

实际的组装过程会因所选择的封装技术而有所不同。

例如,“芯片优先(chip-first)”技术是先放置芯片然后在其上构建互连,这种方式无法进行“已知良好封装”的测试,如果互连出现故障,可能会导致好的芯片被废弃。

反过来,还有一种“芯片后置(chip-last)”技术,先单独构建互连,然后将芯片装配在其顶部,这可以在组装之前进行封装预测试,从而降低良好芯片被废弃的可能性。

多芯片系统可测试性解决方案可以分为几个方面:

芯片内单个模块的测试覆盖率

单个芯片(裸芯片)的测试覆盖率

封装系统的测试(芯片到芯片覆盖率)

访问裸片中的测试网络

组装后对测试网络的分层访问

使用UCIe IP确保多芯片系统的可靠性

UCIe作为新的接口标准,让多芯片系统间的通信更加流畅,使得各个组件之间能够更有效地交换信息。

作为全球领先的EDA厂商,新思科技提供全面且可扩展的多芯片系统解决方案,包括 EDA 和 IP,用于快速异构集成。为了实现安全可靠的芯片间连接,新思科技提供了完整的 UCIe 控制器、PHY 和验证 IP 解决方案。

作为 SLM 和测试系列的一部分,新思科技可同时提供完整的UCIe监控、测试和修复 (MTR) 解决方案与STAR分层系统 (SHS) 解决方案。

其中,MTR 解决方案包括用于测量 UCIe 通道信号质量的信号完整性监视器、用于自检的 BIST 以及用于冗余通道分配的修复逻辑;而SHS解决方案则充当支持行业标准 IEEE 1687、IEEE 1149.1、IEEE 1838 接口的连接结构。这一完整的解决方案能够在芯片生命周期的所有阶段对 UCIe 进行高效且经济高效的健康监控。

UCIe IP的使用为确保多芯片系统可靠性提供了一种综合的可测试性解决方案。接下来,我们就来探讨一下这种方案的优势。

UCIe接口的DFT

UCIe接口的设计可测试性(DFT)是在裸芯片测试阶段,通过在UCIe IP中实施广泛的可测试性功能,达到识别并剔除有缺陷的芯片。

这些全面且强大的测试性功能极大地提高了UCIe接口的测试覆盖率,具体包括:全面覆盖所有合成数字电路的扫描链、专门用于模块特定的内置自测试(BIST)功能、环回内置自测试 (BIST) 功能,涵盖直至 IO 引脚的完整信号链,以及可编程伪随机二进制序列(PRBS)和用户定义的测试模式生成器和检查器。这还包括错误注入功能,它可以精确地模拟并消除错误,提高系统的鲁棒性。

除了以上的单芯片测试,UCIe接口的设计还覆盖了组装后的系统内测试,包括:远端(芯片到芯片)BIST环回功能,用于测量、分析和修复通道的芯片到芯片链接BIST、二维眼图边缘分析以及各个通道测试和修复功能。

通过这种方式,UCIe接口的设计可测试性(DFT)解决方案,无论是在单芯片还是在多芯片系统层面,都能够提供高水平的测试覆盖范围,从而确保其可靠性。

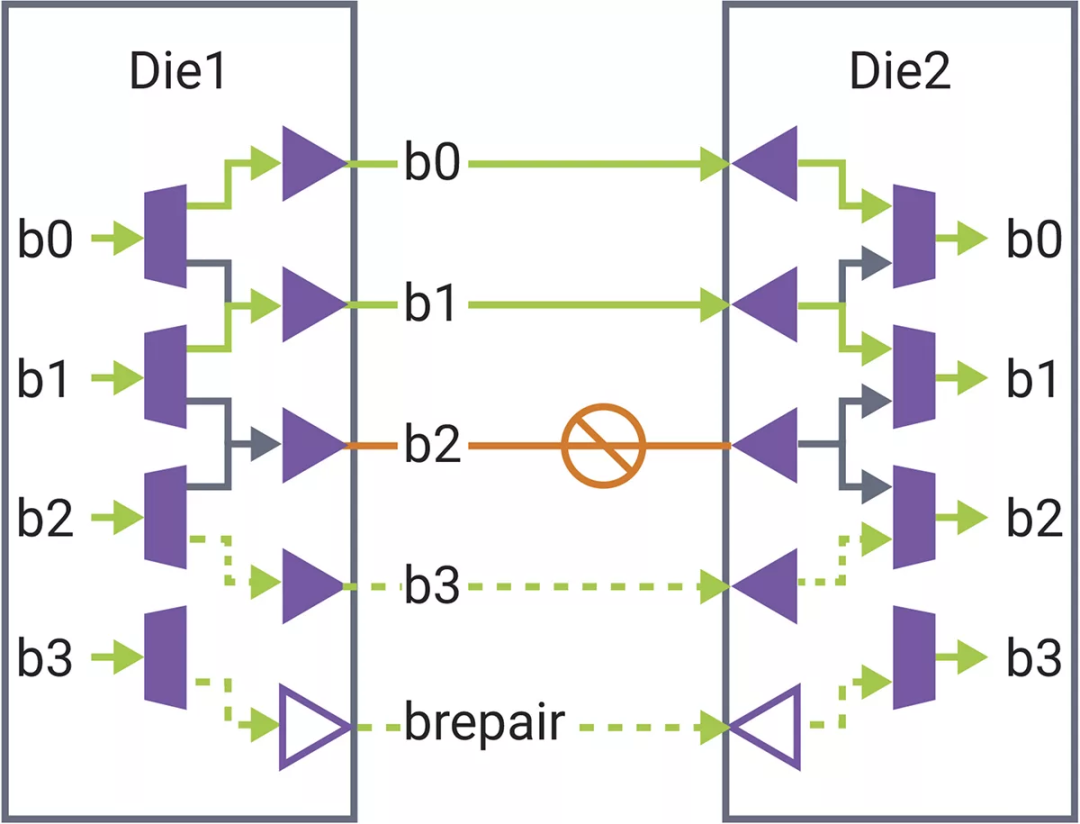

解决高级封装挑战:UCIe测试和修复的应用

先进封装可通过在硅或 RDL 中介层上进行细间距、微凸焊点以实现高密度布线。然而,在组装过程中,一些微凸焊点连接可能无法很好地形成,甚至可能会损坏。不过,不必担心,UCIe可以在组装完成后对这些连接进行测试和修复,以挽回潜在的良率损失。

这些UCIe的测试和修复工作主要是在生产测试和链路初始化阶段进行的。具体来说,在测试阶段,它们会以较低的速度对每一个独立的链路进行缺陷检查,一旦发现有缺陷的链路,就通过将数据重新路由到UCIe标准预定义的备用链路来进行修复。

为了满足高级封装技术的需求,UCIe每个方向最多可配置8个备用引脚(发送和接收),这为所有功能链路的修复提供了可能:

4个备用引脚,用于数据引脚修复,每组32个数据引脚中有2个备用引脚

1个备用引脚,用于时钟和跟踪引脚修复

3个备用引脚,分别用于有效引脚、边带数据引脚和时钟数据引脚修复

当芯片间链路上没有数据传输时,UCIe就会进行这些测试和修复工作。修复完成并初始化链路后,假设链路状态良好,数据可以顺利通过。而生成的物理层(PHY)配置(也被称为PHY修复签名)则会存储在链路两端的内部寄存器中。

然而,我们需要注意的是,如果我们在协议级别发现误码率 (BER)增加,甚至出现了数据丢失,就说明微凸焊点的特性发生了老化或退化。在这种情况下,预计链路将中断并执行新的测试和修复步骤。

有些应用对芯片间链路上的流量连续性有严格的要求,针对这些情况,可测试性解决方案在每个UCIe接收器引脚中加入了信号完整性监视器(SIM)。

图1:使用内置备用链接进行链接修复

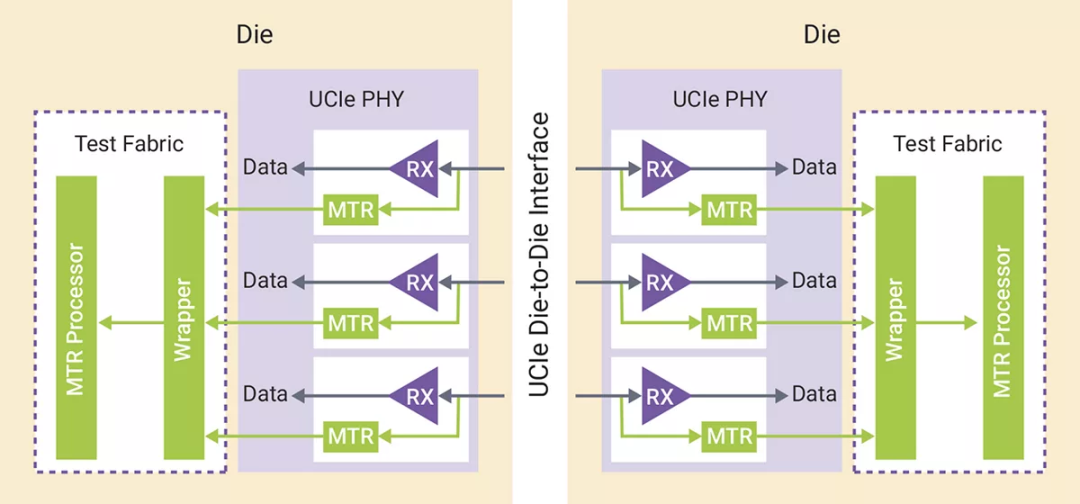

信号完整性监视器与UCIe PHY修复机制的协同作用

信号完整性监视器(简称SIM),是一种嵌入在接收器内部的微小模块。在设备的正常运行过程中,它会不断检测接收器引脚接收到的信号,以便发现信号特性的任何变化。这些变化可能会对链接的性能产生影响,或者表示链接有潜在风险,可能在不久的将来会出现问题。

每个传感器收集到的数据会被送到接口之外的一个监控、测试和维修(MTR)控制器中进行更深入的分析和处理。当把来自多个UCIe链接的数据整合起来时,我们能够立刻洞察到多芯片系统的运行状态,并且能够实施预测性的链接维护。

如果通过这一过程预见到某个特定链接可能会出现故障,则可以利用UCIe PHY的修复机制将其关闭,并将数据重新指向一个备用链接,整个过程甚至都不会中断数据的传输。

图2:UCIe链路的健康监控解决方案

利用UCIe PHY加快唤醒时间

虽然在大多数芯片间接口的案例中(例如在服务器分割或扩展中),数据流量模式在运行期间是稳定的,但在特定情况下,也可能会出现异常。在这种情况下,最好在没有流量时将接口置于低功耗模式以节省电量。通过避免测试和修复过程并依赖在先前 PHY 初始化期间创建的 UCIe PHY 修复签名,可以加速链路重新初始化。

这个概念可以进一步扩展到芯片完全断电的情况。在这些情况下,从 PHY 检索 PHY 修复签名并将其存储在片上永久存储器(闪存的 eFuse)上。存储器可以存储多个签名,涵盖不同的用例或条件,从而实现额外的用户灵活性。

使用UCIe加速芯片测试

测试时间是非常宝贵的,通过分层划分测试策略,同时进行不同芯片的测试,可以加快测试时间。通过分层连接两个芯片的测试基础设施,可以将层次结构扩展到多芯片系统中的多个芯片。这种方法允许从主芯片中的单个JTAG(或类似)测试接口访问多芯片系统中的所有芯片。

通常,将测试向量加载或读取到芯片中所需时间会成为缩短整体的测试时间的瓶颈。为了克服这一限制,设计人员可以使用现有的高速接口,例如PCI Express (PCIe)或USB等作为测试设备的接口。测试向量和命令针对该接口进行打包,并在生产测试阶段在芯片上进行解包。

许多芯片没有高速接口,但是,在测试期间,可以使用 UCIe 芯片间接口在芯片之间高速传输大型测试向量和命令。UCIe芯片间接口将高速 DFT 访问扩展到整个多芯片系统,而无需增加引脚数量,这对于 IO 和面积有限的芯片尤其重要。

总结

综上,除了UCIe芯片间接口之外,实现所有这些测试和可靠性增强功能的共同点是可以连接所有内部模块的测试、修复和监控结构。新思科技提供的UCIe控制器、PHY和验证IP解决方案,就像一只锚,确保了整个多芯片系统设计过程和最终产品的可靠性和稳定性。它不仅为设计师们提供了一套强大的工具,更打开了一个全新的设计世界,使得他们能够更好地发挥他们的创新性和创造性。

审核编辑:刘清

-

控制器

+关注

关注

114文章

17638浏览量

190247 -

接收机

+关注

关注

9文章

1240浏览量

55856 -

PHY

+关注

关注

2文章

331浏览量

53793 -

DFT算法

+关注

关注

0文章

27浏览量

7804 -

UCIe

+关注

关注

0文章

52浏览量

1992

原文标题:UCIe IP :多芯片系统可靠性的新路径

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

是德科技与HEAD acoustics成功完成新一代eCall系统互操作性测试

UPS测试系统:关键项目与应用指南

集成电路测试中的关键角色:MEDER超微型继电器

充电桩负载测试系统技术解析

怎样通过四通道气密性测试仪实现快速检测芯片的密封性

是德科技携手Alea成功验证3GPP EUTRA任务关键型测试用例

请问如何保证多片AD1278的通道之间相位一致性?

DC-DC电源管理芯片效率测试,确保高效能与可靠性的关键步骤

康谋方案 | 多源相机数据采集与算法集成测试方案

多芯片系统成功的关键:保证可测试性

多芯片系统成功的关键:保证可测试性

评论