在“如何使用LTspice获得出色的EMC仿真结果"系列文章的第1分部中,我们介绍了针对电源器件、传导辐射和抗扰度的LTspice仿真工具。在第2部分中,我们将介绍LTspice和C程序的组合,旨在帮助设计人员了解和改善有线网络信号完整性。

借助这些工具,设计人员无需多次进行实验室测试迭代,也无需重新设计硬件。文中提供了符合以下标准的仿真模型:现场总线通信(RS-485、RS-232)、高速背板(LVDS)、无处不在的USB标准以及支持通过数据线供电(PoDL)的新型单对以太网(SPE)。

为什么设计人员应关心信号完整性?

信号完整性不仅指原型机拥有正常工作的链路。即使链路看起来有效,也建议您对信号质量进行深入分析检查,原因如下:

可靠性:距离、吞吐量和环境可能会导致二进制误码率提高,达到系统纠错机制无法接受的程度。

IEEE标准合规性:符合IEEE建议可确保网络成员之间无缝互联。

EMC指令合规性:高摆率和过冲常常是不合规的原因,因为其含有高谐波成分。

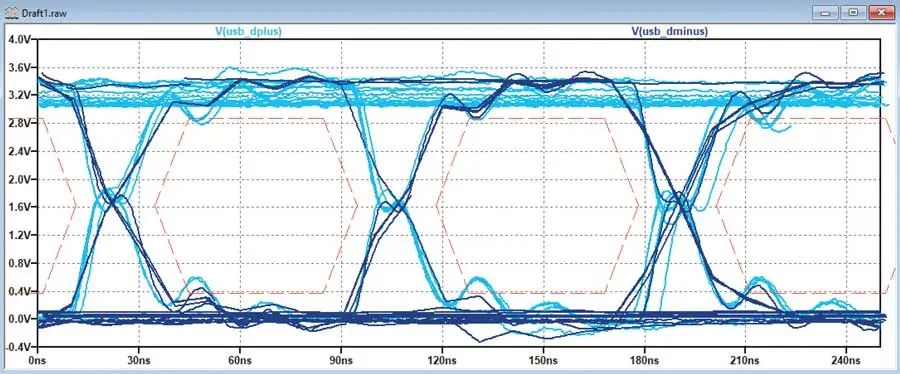

图1. 使用LTspice执行的分析示例

使用LTspice解决信号完整性问题?

本文将帮助设计人员回答若干关键问题,例如:

系统是否具有足够的信号完整性?

首先应该改善信号的哪一方面?是否应该改善信号摆率、振铃、抖动或匹配?

系统正常工作,但随着时间推移、温度和元件容差的变化,它能否可靠地工作?

阅读本文后,您应该能够:

在LTspice中实施信号完整性分析

生成、导入和使用代表性测试向量,并产生类似图1所示的分析和输出

使用多个随机参数对系统进行统计验证

执行眼图仿真

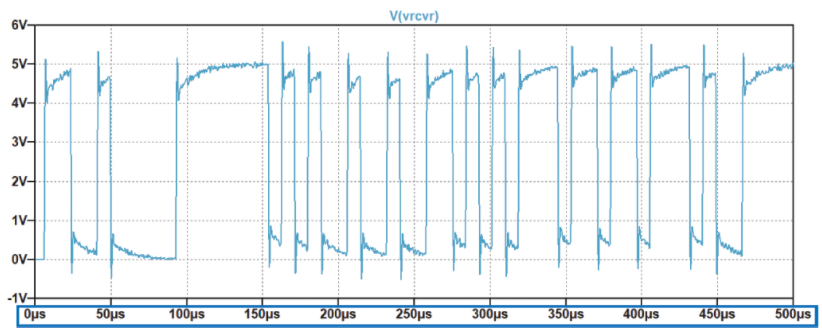

眼图提供了一种便捷的方法来评估发送器或接收器端信号是否一致。眼图是基于时间的信号表示。

这种表示方法使用余辉方式来分析大量符号,并确保信号电平、抖动和上升时间是适当的。

LTspice具有眼图分析所需的一些工具,但要执行全功能分析,需要实施一些额外的步骤。

使用测试向量生成PWL文件

LTspice提供了一种在仿真中使用测试向量的高效方法。为了更好地覆盖可能导致不一致的情况,必须使用大量数据。

一些不一致情形会在非常特殊的情况下出现,例如:

长连续位序列

非零平衡序列

来自附近其他传输通道的串扰

这意味着,假设数据是使用随机函数生成的,为了确保遇到特定的11个连续高电平,可能必须使用数以千计的符号。

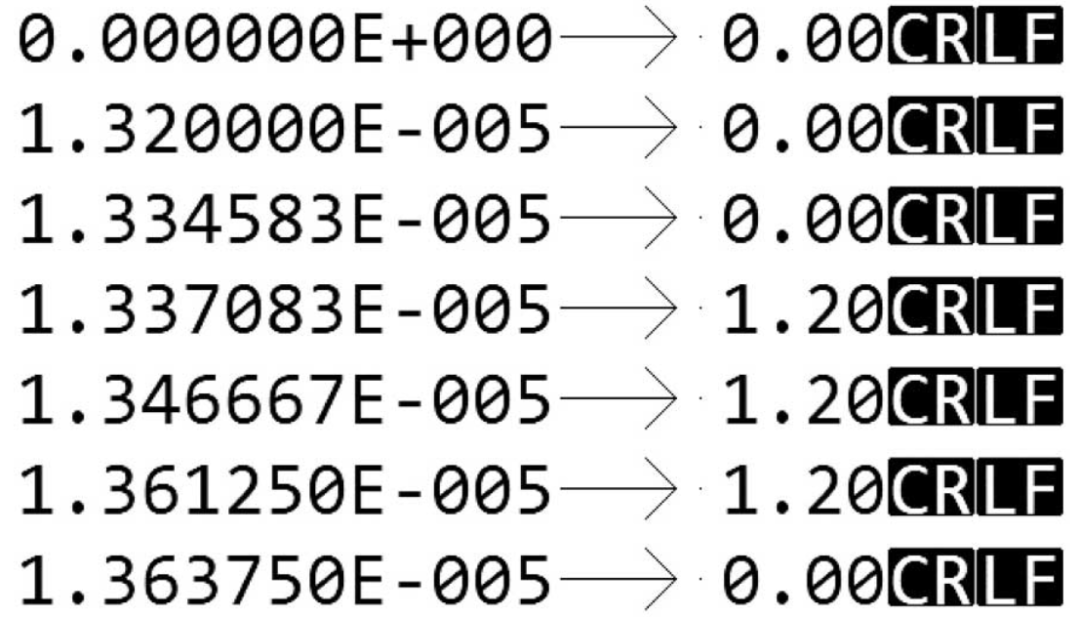

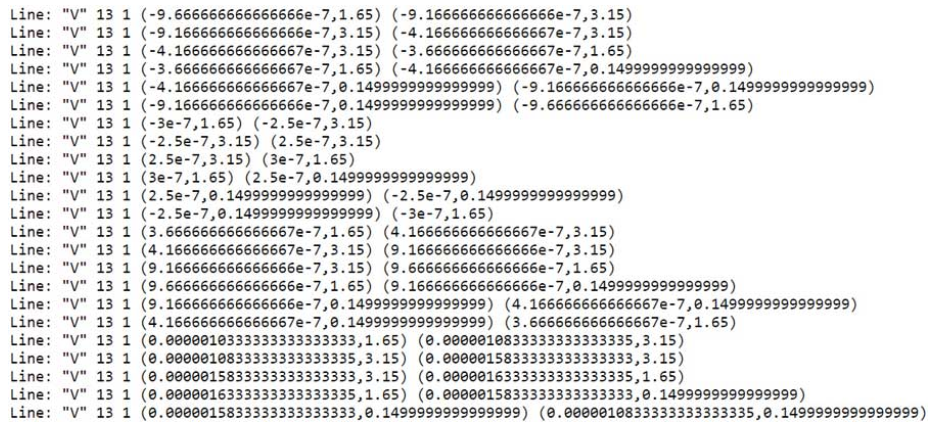

LTspice期望的PWL数据格式如图2所示。

图2. PWL测试向量的文件格式。

其中:

第一个值是时间

第二个值是输出(电压、电流、温度等)

-> 是制表符(Ascii码#09)

CR是回车符(Ascii码#13)

LF是换行符(Ascii码#10)

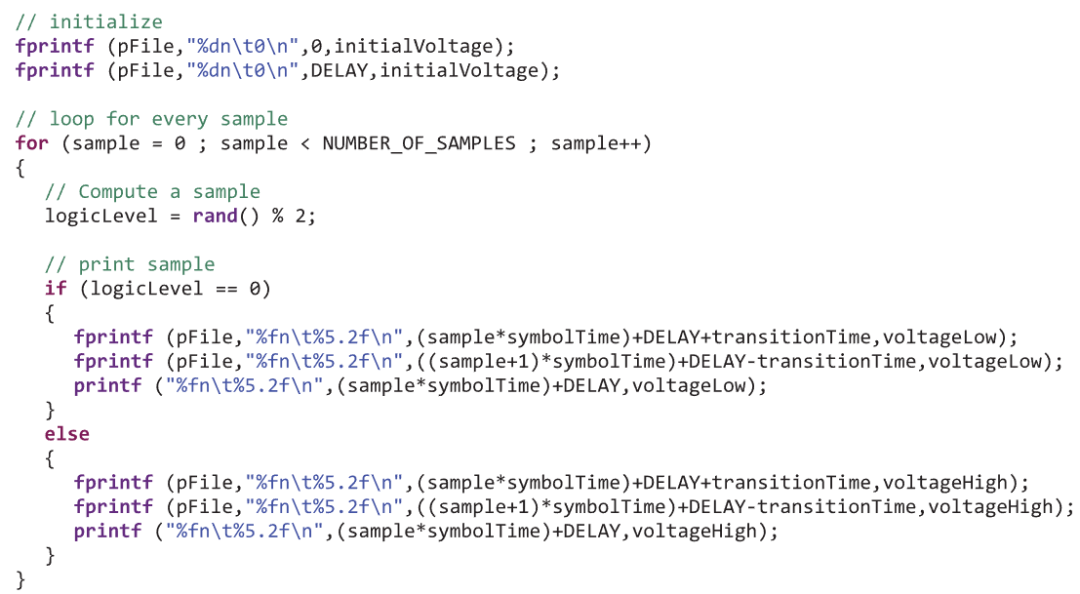

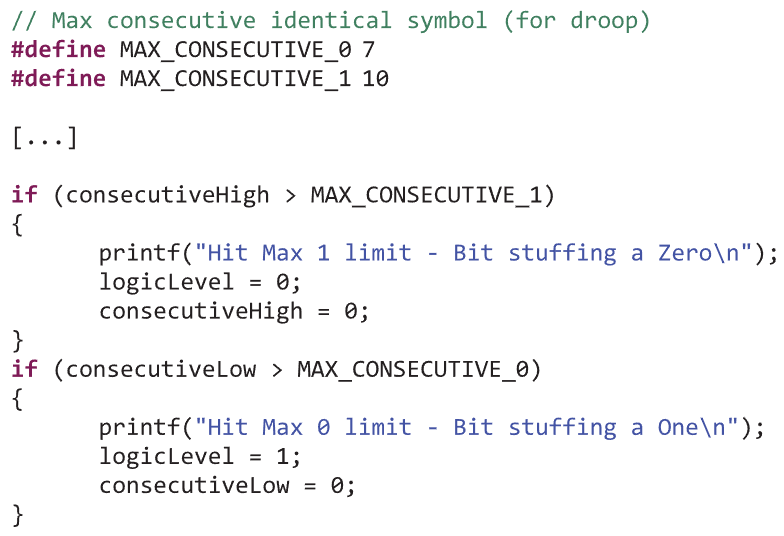

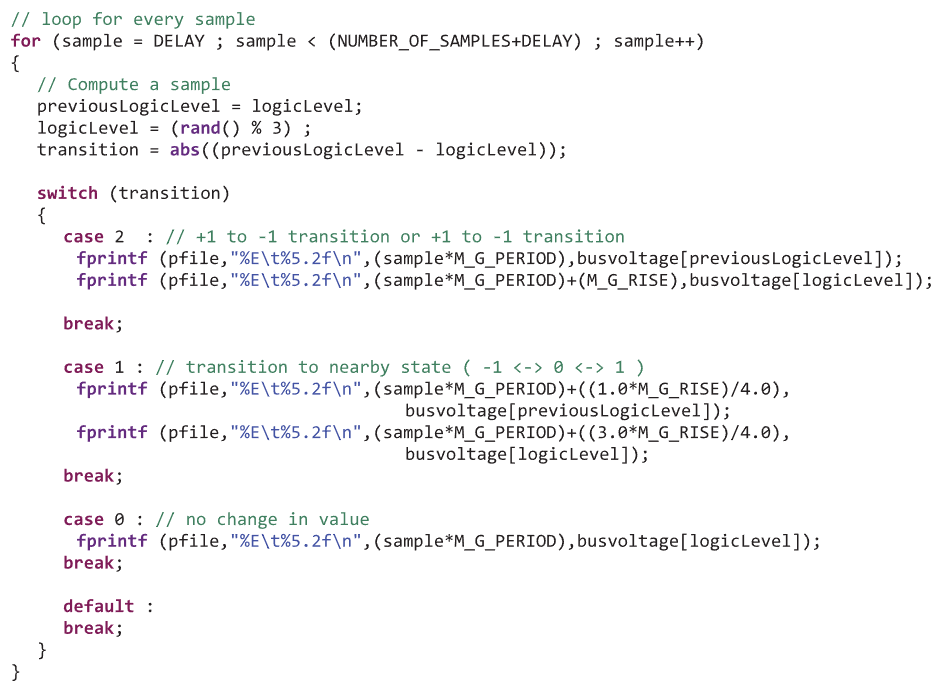

图3. 用于生成测试向量的代码摘录

生成测试向量的方案有很多。这里,我们选择C语言。

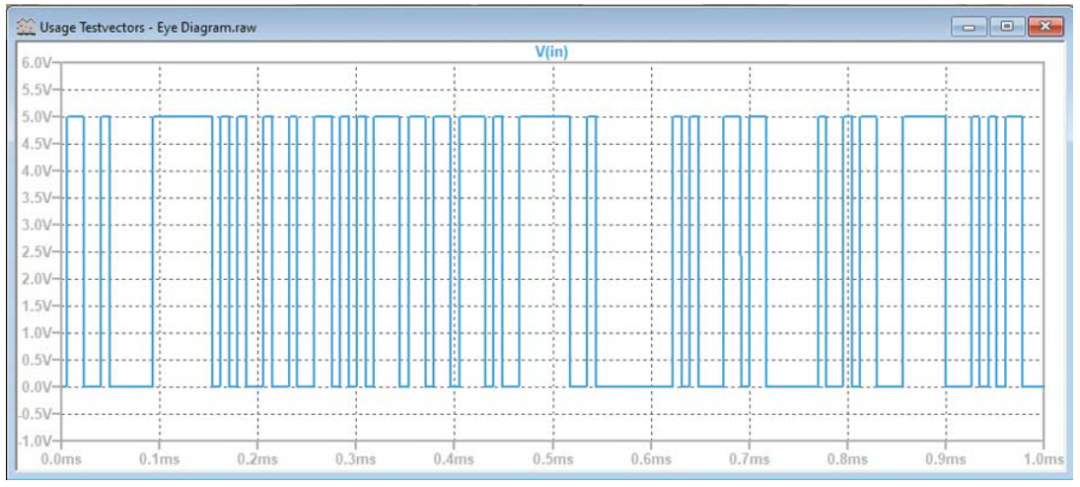

只需几行代码,就可以轻松生成大量可立即注入仿真的测试向量。图3显示了用于生成测试向量的代码摘录,图4显示了C程序生成的波形。

图4. 使用C程序生成的测试向量

有线通信中使用的概念(如位填充)可以用几行代码来实现,如图5所示。

图5. 代码参见本文提供的链接。

使用捕获的测试向量生成PWL文件

也可以使用实际数据并将数据导入LTspice。使用常规实验室设备采集数据后,只需几个步骤即可将其导入。

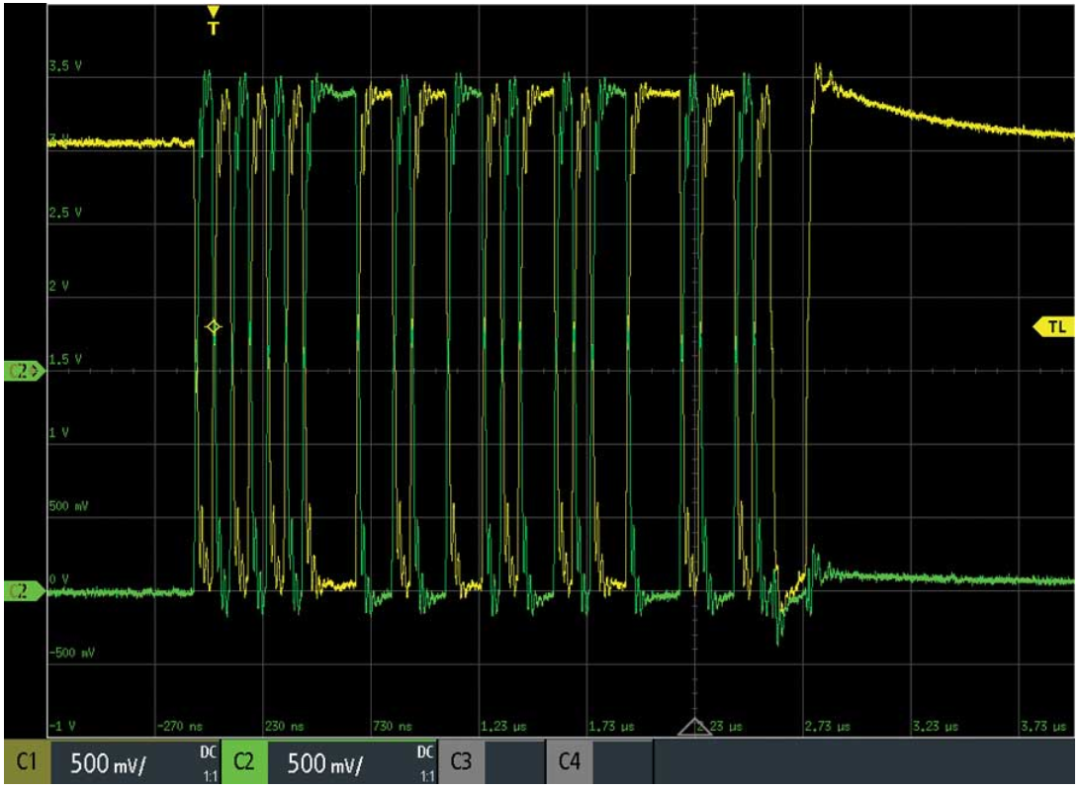

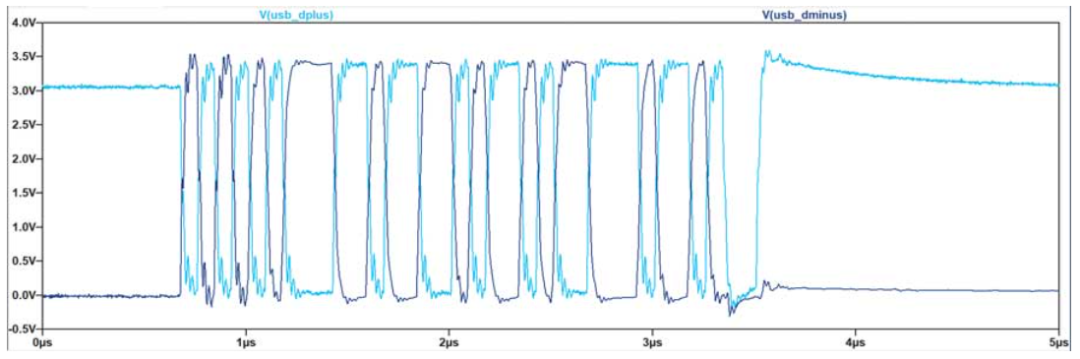

例如,图6是使用示波器捕获的USB 1.0通信信号。

图6. 使用实验室设备捕获的USB信号

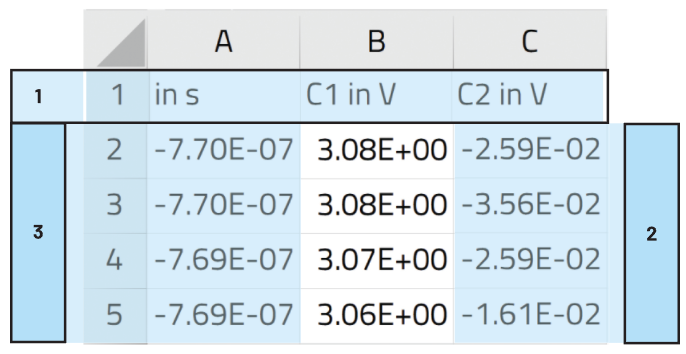

图7是示波器保存的数据集典型示例(具体格式可能有所不同,但将数据导入LTspice的规则仍然适用)。

图7. 捕获的USB信号的原始数据

要在LTspice仿真中使用此数据集,需要进行一些修改:

图8. LTspice中导入的USB信号

使用测试向量PWL文件

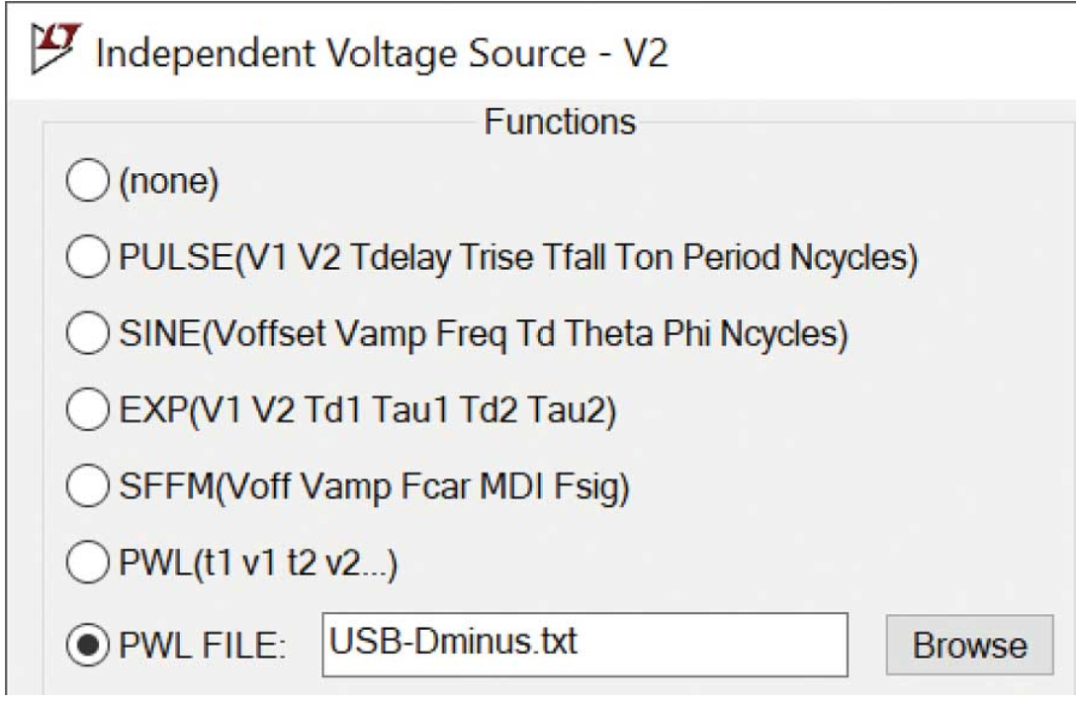

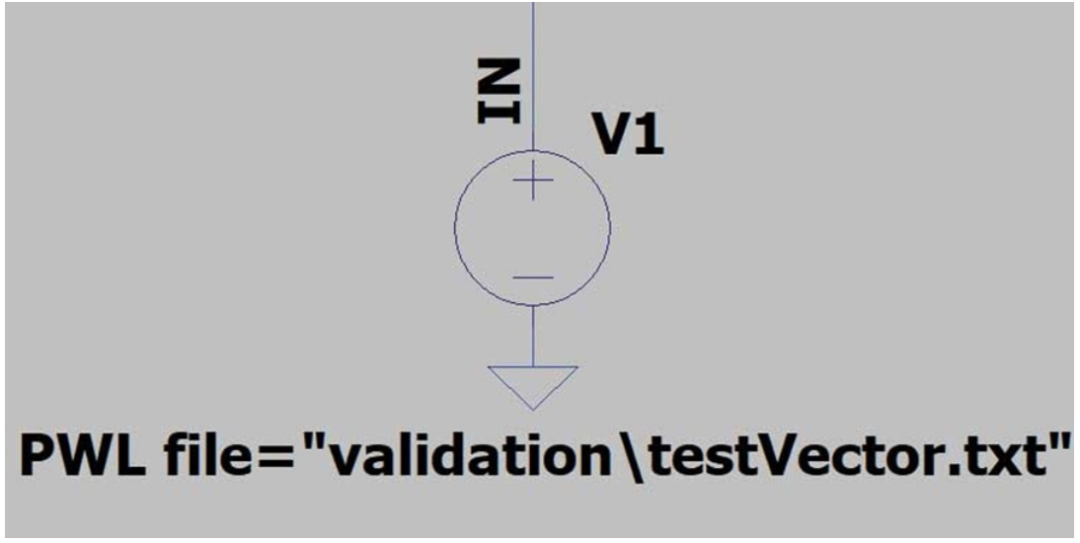

要使用生成的PWL文件,可以向设计添加电压源和文件路径,如图9所示。

图9. 电压源的PWL选项

绝对和相对文件路径均可使用,但建议使用相对路径,使仿真可移植,以便与同事分享。

图10. 相对路径示例

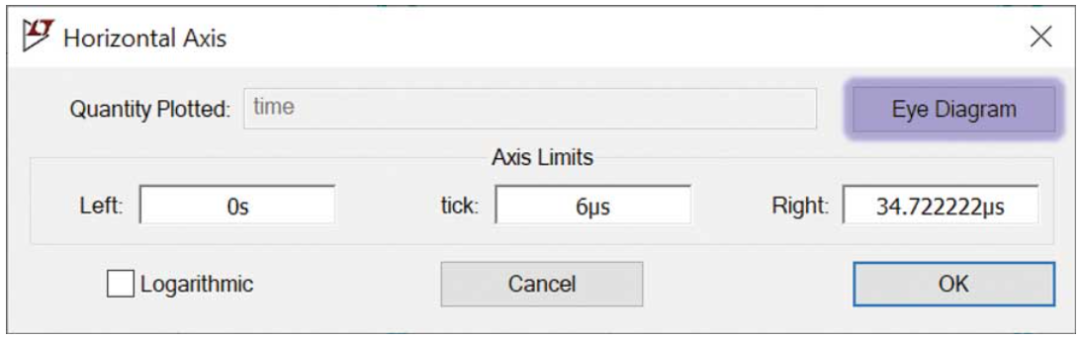

眼图功能的启用和调整

为了充分发挥LTspice这一隐藏功能的潜力,首先必须运行仿真。

图11. 右键单击该区域以启用眼图水平轴属性

仿真完成并显示信号后,右键单击水平(时间)轴。

随即弹出一个对话框,显示如图12所示的眼图按钮。

图12. 眼图选项的位置

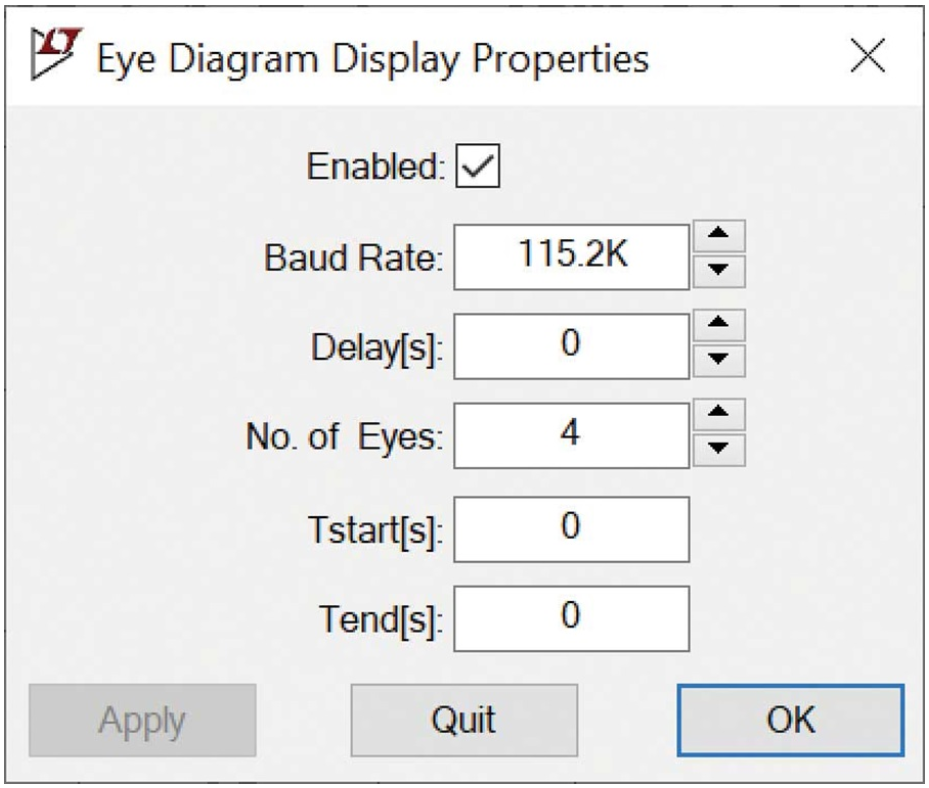

在此弹出窗口中,可以启用和调整眼图显示,其中参数通俗易懂,无需解释。

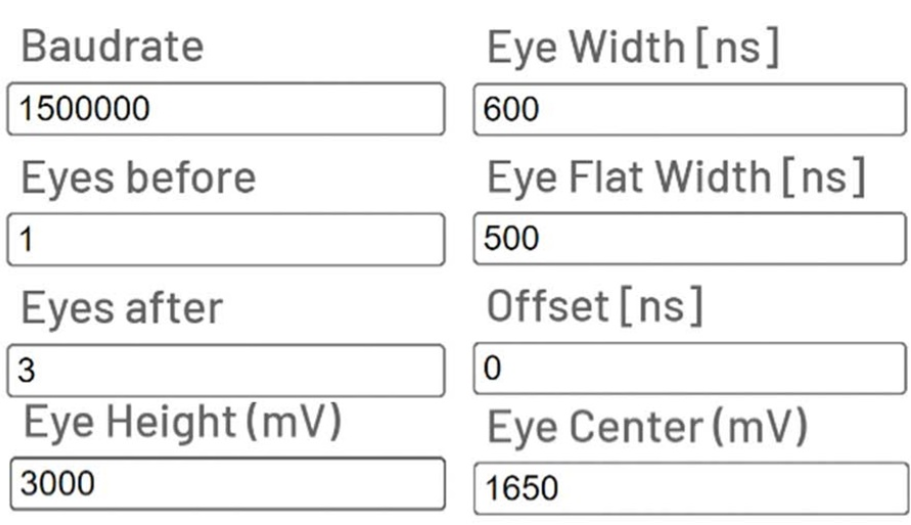

图13. 眼图的设置

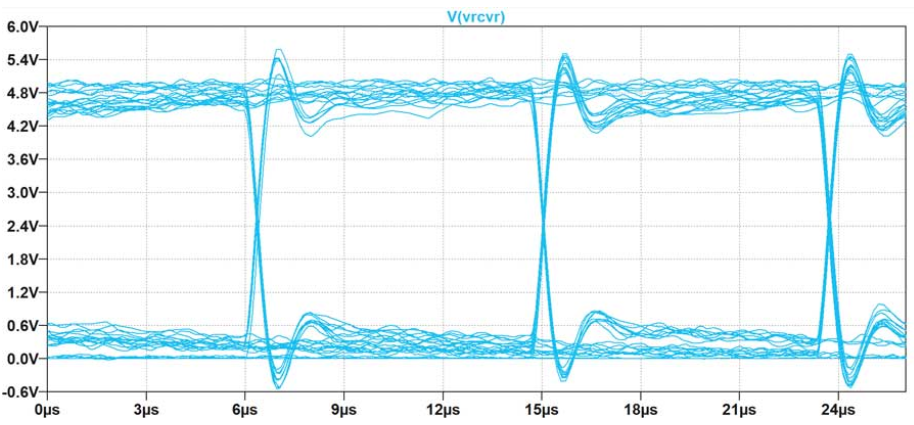

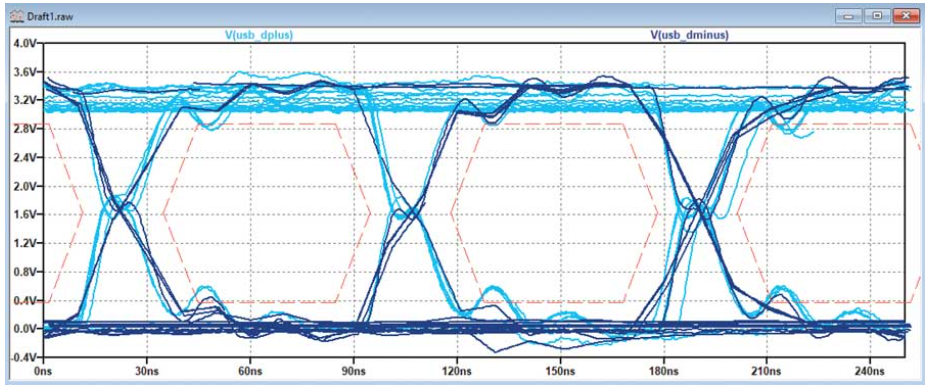

验证后,显示结果将如图14所示。

图14. 眼图显示

计算和显示眼图模板

为了简化对信号完整性的评估,可以将眼图与眼图模板相关联。眼图模板不是标准的LTspice功能,但仍然可以实现(类似第一篇文章中的EMC限值线)。

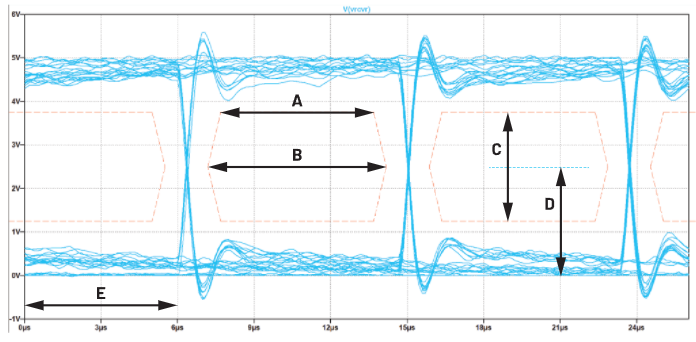

眼图规格是一个标准,因此大部分模板可以通过一组精简的变量进行评估,如图15所示。

图15. 眼图和眼图模板

下面的列表给出了眼图模板中字母A到E的定义:

A:眼图平宽,在某些模板定义中它可以低至零。

B:眼宽,评估最大抖动、摆率和波特率等参数的关键。

C:眼高,根据您是在电缆的近端还是远端评估此参数而有所不同。

D:眼图中心,定义眼图的中心电压。

E:延迟,仅在LTspice中使用,以便在绘图窗口内移动信号。

生成眼图模板

在本系列文章的第1部分中,我们说明了如何使用绘图元件在FFT频谱上显示EMC限值线。在本文中,我们将展示如何使用相同的工具来绘制眼图模板。

与生成和添加EMC限值线相比,眼图的生成更为复杂。对于眼图,我们使用含有JavaScriptP2的网页来生成眼图定义,然后可以将其粘贴到LTspice信号显示的绘图设置文件(*.plt)中。如图16所示,工程师可利用此JavaScript程序完成其设计。

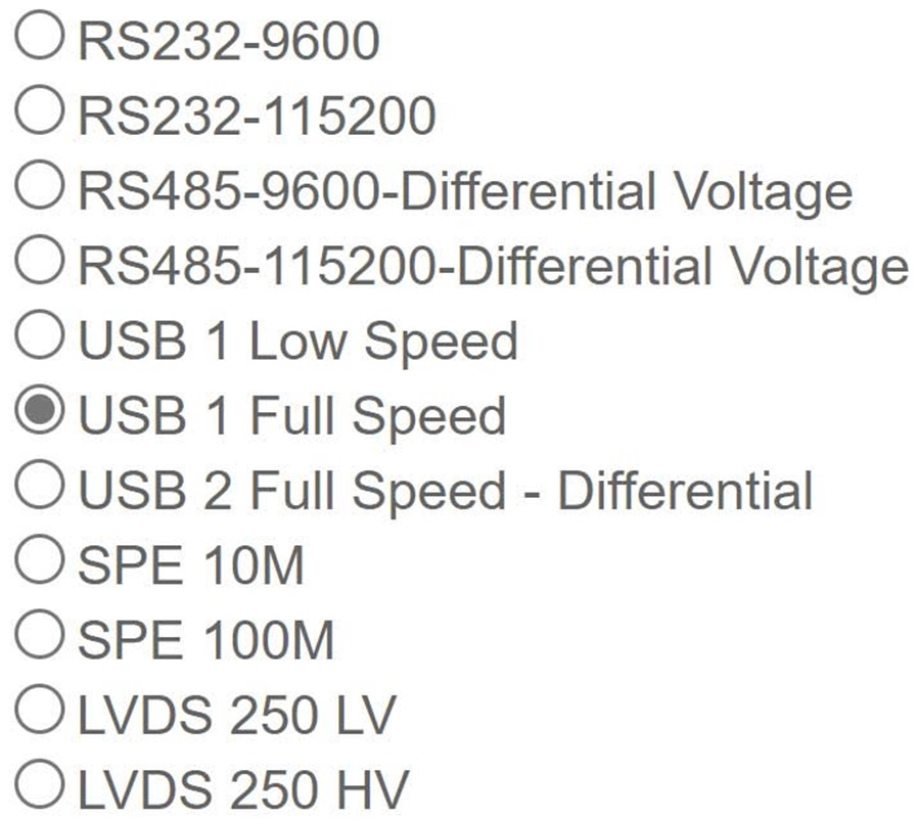

图16. 眼图生成器的预设

常见有线接口标准的眼图定义已作为预设提供。单击每个单选按钮,字段会自动填充典型值。

使用提供的字段也可以微调或实现您自己的眼图定义。

图17. 眼图模板输入字段

单击更新按钮就会生成相应的绘图设置命令。您可以按照本系列文章第1部分所述的方法,将这些行添加到绘图设置文件中。

图18. 由网页生成的绘图设置

为了获得比较理想的显示效果,可能需要调整要绘制的眼图数量和LTspice延迟设置,如图19所示。

图19. 由网页生成的绘图设置应用于波形

评估容差范围内的一致性

设计中使用的元器件具有较宽的容差,我们可以通过计算检查这些容差是否会有问题。但是,当设计包含数百个元器件时,使用纸笔或电子表格等手动方法会非常耗时,并且可能无法捕获重要参数。对于某些器件,可以使用更窄的容差,但如果为整个物料清单挑选低容差元器件的话,将会带来价格和供货问题,而且不会考虑老化或温度相关性的影响。

为了在容差范围内验证设计,spice及其扩展LTspice提供了几个非常棒的工具。

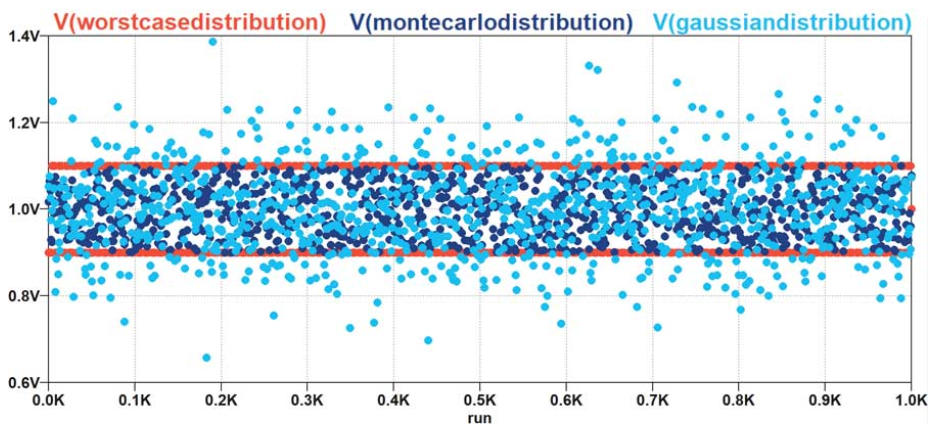

以下部分介绍在LTspice中使用蒙特卡罗和高斯分布进行容差分析和最差情况分析的方法。

图20. 三种主要方法的随机值分布

高斯、最差情况和蒙特卡罗方法的通用测试电路

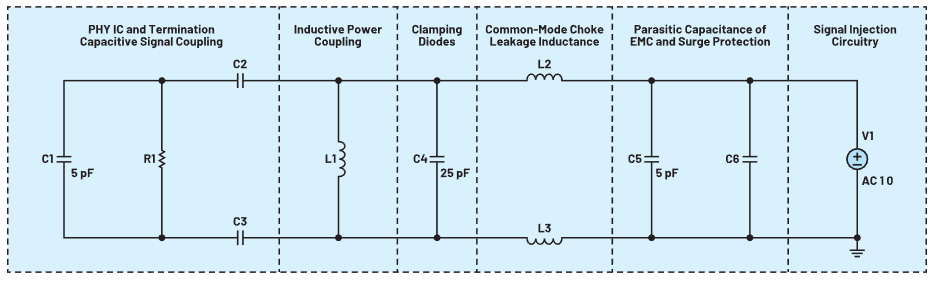

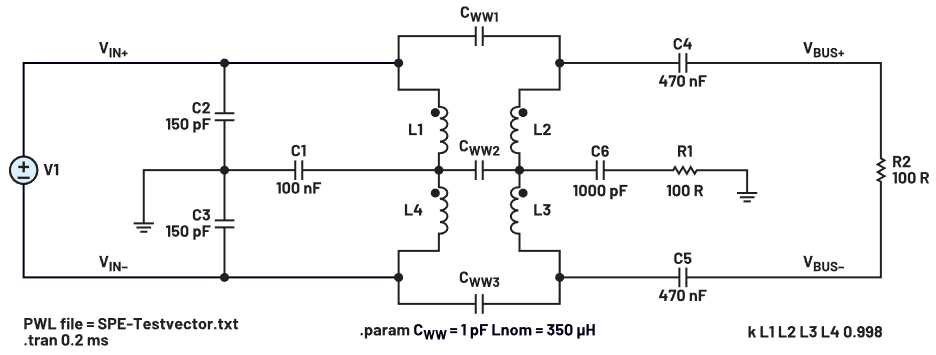

为了比较这些方法在实际用例中的相关性和穷尽性,我们选择了以下基于Graber4工作的示例。此设置显示了SPE 10Base-T1L标准(10SPE)物理层或MDI的仿真电路。

图21所示的仿真电路包括100 Ω ±10%的端接电阻,用于ADI公司的 ADIN1110或ADIN1100 10BASE-T1L以太网PHY/MAC-PHY。

图21. 高斯、最差情况和蒙特卡罗方法的通用测试电路 — 基于参考文献

信号耦合电容、功率耦合电感、共模扼流圈和其他EMC保护元件均进行建模仿真。对于某些元件,我们添加了建议的元件值和容差范围。

回波损耗图的语法为:

(100+1/I(V1))/(100-1/I(V1))

蒙特卡罗仿真

蒙特卡罗仿真从仿真电路中每个指定元件的容差范围中取一个随机值。对于电路仿真而言,元件容差范围内的所有值都有相等的概率。

LTspice内置一个使用方便的蒙特卡罗功能,其语法很简单。

例如,要创建一个容差为10%的100 Ω电阻,就需要使用以下语法:

{mc(100R, ToIA)}

.param ToIA = 0.10

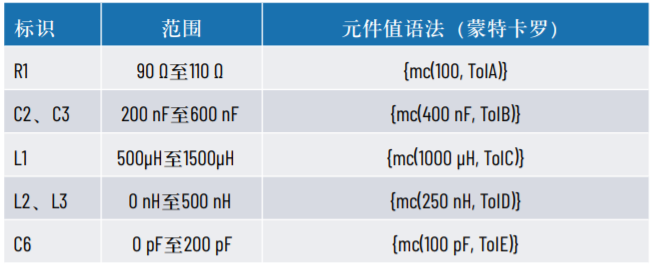

表1. 使用蒙特卡罗方法定义元件值和容差

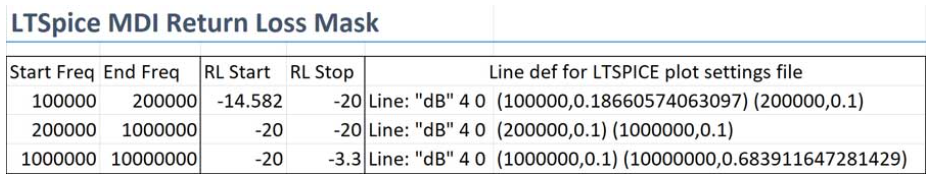

图21所示的电路可用于仿真回波损耗,它衡量所有可能发生的信号反射。

回波损耗是由电缆链路上所有位置的阻抗不匹配引起的。回波损耗以分贝为单位,对于10BASE-T1L中采用的高数据速率或长电缆距离(1700 m)通信尤为重要。

要将MDI回波损耗限值线添加到图中(图23中所示的红线),请单击Plot Settings(绘图设置)菜单中的Save Plot Settings(保存绘图设置)。

使用标准文本编辑器打开.PLT文件。复制并粘贴Excel文件所示的线定义语法(图22)。

图22. LTspice绘图设置文件的线定义

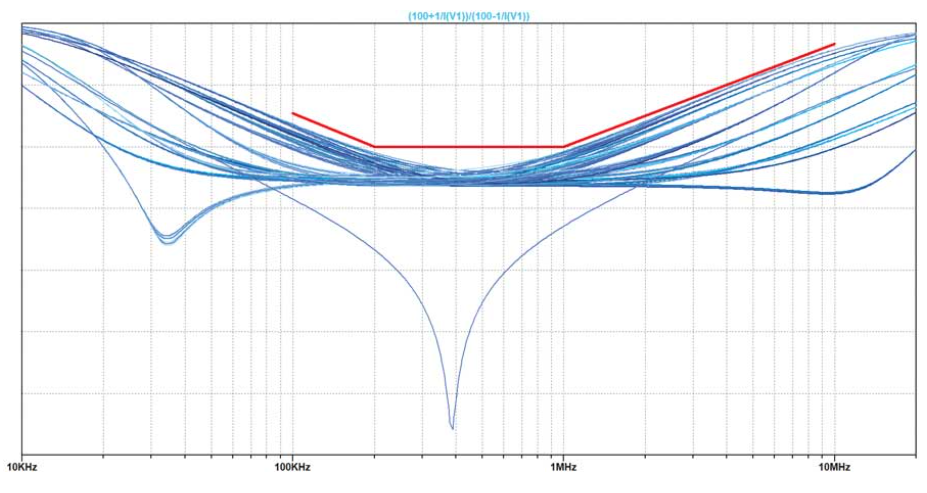

图23. SPE终端的差分回波损耗:蒙特卡罗分布参数的128次运行

要在仿真中得到理想的图形,请右键单击波形,然后单击Don'tPlot Phase(不绘制相位)按钮。

关于蒙特卡罗仿真的结论

蒙特卡罗仿真是评估电子设计在其容差范围内的合规性的重要方法,很可能将满足大多数设计人员的需求,同时仿真运行次数合理。

最差情况仿真

最差情况仿真功能不是LTspice的内置功能。但是,您可以用所需函数来模拟最差情况,如Joseph Spencer和Gabino Alonso的文章所述。根据最差情况执行仿真需要.func binary(run,index)和.func wc(nom,tol,index)函数,您需要将它们作为SPICE指令放在LTspice原理图中。

.func binary(run,index) floor(run/(2**index))-2*floor(run/(2**(index+1)))

.func wc(nom,tol,index) if(run==numruns,nom,if(binary(run,index),nom*(1+ tol),nom*(1-tol)))

为了使用这些函数,您需要:

使用numruns声明所需的仿真运行次数,这些运行次数应覆盖每个进行最差情况分析的元件的最大值、最小值和标称值。运行次数为2N+1,其中N等于与元件容差相关的不同索引的数量。对于图21,运行次数为129,因此语法为:

.param numruns = 129

您必须声明以下表达式,而不是使用元件的常规值:

{wc(100R, 0.1, 0)}

其中:

100R为标称值

0.1为容差(此处为+或-10%)

0为要改变的参数的索引,下一个要改变的元件将采用索引

使用下表中的表达式(而不是静态元件值)运行图21所示的仿真电路:

表2. 使用最差情况方法定义元件值和容差

结果显示在图24所示的波形图中。

通过编辑绘图设置文件来添加MDI回波损耗模板限值线,如前文所述。

关于最差情况分析的结论

Steve Knudtsen简要说明3了系统设计使用最差情况分析的优点和局限性。

最差情况分析是一种常见方法,其中会将元件参数调整到其最大容差极限。

最差情况方法的局限性包括:结果与通常观察到的结果不一致;要观察系统表现出最差性能,将需要装配非常多的系统。

如果系统针对最坏情况进行设计,那么选择的元器件可能会很昂贵。

然而,将最差情况与蒙特卡罗或高斯仿真结合使用可以产生有价值的系统见解。

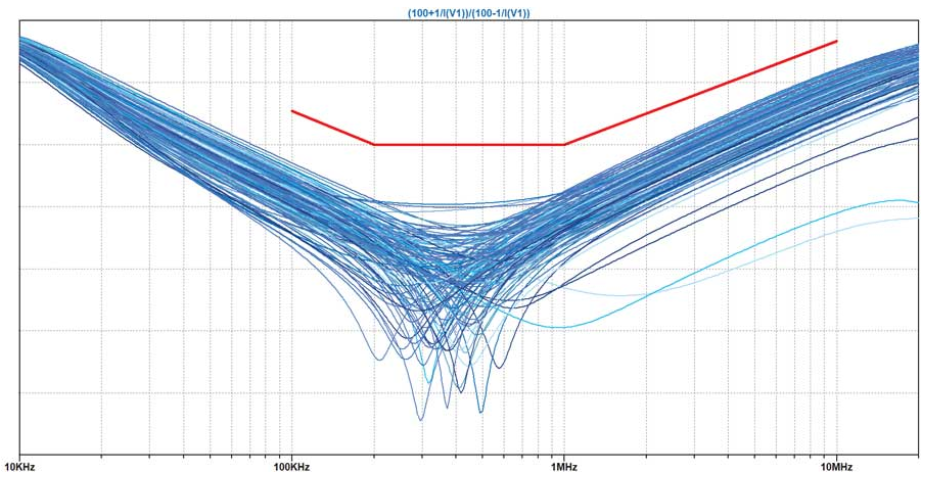

图24. SPE终端的差分回波损耗:最差情况分布参数的128次运行

当仿真时间很长且标称行为已经得到验证时,最差情况分析非常适合对系统行为进行总体验证。

高斯仿真

LTspice内置一个高斯函数,其中心值出现的概率较高。此高斯函数的语法很简单。

{nominal_value*(1+gauss(tolerance/σ))}

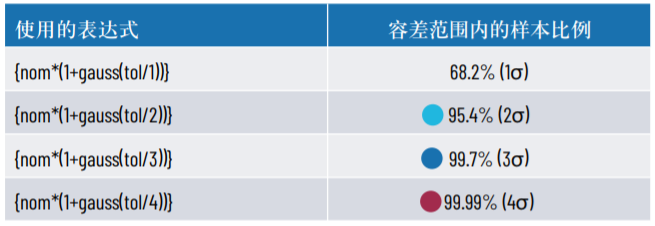

要根据高斯分布的标准差参数σ进行调整,可以使用表3中的表达式。

表3. 使用高斯分布方法定义元件值和容差

或者使用更形象的表示:

图25. 样本的高斯分布与σ的关系

例如,要创建一个容差为10%的100 Ω电阻,并且值在容差内的概率为4σ,您需要使用以下语法:

{100R*(1+gauss(ToIA/4))}

.param ToIA = 0.10

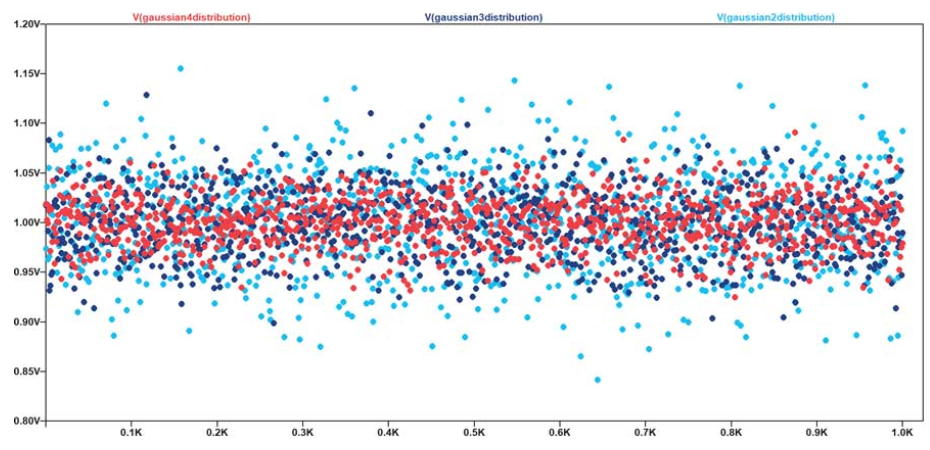

图26提供了图19所示仿真运行128次的结果,其中高斯仿真如图19所示,高斯分布参数使用4σ。

图26. SPE终端的差分回波损耗:高斯分布参数的128次运行

关于高斯分布方法的结论

高斯分布通常是仿真电子设计变化的重要方法。

参数围绕标称值的高斯分布仍然是研究容差影响的较自然的方法。

遗憾的是,这种方法代价不菲。为了详尽无遗,仿真运行次数需要非常多。

此分布还会选取容差范围之外的值,省略元器件制造商执行的排序和分仓操作。

在10BASE-T1L链路分析中的应用

使用10BASE-T1L以太网标准的话,可以省去几条现场总线。同一电缆既可用于传统现场总线,也可用于10BASE-T1L;它是一种简单的平衡铜线对,用于全双工通信和为终端供电设备(PD)供电。虽然可以复用同一电缆,但必须更换物理层通信收发器(PHY)和无源元件以满足10BASE-T1L标准。

LTspice中的大多数10BASE-T1L信号完整性验证可以使用类似形状的信号进行。

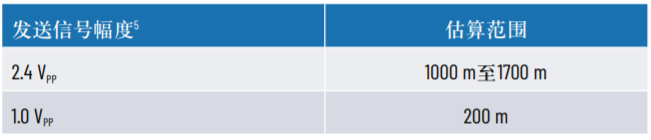

表4. 单对以太网的范围取决于发送信号幅度

使用的编码为PAM,用于脉冲幅度调制3级。根据端点期望的覆盖范围和能力,发送信号幅度可以调整为1 V或2.4 V。

在电缆侧,-1至+1转换的信号上升时间为53.33 ns,下降时间相同。

将摆率视为恒定,因此0至1、1至0、-1至0和0至-1转换的标称转换时间应为26.66 ns。

为了生成这样的测试向量,我们将使用图27中的代码。P3它将以PWL格式输出含有5000个PAM3符号的测试向量。

将此测试向量输入到原理图中,我们就能验证各种参数,例如最小耦合、绕组间电容等等。

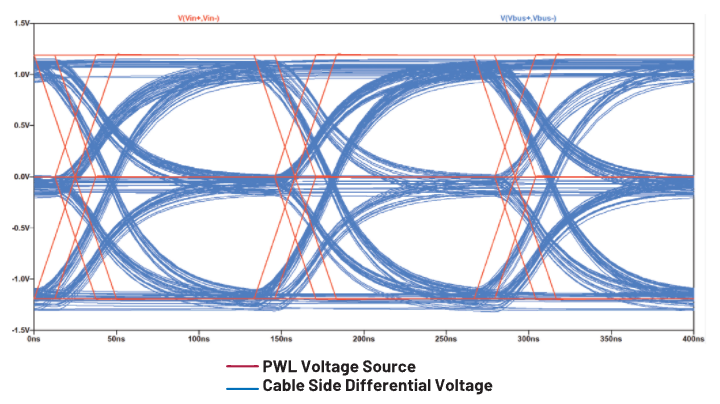

图28、29和30分别显示了10BASE-T1L链路基于变压器的端接、PWL源电压文件的输出以及PWL电压源和电缆侧差分电压的眼图。这可用于10BASE-T1L标准合规性测试。

图27. 用于生成PAM3测试向量的代码摘录

图28. 基于变压器的端接,使用PAM3 PWL测试向量

图29. PWL电压源的输出

图30. PWL电压源和电缆侧差分电压的眼图

LTspice是一款功能强大且免费的仿真工具,可与使用标准C语言和JavaScript代码的波形发生器结合使用。最终,我们得到一种强大的有线通信信号完整性分析工具,其可用于节省实验时间、指导最终产品设计并缩短产品开发时间,加速产品上市。ADI和Würth Elektronik将为工程师提供该工具来设计有线链路,并帮助他们理解10BASE-T1L SPE等新标准。

审核编辑:汤梓红

-

信号完整性

+关注

关注

68文章

1497浏览量

98237 -

有线网络

+关注

关注

0文章

37浏览量

11070 -

C程序

+关注

关注

4文章

255浏览量

37682 -

LTspice

+关注

关注

2文章

132浏览量

14663

原文标题:LTspice+C程序,如何改善有线网络信号完整性?

文章出处:【微信号:ADI智库,微信公众号:ADI智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

常见的信号完整性问题及解决方案

高速DSP 数据采集的信号完整性问题

高速DSP 数据采集的信号完整性问题

在高速设计中,如何解决信号的完整性问题?

数字电路设计的信号完整性问题探讨

识别和修复pcb信号完整性问题

什么因素导致信号完整性问题?

PCB设计中的信号完整性问题

使用LTspice解决信号完整性问题

使用LTspice解决信号完整性问题

评论