信号传输并非严格针对网络设计师,您的PCB设计可能会遇到相同类型的问题。由于您无需费力地摆弄耳朵,因此防止电源完整性和信号完整性问题对于您的PCB设计流畅且无静电至关重要。

HDMI,还是复合?了解信号完整性问题中的信号

无论是带有智能,纯平电视或等离子电视的电缆,卫星,Netflix,Hulu,亚马逊或Youtube,都有多种接收信号的方式,您可以观看所需的电视。同样,大多数PCB在常规和高速设计中将包括几种信号类型。其中一些是:

电源信号:根据复杂程度,您可能有几种不同级别的电源信号。例如,大多数处理器需要3-5V范围内的信号,而放大器可能需要高达15V范围内的偏置电压。

数据信号:数据可以是模拟的也可以是数字的。对于模拟量,典型范围为+/- 10V。对于数字信号,范围可能是0-5V或+ / 5V,具体取决于信号格式。

控制信号:通常用于打开或关闭设备的信号,通常是0-5V信号。

通信信号:这些信号的信号强度可能会低至微伏级别。这些通常是RF,频率可能会在很宽的范围内变化。

除信号强度外,对于模拟信号,频率也是PCB设计中的重要考虑因素。这在具有高频率水平的通信设备的PCB中尤为重要。

输出尺寸和布线注意事项:有多宽?

对于非常简单的PCB设计,通常可以避开设计路线以适应极端的电流和电压。例如,在整个过程中使用单个走线宽度可以处理最大容量。尽管这种情况与最佳实践相去甚远,但您的董事会可能会在这些情况下正常工作。如果您像我一样,我们希望通过使电路板尽可能的小巧和多功能来优化我们的电路板。

对于这些更复杂的PCB设计,必须格外小心,布线也不是那么简单。我们要设计与它们携带的信号相匹配的路线。请参考下表以了解一般注意事项:

采用上述解决方案可减少损失,空间和成本。但是,要正确地合并这些要求使用最佳的PCB设计工具。

确保静音

较旧的电视信号传输中的噪音使您试图通过积雪查看自己喜欢的节目。如今,信号完整性问题(如嘈杂的传输线)可能会给您带来困惑,甚至根本没有信号。的噪声的在PCB设计源可以来自多种来源。例如,开关IC引脚状态引起的干扰,诸如振荡器之类的辐射设备对附近走线的干扰,同一走线上的多个频率信号以及其他来源。

从大多数复杂的PCB设计中完全消除噪声几乎是不可能的。但是,有一些方法可以使噪声最小化。消除噪音的最佳资产是组件的放置。所有分量辐射均取决于频率,并且频率(信号变化)越高,离光源的距离越短。因此,应将处理同一信号的组件放置在远离其他组件的位置。将组件放置在信号彼此起源和终止的地方。

您也可以尝试实现去耦电容器或旁路电容器。如有可能,应将它们直接绑在地面上,并适当调整尺寸。请注意,任何电感都会与电容器结合以建立滤波电路。

嘈杂的数字电视信号

一起扭耳朵:差分传输

只要有可能,可以通过使用差分电路来改善信号完整性。大多数IC设计人员都试图实现这一目标。但是,有时差分对可能会路由到彼此不相邻的引脚。从PCB设计的角度来看,我们要执行以下操作:

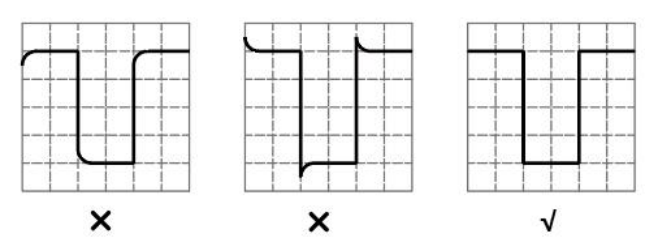

将差分对一起布线。

使用尽可能相同的走线宽度和长度。

在同一信号平面或同一层上布线。

地平面可简化信号完整性

接地层可以为多个电路提供中央层参考,这可以显着减少您的引脚连接和走线数量,更不用说简化复杂PCB的外观布局了。在设计PCB时,以下技巧可以最大程度地减少与接地层相关的问题:

确保没有从电源平面到接地平面的直接路径(这看起来很容易,但是对于复杂的设计,可以忽略它,直到开始油炸才意识到)。

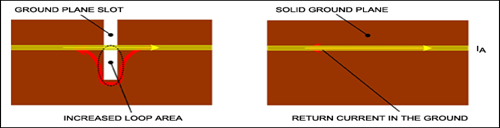

请勿在接地平面上插入间隙。

在接地/电源层之间运行时钟信号(或其他关键信号)。

在同一层上路由使用相同回路(地平面)的信号。

对于具有多个接地平面的板,请在每个平面上的同一点将这些平面连接在一起。

对于带有机箱连接的板,请确保所有接地层都连接在一起。

地平面的做与不做

当我四处移动旧电视的兔子耳朵来获得想要的频道时,总有某种疯狂的方法:向左摇摆,然后向右摇摆,然后来回缓慢地工作,直到找到正确的位置为止。最佳清晰度。值得庆幸的是,在PCB设计中,存在明显更具体的信号完整性问题信号处理方法。通过做出最佳的路由决策,采用降噪策略,在可能的情况下使用差分对以及应用良好的接地层使用,您将显着提高保持信号完整性的机会。

-

信号完整性

+关注

关注

68文章

1495浏览量

98230 -

PCB

+关注

关注

1文章

2347浏览量

13204

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

Cadence工具如何解决芯粒设计中的信号完整性挑战

高频PCB布线“避坑指南”:4大核心技巧让信号完整性提升90%

深圳 9月12-13日《信号完整性--系统设计及案例分析》公开课,即将开课!

罗德与施瓦茨示波器RTO2014破解信号完整性难题的全面指南

上海 6月20-21日《信号完整性--系统设计及案例分析》公开课,即将开课!

信号完整性测试基础知识

PCB设计中的信号完整性问题

PCB设计中的信号完整性问题

评论