案例摘自郑军奇专著《EMC设计与测试案例分析》第三版

问题描述:

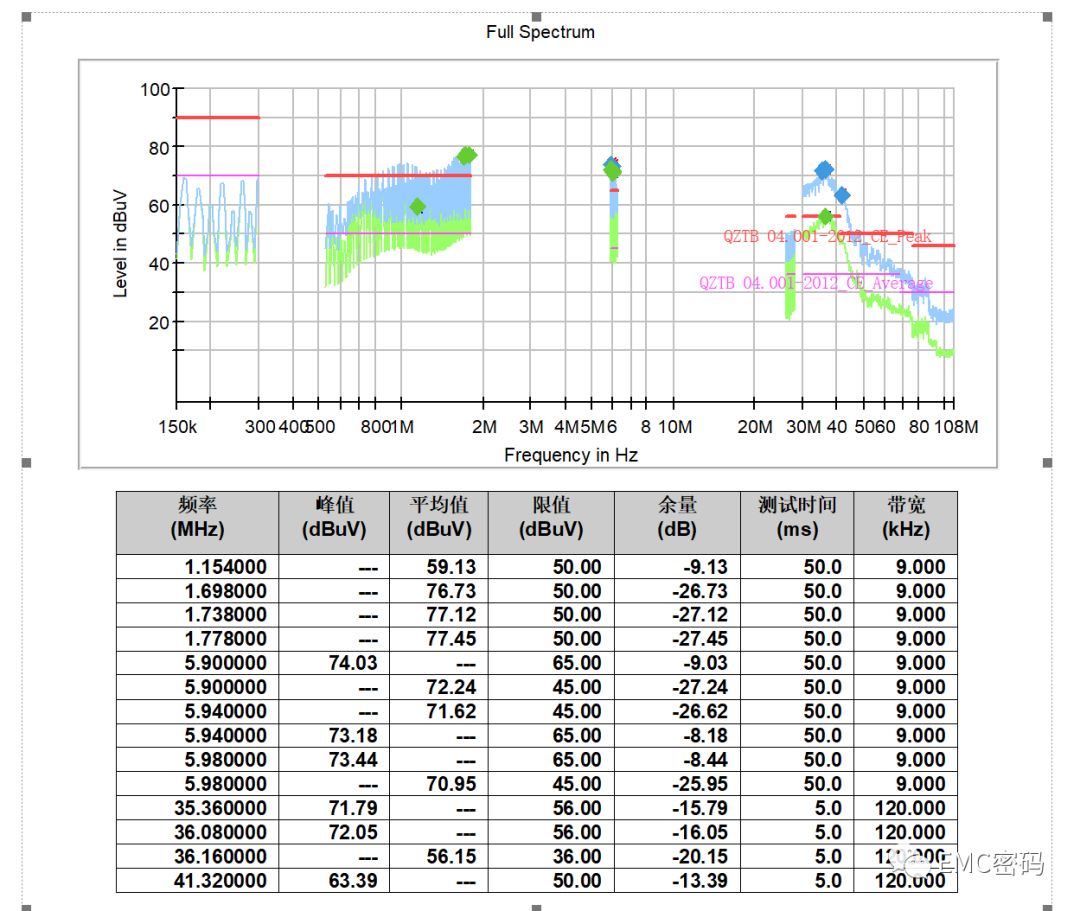

某汽车零部件产品是电机驱动器,在进行传导骚扰测试时,发现没有通过,下图是该电机驱动器的传导骚扰测试结果:

图1 某电机驱动器的传导骚扰测试结果

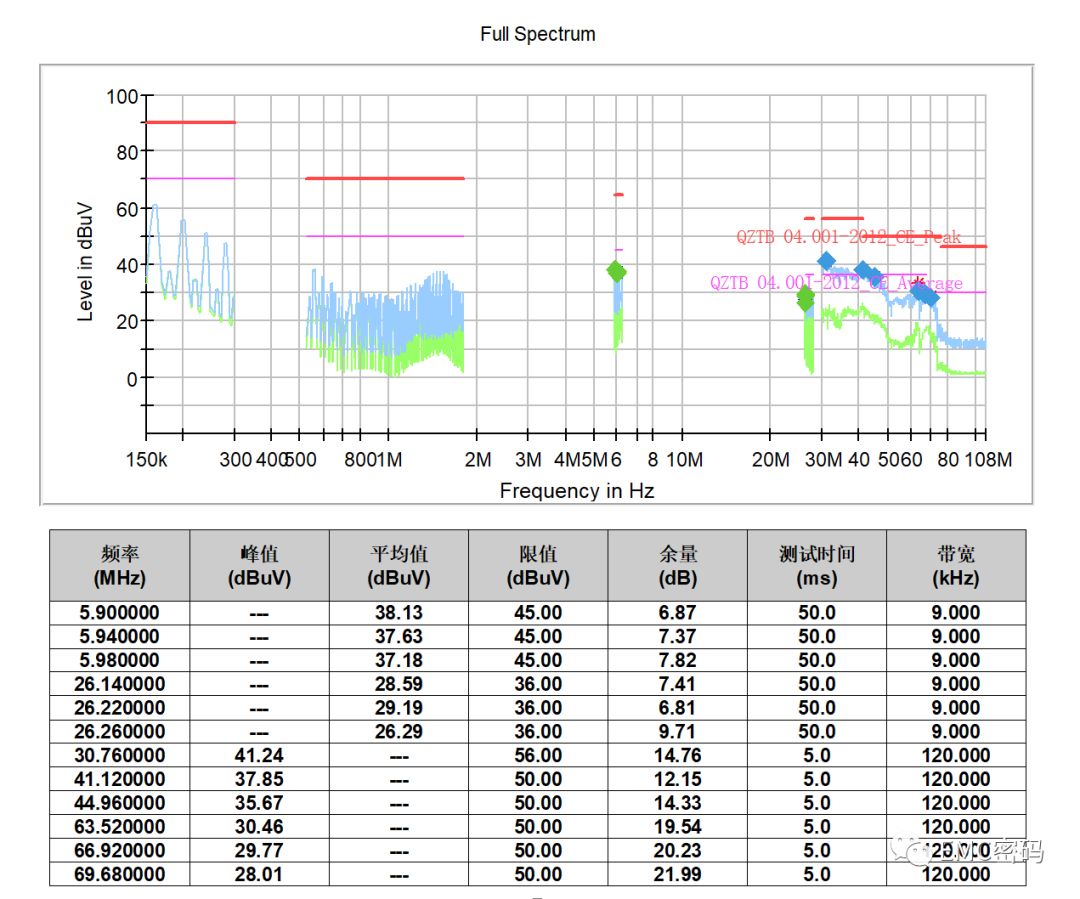

在驱动的功率管的DS级之间并联电容后,测试通过。增加电容后的变频电机驱动器的传导骚扰测试结果如下图2所示:

图2 增加电容后的电机驱动器的传导骚扰测试结果

原因分析:

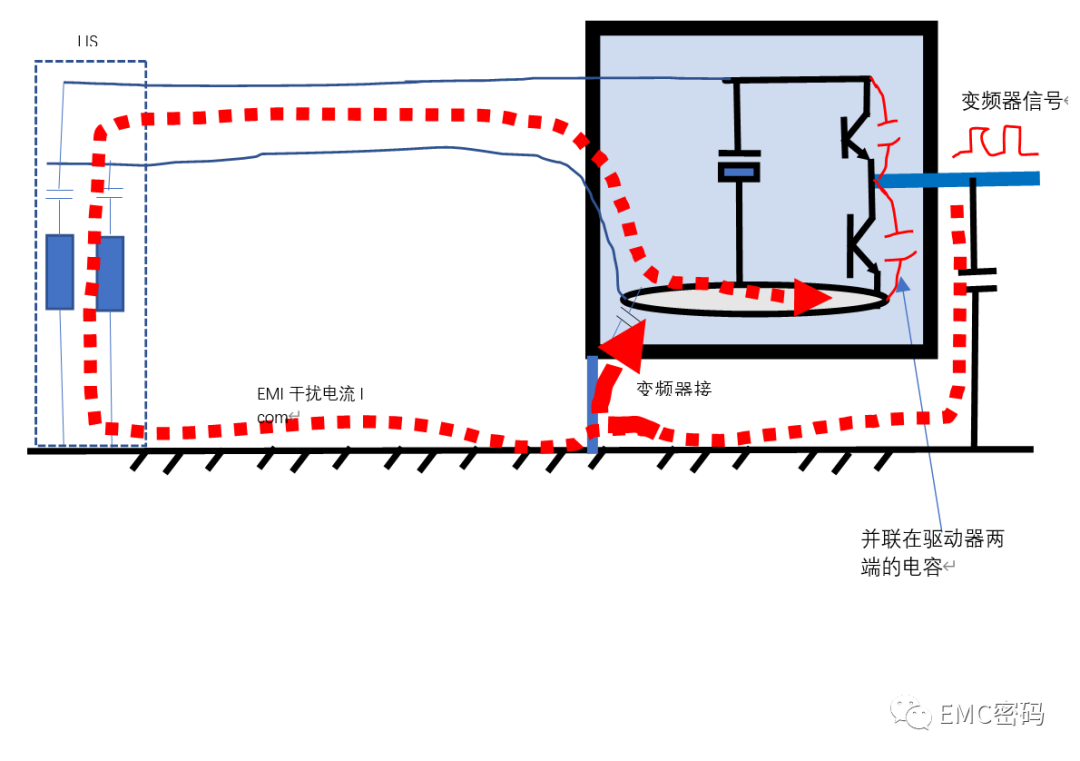

图3是驱动器产生EMI问题的原理图。图3中驱动器的驱动信号线与参考接地板之间存在寄生电容,该寄生电容与参考接地板、LISN、电源线、变频器本身电路组合成一条共模回路,当驱动器的信号电流流过LISN时,即产生传导骚扰。

图 3 变频驱动器产生EMI问题的原理图

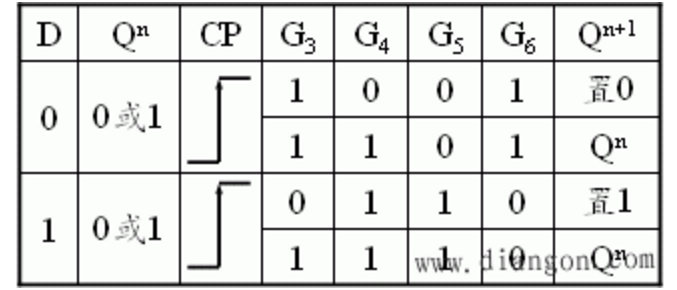

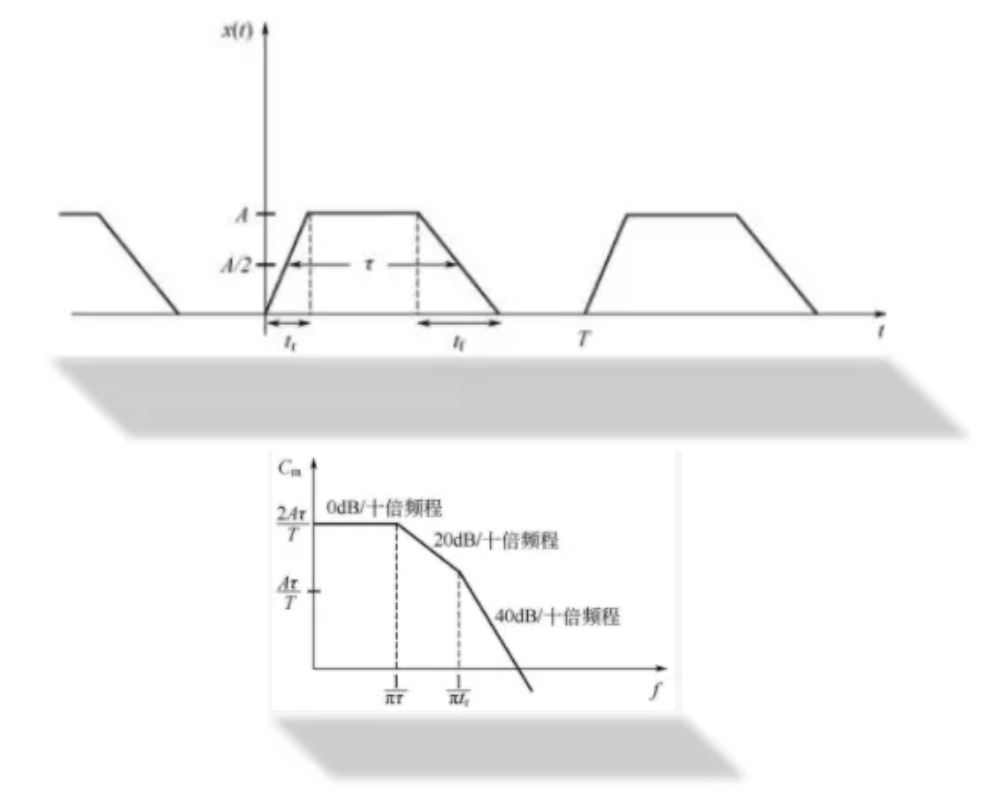

驱动器的输出信号假设为矩形波,根据傅里叶变换,矩形波由无限多个正弦波叠加而成,这些正弦波即为矩形波的基波即各次的谐波分量。根据傅里叶变换理论,矩形波的低次谐波分量的幅度随着谐波次数的变高呈线性衰减,高次谐波分量的幅度随谐波次数的变高呈平方衰减。谐波分量的幅度为线性衰减与平方衰减的转折点为1/ΠTr,如上升沿时间10ns,对应的转折点约30MHz。案例中,当功率管的D、S两极间并联电容后,对于功率管输出的信号电压波形,实质上改变的主要是信号电压波形的上升沿时间,即上升沿时间变长。

而上升沿时间变长后(案例中原上升沿时间为10ns,并联电容后下降为50ns),谐波分量的幅度为线性衰减与平方衰减的转折点为1/ΠTr的值变小(即从原来的30MHz下降为6MHz),矩形波的谐波分量的幅度随着谐波次数或频率更早的进入平方衰减区域,使得高次谐波的幅度变小。高次谐波的幅度变小后,按原理图所示相应的共模电流也变小,传导骚扰也变低。

思考与启示:

上升沿时间与信号的高次谐波的幅度有非常大的关系,而低次谐波的幅度与上升沿时间无关,当产品周期性工作信号的高次谐波频点EMI超标时,降低产品周期性工作信号源的上升沿时间是非常有效的措施;

功率电路中,D、S两极间并联电容或在G极上串联电阻、磁阻都可增大功率管输出信号的上升沿时间,D、S两极间并联的电容值大小与高次谐波幅度的降低无直接的关系,应该考虑电容值大小与上升沿时间的关系;

时钟线上并联电容,也可增大时钟信号线电压波形的上升沿时间,减小时钟信号高次谐波的幅度,降低时钟信号产生的EMI水平。

审核编辑:刘清

-

驱动器

+关注

关注

54文章

9015浏览量

153364 -

emi

+关注

关注

54文章

3864浏览量

134112 -

寄生电容

+关注

关注

1文章

301浏览量

20201 -

变频电机

+关注

关注

4文章

236浏览量

23923 -

电机驱动器

+关注

关注

16文章

831浏览量

66184

原文标题:经典案例:信号上升沿对EMI的影响[20231214]

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

上升沿和下降沿是什么意思?

电容对信号上升沿的影响

西门子1200上升沿和下降沿的操作流程

开关信号的上升沿时间对传导发射的影响

信号上升沿对EMI的影响

信号上升沿对EMI的影响

评论