从字面上理解上升沿和下降沿是一个变量变化的时刻和一个无穷小的时间。但是plc程序中最小的时间单位是扫描周期,所以所谓的边沿就是一个扫描周期。

上例中使用的bTrig变量都是用来让下面的程序执行一个扫描周期的,也可以理解为执行bTrig的上升沿,和下面的编程效果一样:

上升功能块R_TRIG的功能实际上是检测输入变量,当输入变量从低电平变为高电平时,在第一扫描周期输出高电平,然后输出低电平。即,输出一个扫描周期。

与上升沿相同,下降沿检测输入变量从高到低变化的第一个扫描周期。

为了理解的上升沿和下降沿的含义,我们可以灵活地将其应用到程序中,比如让程序执行一个扫描周期,检测一个变量的上升/下降沿,通过设置我们上面例子中的IF语句来重置一个变量,或者在案例中执行一个条件后立即更改判断变量的值,等等。

本文原创首发 www.elecfans.com 源自 www.jcpeixun.com 转载请注明出处,谢谢。

编辑:ymf

上升沿和下降沿是什么意思?

- plc(484636)

- 高电平(22728)

相关推荐

热点推荐

PC1003K 5V_7A_5A单通道低侧GaN FET驱动器技术手册

)。PC1003K设计简洁,可实现极快的传播延迟,仅为2.42纳秒。通过在栅极与OUTH和OUTL之间分别连接外部电阻,可独立调整上升沿和下降沿的驱动强度。该驱动器在过载或故障情况下提供欠压锁定(UVLO),并具备过热保护(OTP)功能。

2025-12-30 17:12:19 0

0

0

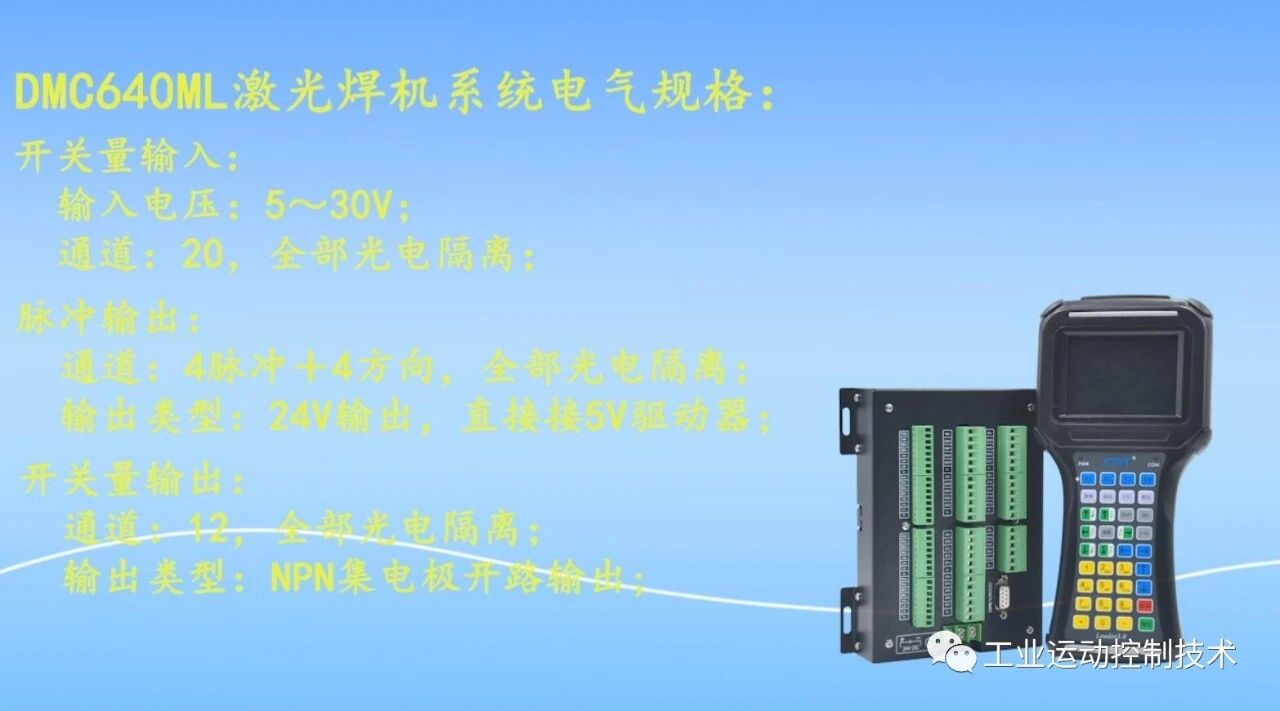

0激光设备:激光出光时间不准问题处理

、问题诊断流程 1. 硬件系统检查 (1)激光电源检测:使用示波器测量Q开关驱动信号的上升沿和下降沿时间,正常值应在50ns以内。若发现信号延迟,需检查电源模块电容是否老化(容量衰减超过20%即需更换)。 (2)光路系统检测:采用红

2025-12-26 07:35:29 262

262

262

262

具有上升时间加速器的 TCA9416 超低电压 I2C 转换器:特性与应用解析

)的 TCA9416 超低电压 I2C 转换器,看看它在实际应用中能为我们带来哪些便利和优势。 文件下载: tca9416.pdf 一、器件概述 TCA9416 是一款具有输出使能 (OE) 输入以及上升沿和下降

2025-12-17 10:10:02 243

243

243

243CW32F030在深度休眠模式下UART接收数据

配置步骤:

步骤 1:

使能 UARTx_RXD 对应引脚的 GPIO 下降沿中断;

步骤 2:

设置 UARTx_CR1.START 为 1,选择 RXD 信号起始位判定方式为低电平;

步骤 3

2025-12-15 06:53:34

常见单片机的功能

沿、下降沿触发和电平触发几种。外部中断一般通过输入口来实现,若为IO口,则只有设为输入时其中断功能才会开启;若为输出口,则外部中断功能将自动关闭(ATMEL的ATiny系列存在一些例外,输出口时也能

2025-12-03 08:30:02

GPIO中断设计中边沿触发和电平触发的区别是什么

瞬间(上升沿/下降沿)、每次跳变仅触发一次中断、需干净跳变(避免抖动)、自动清除(硬件记录边沿事件);

电平触发:持续电平状态(高/低电平)、只要电平维持即持续触发中断、需稳定电平(避免浮动)、必须手动

2025-11-17 06:59:11

CW32F030C8T6:GPIO配置的全攻略

// 配置按键引脚为输入模式

GPIO_InitStruct.IT = GPIO_IT_RISING | GPIO_IT_FALLING;// 中断触发方式:上升沿和下降沿

2025-11-13 06:38:38

FT32F030F6AP7辉芒微FMD单片机32位MCU

:

定时器支持捕获功能,可测量外部信号的上升沿 / 下降沿时间。

运算速度快(Cortex-M0 内核,最高 48MHz 主频),适合高频信号测量(如 MHz 级)。

UART 接口可输出测量数据至

2025-11-10 11:40:55

MCU200T的SPI FLASH驱动程序的单条指令设计

分别发出,这样做当然可以。

同时,要讲如何让设计指令,我们这里先补充介绍下对这张时序图的理解,时序图大家想必在数电学习中已有所了解,就是看时钟上升沿,下降沿数据的变化,或者是看时钟电平拉高 或者 拉低

2025-10-28 08:01:56

基于FPGA的DDR控制器设计

SDRAM相比,DDR SDRAM的最大特点是双边沿触发,即在时钟的上升沿和下降沿都能进行数据采集的发送,同样的工作时钟,DDR SDRAM的读写速度可以比传统的SDRAM快一倍。

DDR3读写控制器

2025-10-21 14:30:16

FPGA搭建DDR控制模块

,DDR SDRAM的最大特点是双边沿触发,即在时钟的上升沿和下降沿都能进行数据采集的发送,同样的工作时钟,DDR SDRAM的读写速度可以比传统的SDRAM快一倍。

DDR3读写控制器可以在Xilinx

2025-10-21 10:40:28

用FPGA实现DDR控制模块介绍

,DDR SDRAM的最大特点是双边沿触发,即在时钟的上升沿和下降沿都能进行数据采集的发送,同样的工作时钟,DDR SDRAM的读写速度可以比传统的SDRAM快一倍。

DDR3读写控制器可以在

2025-10-21 08:43:39

用30道电子工程师面试题来拷问堕落的你...

对输入信号和时钟信号之间的时间要求。建立时间(SetupTime)是指触发器的时钟信号上升沿到来以前,数据能够保持稳定不变的时间。输入数据信号应提前时钟上升沿(如上升

2025-10-15 17:37:10 897

897

897

897

普源示波器DS8204-R触发功能设置指南

基础设置:快速定位信号 1. 触发类型选择 在示波器界面进入“触发”菜单,根据信号特征选择触发模式: 边缘触发:适用于周期性信号,可设置上升沿/下降沿触发; 脉宽触发:针对特定脉冲宽度信号,设置最小/最大脉宽范围; 斜率触发:捕捉信号上

2025-09-29 17:58:09 619

619

619

619

CDCF5801A时钟乘法器技术文档总结

该CDCF5801A提供参考时钟(REFCLK)信号的时钟乘法,具有通过相位对齐器以仅1.3 mUI步长延迟或推进CLKOUT/CLKOUTB的独特功能。对于DLYCTRL引脚上的每个上升沿,只要

2025-09-19 14:07:10 633

633

633

633

嵌入式接口通识知识之Ethernet接口

速率不变,RGMII接口在时钟的上升沿和下降沿都采样数据。在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7

2025-09-16 17:27:43

【上海晶珩睿莓1开发板试用体验】GPIO事件监控&USB asound声卡设备录入声音并通过云平台识别

,而且检测沿变也分只检测上升沿,只检测下降沿,或者两个都检测,我这里就使用两个都检测,这样就可以让开发板检测GPIO引脚的上升和下降两个信号:

然后读取USB声卡录制声音,则需要安装asound库

2025-09-09 18:28:35

嵌入式接口通识知识之I2S接口

低时,表示当前传输的数据是左声道数据;当LRCK为高时,表示当前传输的数据为右声道数据。(2)SCK(位时钟):数据传输的时钟信号。在SCK下降沿发送数据,在SCK上升沿采样数据。(3)Data

2025-08-29 15:45:14

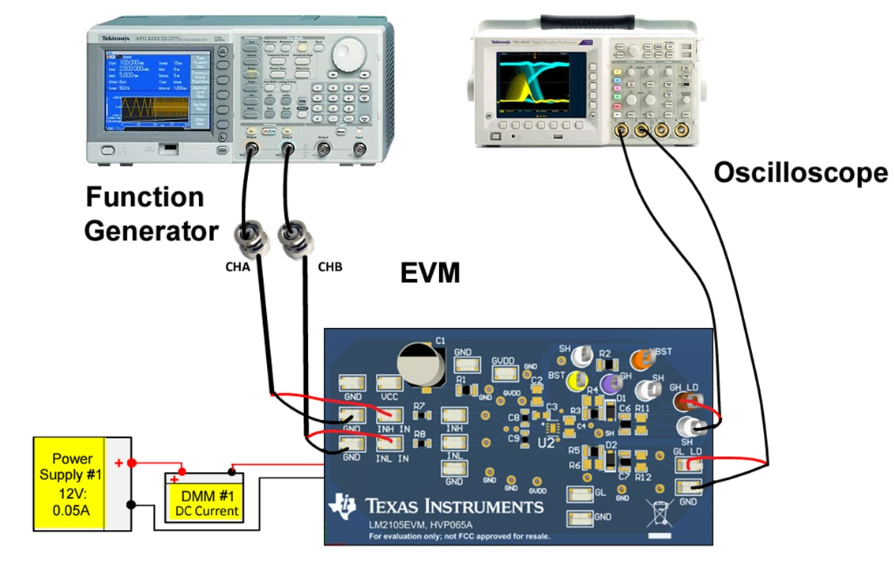

LM2105EVM评估模块技术解析与应用指南

和0.8A灌电流,用于驱动两个N沟道MOSFET。该板还可用于评估采用支持封装的其他引脚对引脚兼容部件。LM2105具有低传播延迟以及驱动器输出高侧和低侧上升沿与下降沿之间的低传播延迟匹配,从而实现对栅极驱动信号的可靠计时。

2025-08-26 16:36:38 739

739

739

739

网络与存储时钟设计实战:156.25 MHz / 100 MHz 参考时钟、抖动预算与 Pin-to-Pin 选型(附 BOM)

;Holdover 是关键

3) 家用实验室如何量“抖动/相噪”?

示波器 + 统计 :采样上升沿/下降沿的时间抖动,统计 RMS / pk-pk。

频谱近似 :用边带评估相位噪声 L(f)L(f)L(f),在

2025-08-22 13:58:01

华沿机器人邀您相约芝加哥Fabtech 2025

9月8-11日,华沿机器人将出席在美国芝加哥举办的Fabtech 2025展览会(展位号:A1139)。针对北美地区规模最大、行业影响力最强的金属加工与智能制造专业展,华沿机器人将以焊接机器人(E10-Pro)为核心重点,展出华沿机器人在自动化焊接、CNC上下料等场景的应用,助力传统制造业自动化升级。

2025-08-20 14:47:36 1281

1281

1281

1281嵌入式接口通识知识之SPI接口

SPI在空闲时,时钟信号是高电平还是低电平。CPHA:时钟的相位;表示SPI设备是在SCK管脚上面的时钟信号变为上升沿时触发数据采样,还是在时钟信号变为下降沿时出发数据采样。至于跳变沿是上升沿还是下降沿

2025-08-14 14:45:11

XMC™-4500 IIC在出现pwm信号正沿时无法驱动半个时钟怎么解决?

我遇到了 IIC 问题。当 PWM 同时产生上升沿时, XMC™ (作为主机)似乎无法产生正 SCLK 相位。 结果,只产生了“8 个时钟”,这导致从设备卡在其 ACK 中并将 SDA 线永久拉低

2025-08-12 07:35:51

CY4147S455将IO口设置成上升沿中断之后,打开看门狗定时唤醒,会自发触发这一中断,为什么?

将IO口设置成上升沿中断之后,打开看门狗定时唤醒,会自发触发这一中断,芯片CY4147S455

2025-08-08 06:35:34

CAN总线电容过大?三种解决方案来了

时,经常会遇到由于下降沿过缓导致的未采样错误。下降沿过缓通常是由于总线电容过大引起的。由于CAN收发器采用单向驱动结构,上升沿有驱动,而下降沿则是通过总线与终端

2025-07-22 11:36:59 565

565

565

565

华沿机器人亮相华为云城市峰会

近日,以“引领智能升级 · 共建美好无锡”为主题的华为云城市峰会2025·无锡顺利召开,作为华为云智能智造领域的签约生态伙伴,华沿机器人副总经理赵屹先生应邀参加,见证无锡人工智能创新中心成立,并出席“无锡人工智能生态共创先锋行动”启动仪式。

2025-07-18 16:34:59 1024

1024

1024

1024【沁恒CH585开发板免费试用体验】+PWM呼吸灯

根据官方提供的关于该开发板的数据手册“CH585DS1.PDF”中有介绍,定时器Timer和脉宽调制PWM资源有以下:

4组26位定时器,16MHz主频定时可达4.2S

4路捕捉/采样,支持上升沿

2025-07-03 19:02:40

华沿机器人:以协作机器人技术赋能汽车智能制造新时代

6月25日,以“轻启未来·赋能质造”为主题的新能源汽车轻量化创新峰会在安徽合肥举办,华沿机器人华南销售总监兼汽车行业BU总监戴劲出席,并发表题为“助力汽车行业智能制造升级变革”的演讲,他全面介绍了华

2025-07-01 09:47:06 1069

1069

1069

1069

快速读懂麦科信MOIP系列光隔离探头

稳定、准确的测量结果;在第三代半导体器件(如氮化镓、碳化硅)研发测试中,凭借其出色的频响特性,可精准捕捉纳秒级快速上升沿与下降沿信号,有效抑制高频共模噪声引发的震荡,呈现纯净、无杂波的信号波形,为

2025-06-27 18:39:18

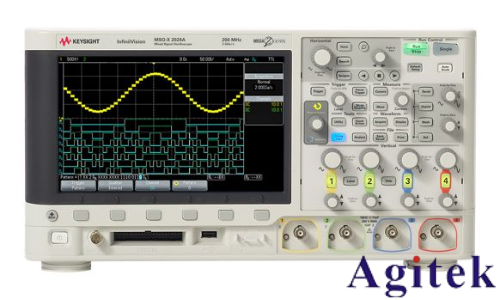

Keysight是德示波器的5个触发设置与波形分析方法

常用的触发模式。在示波器操作界面找到“Trigger”菜单,进入后选择“Edge Trigger”。当信号上升沿或下降沿跨越预先设定的触发电平时,示波器便会触发采集。例如,在检测周期性方波信号时,若要稳定显示方波波形,可将触发电平设置在方波幅值的

2025-06-27 16:00:47 1134

1134

1134

1134

最全的硬件工程师笔试试题集

要求。建立时间(Setup Time)是指触发器的时钟信号上升沿到来以前,数据能够保持稳定不变的时间。输入数据信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个 T 就是建立时间通常所说

2025-06-26 15:34:21

如何在开关模式电源中运用氮化镓技术

问题,可以为上升沿和下降沿设置独立的栅极控制线。

再者,在桥式拓扑结构中,GaN开关在死区时间内的线路损耗会增加。因此,在桥式应用场景中使用GaN 开关时,必须尽可能缩短死区时间,从而实现理想的性能表现

2025-06-11 10:07:24

麻省理工学院香港校友会代表团到访华沿机器人

近日,麻省理工学院香港校友会(MIT Club of Hong Kong)代表团40余人到访华沿机器人总部,通过展厅参观、技术交流与座谈研讨,深入了解国产机器人产业发展现状,并就“机器人+人工智能”的融合发展趋势展开深度对话。华沿机器人CEO王光能及相关人员出席。

2025-05-30 09:26:12 942

942

942

942存储示波器触发电平设置不当会导致什么后果?

使用高级触发功能

推荐功能:

边沿触发:适用于规则波形(如方波、正弦波),需结合触发电平和斜率(上升沿/下降沿)。

脉宽触发:捕获窄脉冲或特定宽度信号(如设置脉宽>50ns)。

逻辑触发

2025-05-29 14:13:03

DDR系列连接器主要应用于工控和主板领域等

传输两次数据(上升沿和下降沿),从而显著提高数据传输速率。同步设计:DDR内存与系统时钟严格同步,降低了时序偏差,确保数据的准确传输。高带宽:例如,DD

2025-05-17 23:35:17 929

929

929

929

USB示波器如何设置触发模式?

。

常见触发模式设置及适用场景边沿触发

设置方法:选择边沿触发模式后,还需设置触发边沿(上升沿或下降沿)和触发电平。触发电平可以通过软件中的滑块、数值输入框或旋钮来调整,将其设置在信号的关键位置,例如

2025-05-15 15:28:27

XD08M3232接近感应单片机的接近感应模块的工作原理

。

ACP_INTS<1:0>:选择中断触发方式(上升沿、下降沿、双沿、电平)。

ACP_FLT<2:0>:设置比较器输出滤波时间,抑制高频噪声。

IR_C1

2025-05-14 11:07:36

模拟开关切换电流时遇到的问题

在做模拟开关切换电流的实验中, 使用6片ADG701组成三路切换的阵列,测量两片模拟开关之间的负载电阻的电压,在上升沿或下降沿都会出现us级别的振铃或者充电的现象

2025-05-06 21:48:07

【RA-Eco-RA4M2开发板评测】RA-Eco-RA4M2 按键操作

配置为下降沿中断、上升沿中断和上升下降沿中断这三种模式。

EIRQ外部中断

RA4M2的所有 GPIO 都引入到EIRQ外部中断线上,使得所有的 GPIO 都能作为外部中断的输入源。GPIO

2025-04-27 23:09:06

MOSFET讲解-16(可下载)

开通的上升沿是很长的,从关断到完全开通需要t0-t4这个时间。那么低阈值MOSFET的好处就说,这个上升沿的时间变的更短。打个比方,假设高低阈值的两个管子,它的上升沿斜率都是一样的,那么,低阈值的管子,

2025-04-22 13:24:12 6

6

6

6系统上强电之后,串行模式的AD7606B偶尔发出错误的DoutA,DoutB,怎么解决?

1. AD7606B配的是“三线模式”,片选被拉低,ADC在BUSY信号的下降沿吐出第一个数据,处理器在SCLK(25MHz) 的上升沿读取数据;

2. AD7606B的外围配置如下:

3.

2025-04-16 06:35:23

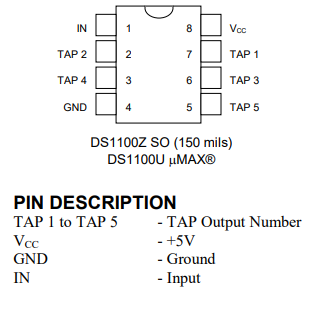

DS1100 5抽头、经济型定时单元(延迟线)技术手册

了成本、并大大提高了可靠性。DS1100 5抽头硅延迟线在经过型号尾标指定的固定延迟后可以在输出端重现输入逻辑状态。DS1100设计成以相同精度重现上升沿与下降沿。每个抽头都能够驱动10个74LS负载。

2025-04-15 17:00:29 766

766

766

766

上升沿时间在10ns以内的电磁铁驱动电路请教

、输出脉冲的上升沿时间在10ns以内

4、目前没有负电压的电源

我目前的想法是使用H桥电路实现,使用4个nmos管和驱动芯片,采用6V供电。请问各位大佬有没有什么别的电路架构推荐呀?

感谢观看!

2025-04-15 16:09:16

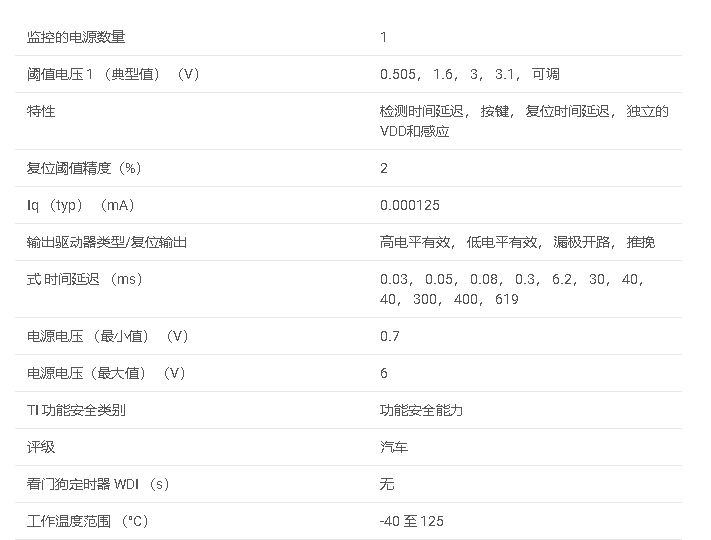

TPS3899-Q1 具有可编程检测和复位延迟的汽车级毫微功耗监控器数据手册

和 CTR 都提供了 RESET 信号的上升沿和下降沿的延迟可调性。CTS 还通过忽略受监控电压轨上的电压毛刺来充当去抖器,并作为“手动复位”运行,可用于强制系统复位。

2025-04-10 09:43:28 635

635

635

635

存储示波器的触发问题及解决办法

深度不足,导致预触发和后触发数据被压缩。

4. 触发模式不匹配(如脉宽、视频触发失效)

原因:

信号特征不符合所选触发模式(如脉宽触发需满足特定时间范围)。

触发斜率(上升沿/下降沿)选择错误。

二

2025-04-09 14:39:44

大族机器人正式更名为华沿机器人

近日,大族机器人在官方渠道发布改名公开信,“深圳市大族机器人有限公司”正式更名为“广东华沿机器人有限公司”(以下简称“华沿机器人”),对应的英语名称为"Guangdong Huayan Robotics Co. Ltd”,本次更名涉及海内外所有业务。

2025-04-02 14:22:47 3814

3814

3814

3814麦科信MHO1系列:示波器捕捉瞬间波形的高效方法

的上升沿和下降沿波形对于评估信号完整性至关重要;在故障诊断中,瞬间的异常信号可能是故障的直接证据。因此,能够高效地捕捉瞬间波形,对于工程师们来说是至关重要的技能。捕捉瞬间波形的高效方法1、选择合适

2025-03-27 09:29:39

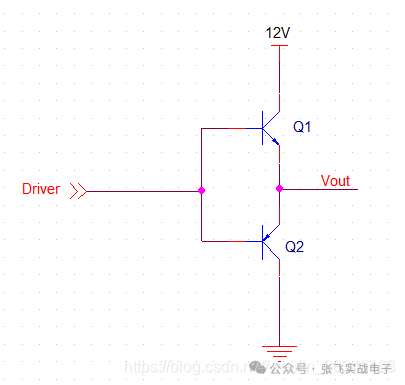

推挽电路驱动与图腾柱驱动的区别

结构如下图所示,输入为高的时候上面三极管导通,输入为低的时候下面的三极管导通,无论输入的上升沿下降沿有多么的缓,都不存在上下管同时导通的问题。图:标准的推挽电路推

2025-03-20 19:33:23 1903

1903

1903

1903

利用X射线衍射方法测量薄膜晶体沿衬底生长的错配角

本文介绍了利用X射线衍射方法测量薄膜晶体沿衬底生长的错配角,可以推广测量单晶体的晶带轴与单晶体表面之间的夹角,为单晶体沿某晶带轴切割提供依据。

2025-03-20 09:29:10 848

848

848

848

触觉智能RK3506核心板,工业应用方案分享(一)

技术解析底层架构突破双倍数据速率:通过上升沿与下降沿双重触发机制,实现单周期内2倍数据吞吐量,较传统SPI接口效率提升300%。多通道并行:支持8线/16线位宽可

2025-03-18 11:49:48 1122

1122

1122

1122

【智能化+高精度】电焊机为何需要一颗“智慧大脑”?航顺HK32F103A给出答案

/PDR)

软件复位

看门狗(IWDG 和 WWDG)复位

低功耗管理复位

可编程电压检测器(PVD)

8 级检测电压门限可调

上升沿和下降沿检测可配置

通用输入输出端口(GPIO)

64 脚封装提供

2025-03-11 10:50:16

从\"能用\"到\"好用\"!航顺HK32F39A国产变频器方案的进阶密码

(PVD)

8 级检测电压门限可调

上升沿和下降沿检测可配置

通用输入输出端口(GPIO)

64 脚封装提供 51 个 GPIO 引脚,100 脚封装提供 80 个 GPIO 引脚

所有 GPIO 引脚

2025-03-11 10:43:10

外部中断触发类型为双边沿触发,进入中断回调后有什么办法判断该边沿是上升沿还是下降沿?

外部中断触发类型为双边沿触发,进入中断回调后有什么办法判断该边沿是上升沿还是下降沿

2025-03-11 06:05:26

《开关电源高频电磁波干扰概论》

200M 时由于幅值已经很低,所以影响很小

波形影响低频部分

上升沿和下降沿影响高频部分

占空比对个频谱幅值有一点影响

第 2 节:

下以部分 13-42 页,介绍的内容比较杂,有传导和辐射的场地

2025-02-26 15:11:08

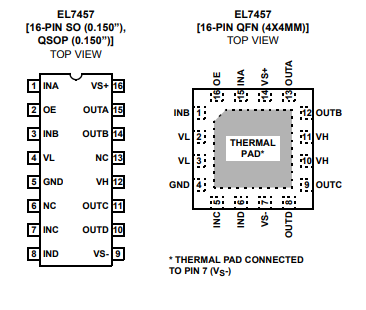

EL7457系列40MHz非反相四通道CMOS驱动器应用笔记

CCD 应用中,驱动程序应在断电期间禁用。EL7457 还具有非常快的上升和下降时间,匹配时间在 1ns 以内。上升沿和下降沿之间的传播延迟也匹配在 2ns 以内。EL7457 提供 16 引脚 QSOP、16 引脚 SO (0. 150“) 和 16 引脚 QFN 封装。所有产

2025-02-25 14:59:04 1102

1102

1102

1102

DLPC410在图片显示在DMD上的同一时刻,产生一个同步信号以协同DMD与其他设备之间的工作,同步信号应该与哪个信号同步?

需求:在图片显示在DMD上的同一时刻,产生一个同步信号以协同DMD与其他设备之间的工作。

问题:该同步信号应该与哪个信号同步?RST_ACTIVE的上升沿?RST_ACTIVE持续4.5us的下降沿?还是4.5us+8us(setting time)?

2025-02-24 06:58:23

THS1206写使能是下降沿有效,还是低电平有效?

在向THS1206写控制字时,要写四次。

开始按照写使能,然后连续写四次数据,结果控制字没写进去;

写使能,写一次数据后关闭写使能,第二次写时再打开写使能,这样依次写四次,控制字才写入。

请问为什么呢?不知道写使能是下降沿有效,还是低电平有效?

谢谢!

2025-02-14 08:09:58

DAC34H84的时钟DDR的下降沿采不到数,怎么办?

DAC34H84的TI官方开发板。

用FPGA在时钟的上升下降沿的时候放上数(用示波器看眼图和时钟的关系绝对满足setup和hold time时间关系),但是始终只有上升沿的数能从IOUTA

2025-02-13 07:45:10

DAC5682Z两通道输出有相差是怎么回事?

信号,通过DDR接口传递给DAC5682Z作为两个通道的数据;CLK2也是200MHz,DDR接口上升沿和下降沿发送的都是同样的数据;

DAC5682Z配置为内插2倍模式,通过示波器观察两个通道的输出

2025-02-12 08:24:16

ADS1198采样值为0是什么原因导致的?

ADS1198初始化已经成功,读ID寄存器,返回值正确(0xB6),设置采样率后,用示波器测DRDY引脚下降沿脉冲的频率正确。

参考手册,发送RDATAC命令后,拉高START,开始转换,DRDY

2025-02-11 08:25:21

求助,AFE5801中关于Dclk的疑问求解

后续处理,但是dclk每个上升沿和下降沿都对应着一个bit数据,而FPGA不能同时采用一个时钟上升沿和下降沿进行串并转换,这个时候是将dclk进行2倍频后用于串并转换模块的时钟信号还是有什么更好的办法?

2025-02-11 08:08:22

HMC848LC5 一款可编程输出电压的45 Gbps 1:4解复用器

HMC848LC5是一款1:4解复用器,设计用于高达45 Gbps数据解串应用。 该器件使用半速率时钟的上升沿和下降沿来采样输入数据序列D0-D3,并将数据锁存至差分输出。 片上生成1/4速率时钟

2025-02-10 15:47:05

HMC855LC5 一款可编程输出电压的28 Gbps 1:4解复用器

HMC855LC5是一款1:4解复用器,设计用于高达28 Gbps数据解串应用。 该器件使用半速率时钟的上升沿和下降沿来采样输入数据序列D0-D3,并将数据锁存至差分输出。 片上生成1/4速率时钟

2025-02-10 15:42:38

HMC854LC5 一款可编程输出电压的28 Gbps 4:1多路复用器

HMC854LC5是一款4:1多路复用器,设计用于28 Gbps数据串行应用。 多路复用器在输入时钟的上升沿锁存四个差分输入。 该器件使用半速率时钟的上升沿和下降沿来串行传输数据。 片上生成1/4

2025-02-08 10:35:39

ADC101S021 SDATA 输出信号偶尔会出现在SCLK的下降沿的时候,有个输出脉冲这个是什么问题?

ADC101S021 SDATA输出信号偶尔会出现在SCLK的下降沿的时候,有个输出脉冲,但是,又马上拉低了。这个是什么问题?

2025-02-07 07:51:20

使用ADS1232时遇到的问题求解决

最近在使用ADS1232的时候,偶然出现一个问题:

ADS1232没有转换输出完成的下降沿出现,即使是系统重新上电,依然如此。

在一次偶然用示波器测试的时候,将DOUT和SCK短接发现系统正常工作

2025-02-07 06:41:15

求助,关于ADC124S021的时序疑问求解

从datasheet后面的使用知道DIN在SCLK上升沿输入,DOUT在SCLK下降沿输出,而时序图好像显示的是DIN在时钟下降沿输入,DOUT则看不出来,现在只转换IN2,但转换结果都是0

2025-02-06 07:30:10

ADS801输入模拟量很稳定,但是12位AD输出却非常不稳定是怎么回事?

分频送出来的,上升沿下降沿应该都没问题

2.我是通过FPGA来读AD转换值的,当ADC开始转换时,当我26脚悬空还没有接入模拟量发现AD有输出(我把12位都接了LED作为监测的),用万用表量是2.25V

2025-02-05 07:59:41

ADS8363用FPGA做了一个SPI接口控制器,用示波器观察SDO无信号输出是怎么回事?

用FPGA做了一个SPI接口控制器,用示波器观察,CS,convst/rd,SDI,BUSY,CLK到片脚信号正常,但SDO无信号输出?

有谁知道SDI数据应在SPI CLK时钟的上升沿改变还是下降沿改变,需要每次单通道采集一次数据,应设置MODE几方式较好?

2025-01-24 06:56:30

使用高速ADC工作中遇到两个很关键的问题求解答

时的频率PWM正常、产生500K频率时在上升沿和下降沿有些尖脉冲、达到10M时PWM波直接失真变形成了类似正弦波);二是告诉ADC的并口输出的数据处理问题(我们目前使用的ADC12040为12位并口输出

2025-01-24 06:51:37

SN65HVS880是不是在CLK的上升沿发送数据出去的?

IP2 IP1 IP0?

3)还有一个问题是SN65HVS880是不是在CLK的上升沿发送数据出去的?

谢谢。

2025-01-24 06:40:03

使用MSP430G2452的IO口读ADS1232的AD数据,在RDY/DOUT脚发生下降沿时触发中断读AD数据,为什么?

使用MSP430G2452的IO口读ADS1232的AD数据,在RDY/DOUT脚发生下降沿时触发中断读AD数据,而非查询RDY/DOUT为低电平。在采用中断方式读AD数据时发现,读数据的速率并非

2025-01-23 07:12:47

使用ADS1230做一个压力控制设备,测试时发现一直能不断DOUT的下降沿信号,连上MCU后DOUT一直是高电平,为什么?

最近在使用ADS1230做一个压力控制设备,精度要求不高,但在测试的时候发现一直能不断DOUT的下降沿信号,连上MCU后DOUT一直是高电平。这个的版图,设计的时候忘了把REFP和REFN接上电源

2025-01-23 07:09:47

使用SN65MLVD082时遇到的几个疑问求解

,125MHz),上升沿裕度很小,甚至上升沿的振铃已经低于150mV,改用51欧姆电阻,虽然信号幅度下降,只有+/-250mV,上升沿裕度能保证在100mV以上。

1、使用51欧姆电阻是否存在问题,是否会

2025-01-23 07:01:34

ads1248输入数据是上升沿有效,输出数据确是下降沿有效,为什么?

ads1248输入数据是上升沿有效,输出数据确是下降沿有效。我对SPI进行配置是,应该怎样啊。求大神,好人一生平安。

2025-01-23 06:39:17

adc08200和FIFO SN74V273对接遇到的疑问求解

采用流水线结构,时序图:

关于这个有两个疑问~这款AD和FIFO SN74V273对接

1FIFO是在CLK的上升沿读数据并存储,而看AD的时序图似乎是在下降沿读取数据比较可靠稳定,需要

2025-01-22 06:44:25

STM32仿PLC上升沿下降沿库

引用#include \"IEC.h\" 调用上升沿下降沿函数TRIG();

传入变量 R_TRIG[0].IN = X0; F_TRIG[0].IN = X0;

上升沿输出

2025-01-20 16:11:00

如何判断电路是否为高频电路

在数字电路中,工程师需要判断该电路是否高频电路,以此确保电路性能稳定、减少信号失真和避免传输线效应,本文将分享如何判断电路是否为高频电路。 1、信号的上升沿/下降沿时间(Tr) 若信号的上升沿或下降

2025-01-20 10:49:00 1367

1367

1367

1367使用的display控制器输出是R[7:0],G[7:0],B[7:0],共24根线,DS90C387R是12根线输入,请问两者怎么相连?

,如何做到在一个时钟周期里,上升沿采样到G[3-0]和B[7-0],下降沿采样到R[0-7]和G[4-7]?

请大侠赐教!谢谢!

2025-01-16 07:45:28

请问ADS7864采样结束怎么控制?

看了ADS7864的手册,采样开始是通过将HOLDX引脚拉低引起的,那么采样结束是不是要将HOLDX引脚拉高啊?采样时间(决定采多少个点)是不是就是下降沿与上升沿之间的间隔?

2025-01-16 07:24:10

ADS7864用BUSY接DSP的外部中断来读取采样数据,应该是采样上升沿触发外部中断还是下降沿?

信号的上升沿时,数据存入寄存器中了。这两者是不是有矛盾呢?我用BUSY接DSP的外部中断来读取采样数据,应该是采样上升沿触发外部中断还是下降沿?

2025-01-16 07:19:43

ADS7864内部开始一次新的转换时,BUSY引脚电平变低,为什么?

根据ADS7864的手册,HOLDX引脚拉低启动一次转换,这里所说的转换应该可以说成是采样。但是,AD内部开始一次新的转换时,BUSY引脚电平变低。这里所说的转换不应该说是采样了。是不是先是采样,然后才是转换,也就是说HOLDX的下降沿先于BUSY的下降沿?两个下降沿之间的时间间隔是固定的吗?

2025-01-16 06:22:38

ADS7864用BUSY接DSP的外部中断来读取采样数据,应该是采样上升沿触发外部中断还是下降沿?

,转换进行期间一直是低电平,数据锁存到寄存器后再升高。这表示BUSY信号的上升沿时,数据存入寄存器中了。这两者是不是有矛盾呢?我用BUSY接DSP的外部中断来读取采样数据,应该是采样上升沿触发外部中断还是下降沿?

2025-01-15 06:50:51

spi16f887与ldc1000的spi通信,是否对于读、写,都是只需要把CSB变成低电平即可?

写入0x05时)是否是在sclk上升沿传送数据,而在写入紧跟的数据时是否要换成在sclk下降沿传送数据。

3.对于读操作,是否是在sclk的下降沿传送数据。

4.对于读操作,是否是先通过

2025-01-14 07:45:20

怎么简单检测ADS8556有没有在工作?

您好!我在使用ADS8556,给CONVST_x一个上升沿,是不是BUSY就一定会出现上升和下降的信号?或者怎么简单检测ADS8556有没有在工作?

2025-01-10 08:14:57

ADS1254用模拟SPI的方式读取数据,读取到的数据呈现下降沿趋势,为什么?

调试程序中,首先在方波的上升沿开启CLK(8M),开始转换,在用定时器中断等待43.4*6us后,用模拟SPI的方式读取数据,但是读取到的数据前面几次始终搞不太对,呈现下降沿趋势,后面的数据

2025-01-09 07:23:11

ADC108s022 DIN是在SCLK上升沿向ADC写参数,而DOUT在SCLK的下降沿从ADC中读取转换后的数据?

是用的是SPI接口的ADC芯片,时序如下

是不是说,DIN是在SCLK上升沿向ADC写参数,而DOUT在SCLK的下降沿从ADC中读取转换后的数据??

2025-01-09 07:14:06

求助,关于ADS7846中断及busy信号异常问题求解

触摸屏后不按触摸屏,在第3个时钟的下降沿笔中断口会输出一个低电平,并且电平持续至本次采样结束,busy会在第5个时钟上升沿和第10个时钟下降沿输出两次高电平,高电平持续时间大致半个时钟周期,DOUT口

2025-01-09 07:08:12

ADS1278上电后并未发热,只是DRDY一直检测不到下降沿,为什么?

第一次使用ADS1278,设计中疏忽导致DVDD与IOVDD都给了3.3V,AVDD给5V,板子上电后并未发热,只是DRDY一直检测不到下降沿,请问DVDD(手册中规定1.8V标准)给3.3V会带来哪些后果,可能导致AD出现目前的情况吗?

2025-01-08 08:20:22

使用stm32与ADS1274通讯,将ADS1274的sync拉低再拉高进行第二次采集过程时都不再有DRDY下降沿出现,为什么?

的sync拉低后一段时间再拉高进行第二次采集过程时始终都不再有DRDY下降沿出现,只能下电后再上电进行再次采集。(期间power-down、test、format、mode管脚都不发生变化,电源

2025-01-08 07:02:08

ADS62P19输出LVDS数据的疑问求解

ADS62P19的datasheet第54页关于LVDS的数据输出有如下表述:

偶数标号的数据在CLKOUTP的上升沿采样,奇数编号的数据在CLKOUTP的下降沿采样。但是下面图中显然和该说

2025-01-08 06:19:49

SN74AC74将CLK和D端使用同一个信号,Q输出从0变为高,请问大神是什么原因造成的呢?

的过程中(下降沿),Q输出从0变为高,请问大神是什么原因造成的呢?规格书上显示上升沿动作,怎么会下降沿也动作呢?谢谢

2025-01-07 06:36:34

使用单片机与单ads1271通信,不论输入电压是多少,输出均是0x7FFFFF,为什么?

我使用单片机与单ads1271通信,不论输入电压是多少,输出均是0x7FFFFF。我是在DRDY引脚下降沿的IO中断里开始读数据。

DRDY在SCLK的第一个下降沿处恢复高电平。

DOUT的图形就是0x7FFFFF

输入(AINP − AINN):0--2V。

2025-01-07 06:07:57

电子发烧友App

电子发烧友App

评论