今天来聊一聊时钟树。首先我先讲一下我所理解的时钟树是什么,然后介绍两种时钟树结构。

时序器件传递信号的时候需要依赖时钟,而STA一项关键的检查就是不能有setup/hold violation。如果对于同一时钟域的两个时序器件,如果他们接收到的时钟之间有相位差,有可能会使setup/hold更难满足,如果产生violation,芯片就会发生逻辑错误。

而时钟从时钟源到sink是需要一定的传播时间的,距离时钟源越远的器件传播时间越长。

有的时候data的传播方向和clock的传播方向相同,如果不做任何时钟树处理,这种情况对setup有好处;有的时候data传播方向与clock传播方向相反,这就对hold有好处;而如果电路中存在反馈回路,那data传播方向就不确定。

所以为了能使上述所有情况都有一个较好的时钟性能,我们会希望时钟到达每个时序器件的时间一样,也就是传播时间的差(skew)越接近0越好。时钟树的目的正是如此。因为时钟树实在太过重要,现在也是很多人研究的课题。

我想说的第一种结构就是H-tree。它的结构确实很形象的像一棵树,是应用最广的结构了。

对于一个四四方方完全对称的芯片来说,H-tree会先从root长到整个芯片的中心,再分出两个trunk到芯片左右两侧,分出的trunk与root相互垂直,每个trunk再分两个垂直枝干出来……不断这样分下去,得到一个简单的分形结构,最终的leaf连接到相应的clock pin上。

这样在物理上就可以保证每一个cell到root的走线长度一致,相应的net上的delay就会一样,再加上整个tree上的buffer也都相同,就能保证传播时间完全一致,从而实现skew为0. 当然实际的芯片不会这么理想化,长出来的H-tree也不一定像一个个H,但它的逻辑结构是一样的。

并且另外一种升级版的H-tree就不保证走线长度一样了,只要保证RC信息一致即可,好像可以称为RC-tree(或者一般也就叫H-tree了)。

第二种结构是网格状的(mesh)。就是把时钟树的每一级做成一个网格,级与级之间用多个buffer相连,最终把最后一级mesh接到clock pin上。

可是这样不就等于把多个driver的output接在一起了吗?这在我们ERC检查的时候是违反的呀?但是,制定output不能短接的依据是担心一个output输出1一个output输出0,这样会造成电源地之间的短路。

但是对于clock mesh来说,它的buffer全部都是同时变化,永远是一样的状态,这也就使mesh成为可能。

但是,毕竟每个buffer到达的时间还是会有一丢丢的差别,还是会存在很短的瞬间电源和地在mesh上发生短路,再加上mesh本身就需要更多绕线,它的功耗是非常大的。另一个缺点就是会占用很多绕线资源。

但是mesh的skew容易做的更小,毕竟每一级它们的输出都接在了一起,只有最后一级接在不同pin上。可以说mesh是牺牲了功耗换取更小的skew。

现在大多数的design还是在利用传统的H-tree,只不过它的变式很多。mesh结构更复杂,EDA tool也不能很好地自动化完成,设计上相对更加困难。

-

STA

+关注

关注

0文章

52浏览量

19622 -

时钟树

+关注

关注

0文章

58浏览量

11290 -

时钟源

+关注

关注

0文章

113浏览量

16820 -

电源地

+关注

关注

0文章

36浏览量

10151

发布评论请先 登录

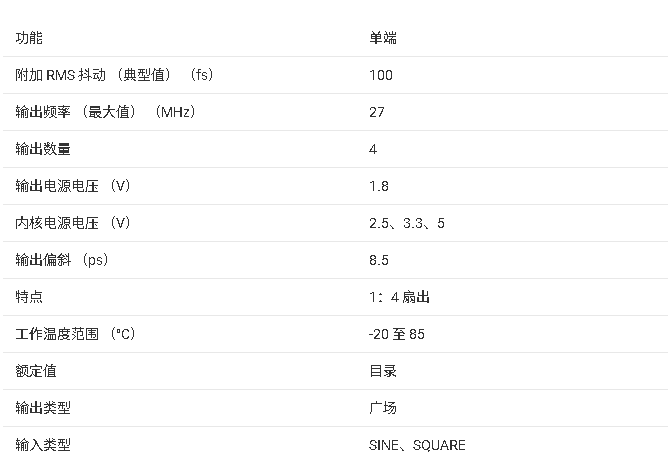

LMH2190:一款高性能四通道时钟树驱动器的深度剖析

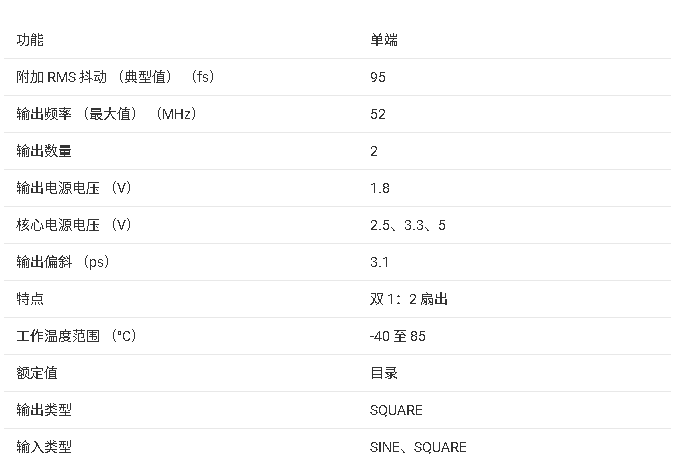

探索LMH2191:52 MHz时钟树驱动的卓越之选

门控时钟(Clock-gating)介绍

外部高速时钟支持两种工作模式

时钟树解析

E203工程源码时钟树解析

时钟设计优化实战

LMH2190 四通道27MHz时钟树驱动器技术文档总结

LMH2191 双通道52MHz时钟树驱动器技术文档总结

ntp时钟同步服务器是什么?ntp时钟同步服务器介绍

时钟树是什么?介绍两种时钟树结构

时钟树是什么?介绍两种时钟树结构

评论