人工智能(AI)是预计到2030年将成为价值数万亿美元产业的关键驱动力,它对半导体性能提出了新的要求。在交付下一代AI能力方面,一些最复杂的问题来自于需要通过新的刻蚀技术来解决的器件制造挑战。

为什么AI对刻蚀技术施加特殊压力?基本原因是AI训练所需的大量数据。这些数据需要高水平的并行处理、丰富的非易失性存储器(如NAND)以及快速的数据传输速率,以将数据推入和推出存储器。先进的设备依赖于在三维中制造的体系结构。作为一种减法过程,刻蚀是塑造这些结构的强大工具。全围栅(GAA)晶体管、低成本每比特的3D NAND存储器和高带宽存储器是AI未来的关键,它们都需要新的、创新的刻蚀方法来塑造它们的器件结构。

刻蚀一直是一项关键而具有挑战性的工艺,但为AI提供动力的芯片将把这一挑战推向一个新的水平。它们不仅要求前所未有的刻蚀精度,还需要能够有选择性地去除一种材料而保留另一种材料,修改剩余材料的表面特性,刻蚀具有越来越高纵横比的结构,有时甚至需要进行横向刻蚀而不仅仅是垂直刻蚀。

垂直刻蚀在AI逻辑中的应用

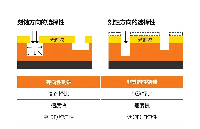

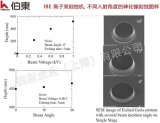

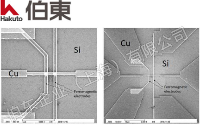

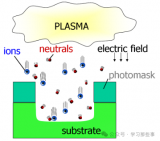

多年来,各向异性定向刻蚀(anisotropic directional etch)一直是集成电路制造中一种非常有价值的工具。干法等离子体反应离子刻蚀(dry plasma reactive ion etch)已被用于实现低介电常数(low-κ)的双柱连线(dual-damascene interconnects)、高介电常数(high-κ)的金属栅(metal gates)、FinFET、埋藏栅DRAM和多代3D NAND。但近年来,向全围栅(GAA)晶体管架构的转变要求采用一种新的、具有挑战性的方法:各向同性、高选择性刻蚀。通过各向同性刻蚀,不仅仅是从堆叠结构的顶部向下刻蚀,而是同时在多个方向上均匀去除材料,这个过程被称为垂直刻蚀(perpendicular etch)。

垂直刻蚀是一种新的刻蚀方法,它在GAA晶体管架构中发挥着重要作用。在传统的晶体管结构中,刻蚀只需要从顶部向下进行,但在GAA晶体管中,需要在多个方向上均匀地去除材料,以形成全围栅结构。垂直刻蚀可以实现对多层材料的同时刻蚀,从而形成所需的结构。

垂直刻蚀的挑战在于实现高度选择性的刻蚀过程。由于需要在多个方向上均匀去除材料,必须确保只有目标材料被刻蚀,而其他材料保持不变。这需要精确控制刻蚀气体、工艺参数和刻蚀时间,以实现所需的选择性。

总之,垂直刻蚀是一种在GAA晶体管架构中必不可少的刻蚀方法。它通过各向同性刻蚀的方式,在多个方向上均匀去除材料,实现了复杂的全围栅结构。随着技术的发展,垂直刻蚀技术将继续演进,以满足未来集成电路制造的需求。

审核编辑:汤梓红

-

半导体

+关注

关注

339文章

31192浏览量

266320 -

晶体管

+关注

关注

78文章

10434浏览量

148540 -

AI

+关注

关注

91文章

40936浏览量

302512 -

蚀刻技术

+关注

关注

0文章

25浏览量

8023

原文标题:【技术干货】蚀刻技术如何发展以满足 AI 时代的需求

文章出处:【微信号:硬蛋芯力量,微信公众号:硬蛋芯力量】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

振奋!中微半导体国产5纳米刻蚀机助力中国芯

【转帖】干法刻蚀的优点和过程

请教碳化硅刻蚀工艺

AOE刻蚀系统

刻蚀端面Al Ga In As/AlInAs激光器的制作与特

关于刻蚀的重要参数报告

一文看懂刻蚀角度与ICP-RIE射频功率的关系

刻蚀工艺的参数有哪些

芯片制造中的湿法刻蚀和干法刻蚀

MEMS制造中玻璃的刻蚀方法

干法刻蚀机在精密光栅加工中的应用优势

垂直刻蚀在AI逻辑中的应用

垂直刻蚀在AI逻辑中的应用

评论