优势

1

EMX 3D Planar Solver 助力客户实现准确、高容量的 EM 分析,确保硅流片一次成功,加快产品上市

2

EMX 3D Planar Solver 以出色的结果达到三星认证标准

中国上海,2023 年 11 月 15 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,CadenceEMX3D Planar Solver 现已通过 Samsung Foundry 的 8nm Low Power Plus(LPP)先进制程工艺认证。EMX Solver 是市面上首个获得此认证的电磁(EM)求解器,成功达到三星的各项认证标准。双方的共同客户可以安心使用 EMX Solver 用于先进节点设计,进行高度准确的高容量 EM 分析,避免不良寄生效应和串扰效应。Cadence 和 Samsung Foundry 此次最新合作将助力客户实现硅流片一次成功,更快将新产品推向市场。

要想顺利完成模块级和芯片级分析及签核,拥有一个经过代工厂认证的 EM 建模引擎非常重要。精确的 EM 模型是设计前沿应用 IC 的基础。三星在认证过程中制造并测量了各种配置的电感器,EMX Solver 在所有类别中都表现出了极高的准确度。

有了 EMX Solver,客户可以仿真大型电路模块,分析无源元件的 EM 行为特性,并分析片上寄生效应。该求解器可以分析先进节点工艺的制造效果,包括与宽度和间距有关的效果。EMX Solver 与所有 Virtuoso产品一起无缝集成在 Cadence 定制/模拟设计流程中,包括基于 AI 的 Virtuoso Studio,以及 Virtuoso Analog Design Environment 和 SpectreRF Option。

“通过与 Cadence 的长期合作,我们为客户提供了其所需的强大工具,实现先进节点设计硅流片一次成功,”三星电子代工设计技术团队副总裁兼主管 Sangyun Kim 说道,“我们之间建立了稳定的合作关系,确保客户可以使用 EMX 3D Planar Solver 加速完成我们 8nm LPP 制程技术的设计收敛。”

“如今的先进制程节点设计必须能够克服串扰效应,”Cadence 全球副总裁兼多物理场仿真事业部总经理 Ben Gu 说道,“准确、高容量的 EM 分析非常重要,可以保护这些设计免受不良寄生效应的影响。Cadence EMX 3D Planar Solver 进行的 EM 分析不仅是业界的黄金标准,现在更是通过了三星的认证,因此我们的共同客户可以继续信心十足地采用先进技术完成设计。”

EMX 3D Planar Solver 支持 Cadence 智能系统设计(Intelligent System Design)战略,旨在实现系统级芯片(SoC)卓越设计和系统创新。

有关 EMX 3D Planar Solver 的更多信息,请访问

www.cadence.com/go/EMXSolverCertification

(您可复制至浏览器或点击阅读原文打开)

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

往期推荐

Cadence 推出 EMX Designer,在片上无源元件综合上提供超过 10 倍的性能提升

Cadence 加强其 Tensilica Vision 和 AI 软件合作伙伴生态,为先进的汽车、移动、消费和物联网应用提供更好的支持

Cadence 推出 Allegro X AI,旨在加速 PCB 设计流程,可将周转时间缩短 10 倍以上

原文标题:Cadence EMX 3D Planar Solver 通过 Samsung Foundry 8nm LPP 工艺技术认证

文章出处:【微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

-

Cadence

+关注

关注

68文章

1029浏览量

147335

原文标题:Cadence EMX 3D Planar Solver 通过 Samsung Foundry 8nm LPP 工艺技术认证

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

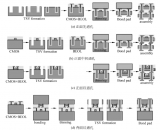

3D NAND中的Channel Hole工艺介绍

2D、2.5D与3D封装技术的区别与应用解析

技术资讯 I 多板系统 3D 建模,提升设计精度和性能

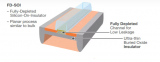

SOI工艺技术介绍

Cadence AI芯片与3D-IC设计流程支持台积公司N2和A16工艺技术

iTOF技术,多样化的3D视觉应用

索尼与VAST达成3D业务合作

3D 共聚焦显微镜 | 芯片制造光刻工艺的表征应用

Cadence EMX 3D Planar Solver 通过 Samsung Foundry 8nm LPP 工艺技术认证

Cadence EMX 3D Planar Solver 通过 Samsung Foundry 8nm LPP 工艺技术认证

评论