PLL芯片对电源的要求有哪些?

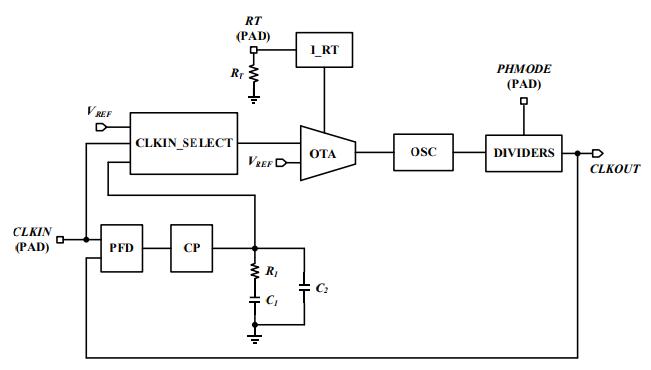

PLL芯片是广泛应用于电子电路中的一种重要的芯片,它主要用于频率合成、时钟信号的处理和数据传输等方面。在应用中,PLL芯片对电源的要求非常高,以确保系统的稳定、精度和可靠性。本文将从电源的几个方面详细介绍PLL芯片对电源的要求。

1. 电源电压范围与电源纹波

PLL芯片的电源电压通常在2.5V到5V之间,因此要求电源的输出电压稳定在这个范围内。同时,在设计电源时,需要评估电源的纹波,以保证电源纹波不影响PLL芯片的工作。通常,电源的纹波要求低于50mV。

2. 电源噪声

PLL芯片对电源噪声非常敏感,因此要求电源的噪声尽可能小。PLL芯片的工作频率通常在几百MHz到几GHz之间,因此电源的噪声幅度要求小于10mV。

3. 电源稳定性

PLL芯片对电源稳定性也非常敏感,要求电源输出稳定性高。稳定性不仅包括电源电压的稳定性,还包括电源的负载能力和瞬态响应能力。如电源的瞬态响应能力不足,则可能会影响PLL芯片的工作。

4. 噪声耦合

在电子电路中,噪声耦合是一个常见的问题。PLL芯片中,噪声耦合可能影响PLL的锁相环环路增益和相位噪声等性能指标。为了避免这种情况的发生,设计电源时应避免电源与其他信号线交叉布线,同时通过布局、过滤和隔离等措施降低噪声耦合。

5. 电源管理

PLL芯片通常需要提供多种电源,以满足其不同的工作模式。如低功耗模式、睡眠模式等。因此,电源管理对于PLL芯片的应用非常重要。合理的电源管理可以节省功耗,延长电池寿命,并提高系统可靠性。

6. 其他要求

PLL芯片还对电源输出的波形、频率和相位等参数设置有一定的要求。如电源的输出波形应为纯净、稳定、无毛刺的正弦波或方波。同时,为了确保PLL的稳定性,电源的频率和相位应与PLL的输入频率和相位匹配。

综上所述,PLL芯片对电源的要求非常高。在设计PLL电路时,应考虑到电源的稳定性、噪声、纹波和管理等多方面的因素。只有合理满足这些要求,才能保证PLL芯片稳定、精确和可靠的工作。

-

电源电压

+关注

关注

3文章

1261浏览量

26518 -

时钟信号

+关注

关注

4文章

510浏览量

30086 -

PLL电路

+关注

关注

0文章

94浏览量

7140

发布评论请先 登录

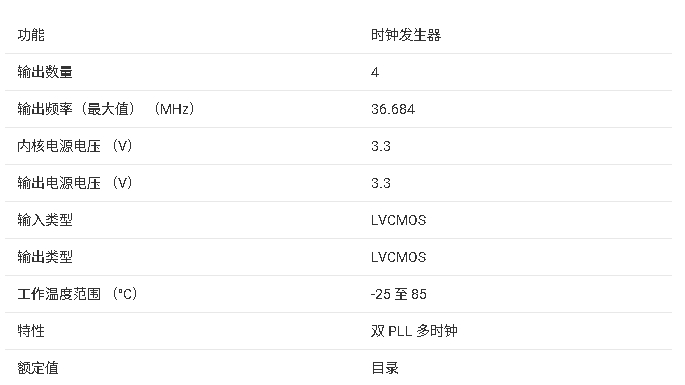

Texas Instruments PLL1705/PLL1706:3.3-V 双 PLL 多时钟发生器的卓越之选

Texas Instruments PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

德州仪器PLL1705/PLL1706:低抖动多时钟发生器的卓越之选

探究PLL1705与PLL1706:3.3V双PLL多时钟发生器的卓越性能

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

德州仪器PLL1707和PLL1708:低抖动多时钟发生器的卓越之选

电流传感器供电有要求么?适配不同电源么?

汉思新材料:芯片底部填充胶可靠性有哪些检测要求

ASP4644电源芯片 Buck变换器双PLL频率同步机制分析

PLL1708双PLL多时钟发生器技术文档总结

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

易灵思 FPGA TJ375的PLL的动态配置

PLL用法

PLL芯片对电源的要求有哪些?

PLL芯片对电源的要求有哪些?

评论