在一个我们越来越多地在虚拟空间工作、学习、购物和玩耍的世界中,对上游连通的需求正在成倍增长。 多个系统操作员(MSO)已经看到他们共同轴心网络的能力 — — 以及他们的客户 — — 已经从实施“数据过电缆服务接口规格 ” ( DOCSIS ) 3.1中受益。 DOCSIS使得现有混合纤维-轴心基础设施的高带宽数据传输成为可能。

DOCSIS 3.1已将该行业提高到1.2千兆赫,但是,如果MOS要跟上全世界消费者的需求,针头需要提高速度和速度。 扩展频谱DOCSIS 4.0将进一步将频率提高到1.8千兆赫,这是支持传统捍卫民主阵线氢氟碳化合物网络更高上游数据率的建筑结构的下一步。

有了DOCSIS 4. 0的核准,我们就可以指望它的支持和设备在2024年初开始装运。 这个版本定义了四个新的分割,扩大了频谱范围,这可能导致令人兴奋的新应用。 上传重活动,如现场流和内容创建将大大加快。 但是,它也给开发商建造上游应用的扩增器带来了挑战,因为它们现在需要支持更高的频段。

“短期乐队分裂项目将开始让位于长期的DOCSIS 4.0升级,特别是在北美市场,在北美市场,操作者正寻求提高能力,并跟上纤维ISP的步伐。” 副总裁兼Dell'Oro集团分析员Jeff Heynen说,“这些升级将大大增加光学节点、放大器和被动设备,包括水龙头和硬线分裂器的开支,”又说“这些升级将大大增加光学节点、放大器和被动设备,包括水龙头和硬线分割器的开支。”1 .

这个博客提供《科尔沃设计峰会》网站的节录,利用灵活结构满足DOCSIS 4.0 高带宽上游要求这解释了DOCSIS 4. 0及其新的上游选项, 并讨论了数据输送量和带宽考虑。如何提高CATV放大器的下游带宽和上上游能力并提高其效率,这绝对值得检查, 特别是如果你在研究下一代技术 和推动这些技术的进步。

DOCSIS 4. 0 频谱选项

DOCSIS 4. 0 频谱选项比以前的迭代大为改善。 有了这个最新版本,用户现在可以享受最多10千兆比特的下载速度和最多6千比特的上传速度,这大大加快了速度,大大提升了延缓速度。 为了加快速度, DOCSIS 4. 0 还包括扩展频谱技术,将上游频谱扩大到684兆赫,下游频谱扩大到1.8千兆赫。 这一扩大频谱为数据传输开辟了更大的路径,使得数据传输速度更快、效率更高。

扩展频谱在DOCSIS4.0中提供了四个新的分解选项,增加了执行灵活性,增加了超高分解。使用频率分解(DFD),将上游和下游分开。具体使用案例的性质将决定哪些分解对上游和下游需求有利。

使用 96 MHz 区块 Orthogoal Connical Division 多重访问(OFDMA ) , 让多个客户共享一条上游接入通道,使用时间划分的多种访问格式技术。 操作员可以选择最适合其需要的分割。 204 MHz 和 396 MHz的分割很可能最为流行,提供了2.5 - 3.0 Gbps上游和10 Gbit/sec下游的合理平衡率。

DOCSIS 技术革新

Qorvo为DOCSIS 3.0、DOCSIS 3.1和DOCSIS 4.0提供了完整的RF解决方案组合,并利用其广泛的工业经验提供支持,以加快设计、制造和测试。

对于下游应用,其用于DOCSIS3.1和FDX DOCSIS4.0网络高功率纤维深度应用的最新产品是QPA3260或QPA3246电源双重混合体,它提供最高线性输出功率,最高至1.2千兆赫;对于捍卫民主阵线DOCSIS4.0,QPA3314电源双重混合体相当于支持1.8千兆赫所需的应用;QPA3260、QPA3246和QPA3314以工业领先的线性提供23 dB收益。

Qorvo的专用制造业务支持了每年生产数百万件产品所需的高级自动化水平,以及CATV市场所要求的质量和可靠性;此外,该公司对CATV系统的测试非常全面,产品具体;为了确保一贯质量和可靠性,Qorvo在其CATV混合放大器生产的100%中安装了小型信号和扭曲测试;此外,测试包括多载体(复合)扭曲测试,包括遗留的模拟装货或用单载器QAM或ODM频道进行的最新数字装货。

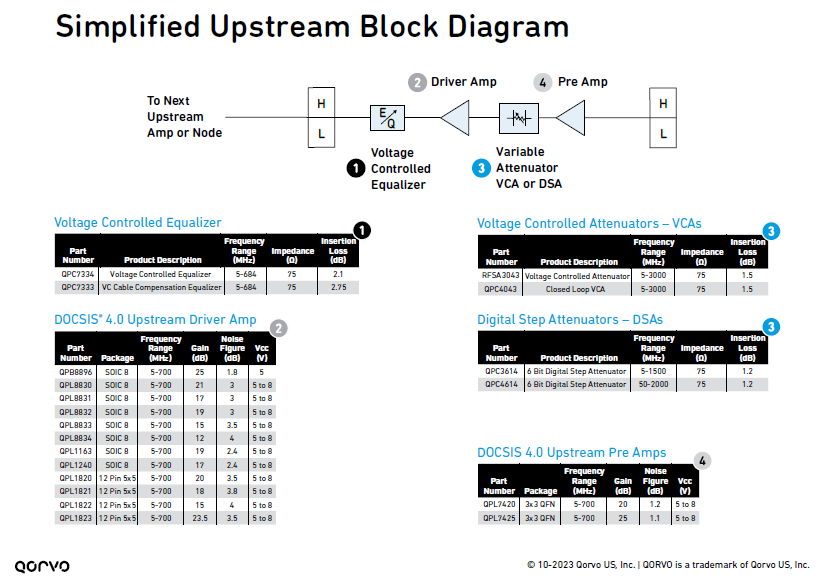

对于上流应用, Qorvo 提供了一种构件方法, 使客户可以在终端应用中将设备安装到需要的地方。 这些装置包括小形式因子、 低电耗放大器加上减速器、 平衡器和开关。 它们使MOSOs能够提供5兆赫至684兆赫的全带宽, 在任何分割时满足 DOCSIS 4. 0 的要求 。

Qorvo的装置系列包括单端和差分放大器,可以覆盖DOCSIS的整个上游波段。Qorvo还提供一组由电压控制的加速器和数字级加速器。有创意的上游变异平衡器系列以线性或有线补偿版本提供。预定于2024年释放的新装置对于低于396兆赫的分解和反向电缆补偿选项提供的损失要少得多。

图2. Qorvo的 " 构件 " 方法使MOSO能够提供DOCSIS 4.0和其他扩展频谱应用。

为新应用铺路

总的来说,DOCSIS 4.0预计将大大改善有线网络基础设施,使范围广泛的应用能够要求更快的互联网速度、提高能力和提高网络效率。

DOCSIS 4.0设计放大器需要仔细考虑若干要求:频率范围提高、输出功率提高、噪音性能提高。利用灵活结构满足DOCSIS 4.0 高带宽上游要求和白皮书,如何提高CATV放大器的下游带宽和上上游能力并提高其效率更详细地解释如何满足这些更高的上游需求。

审核编辑 黄宇

-

频谱

+关注

关注

7文章

905浏览量

47167 -

DOCSIS

+关注

关注

0文章

15浏览量

8754

发布评论请先 登录

晶振的频率误差可以修正吗

通往AGI之路道阻且长:为未来智能筑牢算力基础

用于 DOCSIS 3.0 上行路径的可编程增益放大器 skyworksinc

Cocos引擎携手Google Play共拓全球化新路径

瑞芯微RK3506开发板必备攻略之Qt应用开发手册(下),触觉智能工控嵌入式方案商

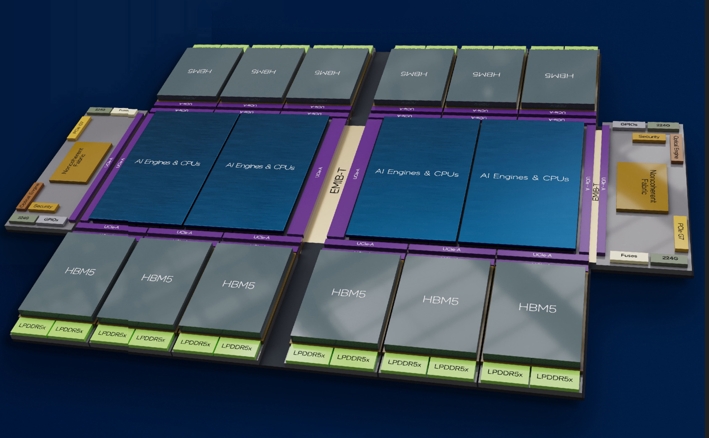

英特尔展示封装创新路径:提高良率、稳定供电、高效散热

在matlab中如何计算含有第一类修正的贝塞尔函数的积分算不出的问题?

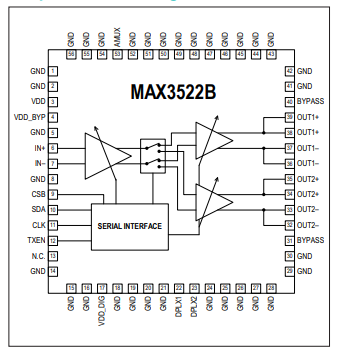

MAX3522B DOCSIS 3.1可编程增益放大器技术手册

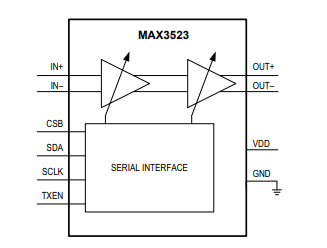

MAX3523低功耗DOCSIS 3.1可编程增益放大器技术手册

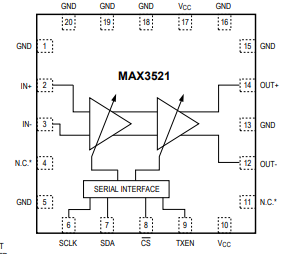

MAX3521 DOCSIS 3.0 Plus上行放大器技术手册

零主栅(0BB)技术降低银耗的路径:IFC工艺与焊接型方案的对比研究

创新“ 修正” 通往 DOCSIS 4. 0 的路径

创新“ 修正” 通往 DOCSIS 4. 0 的路径

评论