为什么源极退化电阻会使共源级的增益变小呢?

共源级放大电路是最常用的放大电路之一,其具有简单的电路结构、高输入电阻、低输出阻抗等优点。其常用的场合,如工业、农业、医疗等领域,均要求放大电路具有高增益、高性能和可靠性。在实际应用中,为了提高共源级放大电路的增益,不少设计者采用了源极退化电阻,但是为什么会使共源级的增益变小呢?我们来探讨一下这个问题。

首先,我们来看一下共源级放大电路的基本结构。共源级放大电路由三个元件组成:信号源,晶体管和负载电阻。晶体管的漏极与地相连,电源通过电阻分压方式施加到晶体管的源极,即源漏极之间的电阻就是源极电阻。这个电路结构被广泛应用是因为它能够实现放大、过滤、偏置等功能。

为了提高晶体管的放大能力,通常会加入源极退化电阻,在源极电路中串接一个电阻,从而限制源电流,增加放大器的动态范围。但是,在加入源极退化电阻后,共源级放大电路的增益却降低了。具体的原因有以下几个:

1.源电流降低:源极退化电阻所导致的源电流降低,使放大器的增益下降。由于源电流是影响晶体管工作状态的重要参数,所以其大小对放大器的性能影响非常大。

2.输入阻抗降低:晶体管源极退化电阻引起的源电流变化会使其输入阻抗降低,从而导致放大器的输入信号被消耗掉,使得输入信号不能被有效的放大。

3.输出阻抗增加:源极退化电阻一定程度上增加了晶体管的输出阻抗,这也会影响放大器的性能。由于输出阻抗的增加会降低输出电信号的有效值,同时增加负载电容的影响,所以原本应该被放大的输出信号会因此被耗散掉。

4.噪声增加:在源极电路中加入一个退化电阻可以提高晶体管的抑制分布噪声的能力,但也会因此增加内部噪声。由于退化电阻会增加输入噪声,所以增益会有所下降,同时伴随着内部噪声的增加。

总之,源极退化电阻的引入虽然能够一定程度上提高晶体管的放大能力,但对于共源级放大电路的增益是一个显著的影响因素。因此,设计者应该根据具体的应用场景来综合考虑增益、带宽、噪声等方面的要求,以达到一个相对理想的电路性能。

-

放大器

+关注

关注

146文章

14362浏览量

222503 -

放大电路

+关注

关注

105文章

1820浏览量

109956 -

晶体管

+关注

关注

78文章

10439浏览量

148605 -

负载电阻

+关注

关注

0文章

112浏览量

8687

发布评论请先 登录

长电科技成功完成晶圆级射频集成无源器件工艺验证

高端电流检测芯片,FP135,增益可通过外部电阻自由调整,输出电压与负载检测电流成线性变化

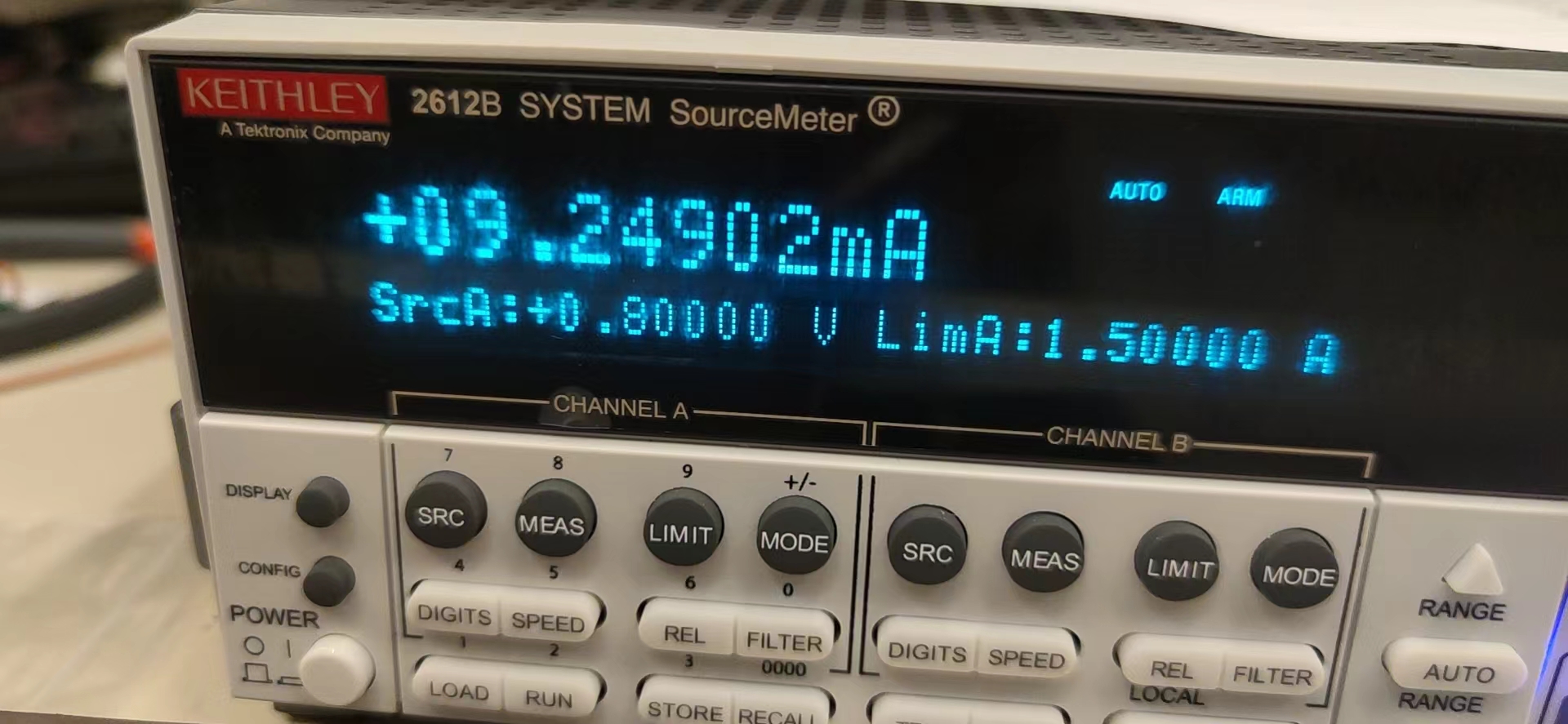

源表应用拓展:四探针法测电阻率

新品 | CoolSiC™ MOSFET M1H共源配置62mm模块

如何使用源表对元器件的IV曲线进行测试?

电子产品如何区分有源和无源

碳化硅双极退化:材料的本征局限还是工艺难题?

浮思特 | SiC MOSFET 封装散热优化与开尔文源极结构

有源滤波器与无源滤波器的区别

源漏扩展结构概述

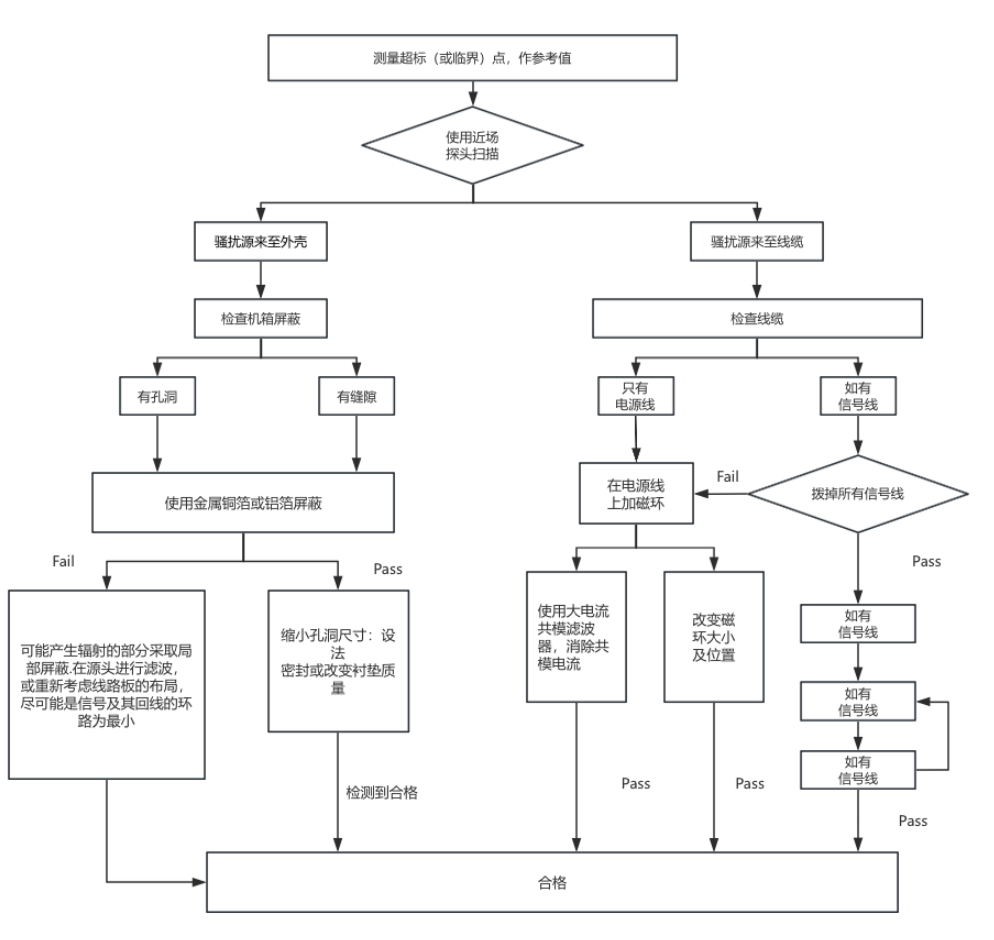

时源芯微 近场探头确定干扰源的位置

为什么源极退化电阻会使共源级的增益变小呢?

为什么源极退化电阻会使共源级的增益变小呢?

评论