怎么检查景芯SoC的低功耗power domain有没有错误?

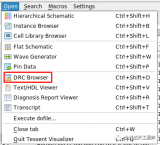

答:推荐使用verifyPowerDomain来检查:

verifyPowerDomain

-xNetPD 查有没有level shifter违例

-isoNetPD查有没有isolation违例

-bind 检查power domain的library binding情况,也就是检查是否所有的cell 都被link 到了对应的库上

-gconn 检查有无instance的pg连接错误

-retention 检查retention错误

请思考,为什么没有检查power switch?

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SoC芯片

+关注

关注

2文章

672浏览量

37270 -

Cell

+关注

关注

0文章

19浏览量

17781

原文标题:低功耗power domain的检查

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

【启芯】低功耗视频解析

低功耗设计是芯片设计的关键技术,本视频简要介绍了SoC芯片设计中常见的低功耗设计技术,验证难点。欢迎加入启芯QQ群:275855756。 学习芯片设计,可以参考:启

发表于 11-03 08:44

UPF流程与电源域Power Domain详解

UPF流程是怎样的?怎样使用UPF0对RTL进行动态/静态功耗验证?什么是电源域Power Domain?如何对电源域Power Domain

发表于 10-20 07:32

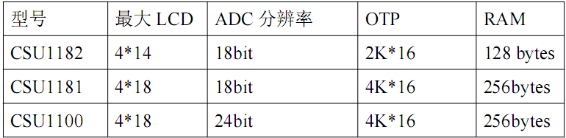

芯海科技最新推出CSU11xx系列超低功耗衡器SoC芯片

芯海科技最新推出CSU11xx系列超低功耗衡器SoC芯片

芯海科技最新推出CSU11xx系列超低功耗衡器

发表于 02-16 15:29

•1354次阅读

打印机不打印,也没有错误提示故障如何解决?

打印机不打印,也没有错误提示故障如何解决?

一. 现象描述从计算机上发送打印命令后,打印机不打印,也没有出错信息提示。

发表于 03-18 11:42

•2.6w次阅读

DVFS hierarchy低功耗A72后端实战案例

本项目采用hierarchy UPF方式划分了7个power domain、voltage domain,指定power switch cell,其中包括SWITCH TRICKLE、

Synopsys推出一款低功耗静态规则检查工具—VCLP

VCLP(VC Low Power)是Synopsys提供的一款低功耗静态规则检查工具,它能够帮助验证和清洁IEEE 1801 Unified Power Format (UPF)

芯科科技推出低功耗蓝牙Lite版SoC

全球领先的安全、智能无线连接技术提供商Silicon Labs(芯科科技),近日宣布了一项重要产品发布——BG22L和BG24L片上系统(SoC),专为低功耗蓝牙®(Bluetooth® LE)连接

怎么检查景芯SoC的低功耗power domain有没有错误?

怎么检查景芯SoC的低功耗power domain有没有错误?

评论