概要

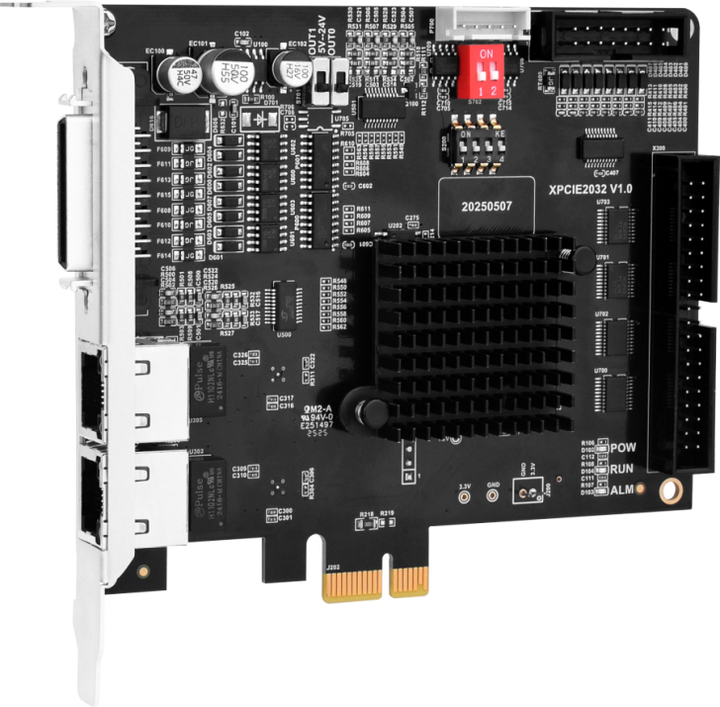

QT7331是一款高分辨率、高采样率的ADC+DAC FMC子板。它同时支持2路14位3.0/2.6/2.0GS/s的A/D通道输入和2路16位12.6GS/s的D/A通道输出,全功率模拟-3dB输入带宽可达9GHz。QT7331A为3GSPS采样率,QT7331B为2.6GSPS采样率,QT7331C为2GSPS采样率。本板卡支持触发输入或者输出;内参考、外参考、外时钟三种时钟方式,可通过SPI总线实现时钟源选择。通过参考时钟可实现多个板卡的同步。

QT7331板卡的电气与机械设计依据FMC标准(ANSI/VITA 57.1),通过一个高密度连接器(HPC)连接至FPGA载板。前面板I/O装配6个SSMC同轴连接器。QT7331设计了风冷和导冷版本,可适应于多种FPGA载板,如 Xilinx和Altera等通用载板,以进行高性能的算法计算。

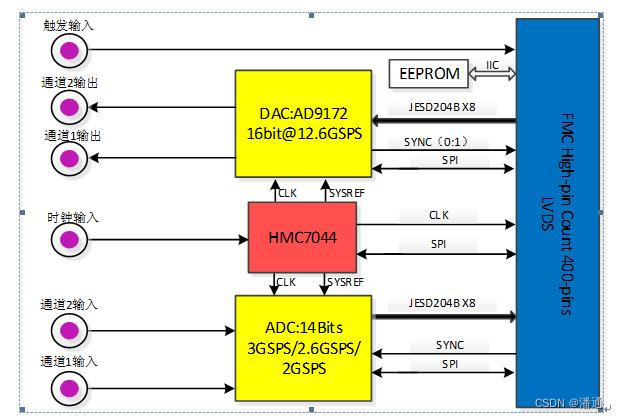

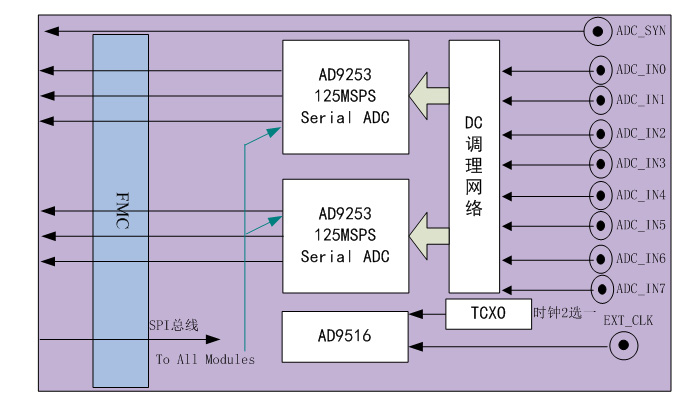

整体架构流程

更多信息请加weixin-pt890111获取

技术指标

6个SSMC的连接器,其中2个分别为模拟信号输入1(AD0)和模拟信号输入2(AD1);2个分别为模拟信号输出1(DA0)和模拟信号输出2(DA1);一个为外部时钟输入(CLK);一个为触发输入或者输出(TRG)

采样频率:2通道16bits 12.6GS/s DA和

QT7331A:2通道 14bit 3GS/s AD;

QT7331B:2通道 14bit 2.6GS/s AD;

QT7331C:2通道 14bit 2GS/s AD;

输入带宽:全功率模拟输入带宽(-3 dB):9GHz

ADC输出和DAC输入均为JESD204B标准数字接口

适应范围:完全符合Vita57.1规范,包括结构件,子卡尺寸,面板连接器,正反面器件的限高等,大大提供了子卡的通用性和适配性

多种散热方式:风冷或导冷

模拟输入和输出均为AC耦合

板载温度监控电路

时钟选择灵活:内部时钟、外部时钟选择可由载板控制

HPC高引脚数连接器

工作温度:商业级0℃~ +70℃ ,工业级 -40℃~ +85℃

其他支持

提供Verilog bit文件

JESD204B Core,可包括BSP

性能与指标

模拟输入:

(1)输入耦合方式:交流耦合;

(2)ADC芯片数量:1片;

(3)全功率带宽 (-3 dB):9.0GHz;

(4)满量程输入电压:

QT7331A、1.13Vpp ~2.04Vpp,典型值1.7Vpp ;

QT7331B/C、1.1Vpp ~2.0Vpp,典型值1.7Vpp ;

(5)输入阻抗:50 Ohm;

(6)连接器: SSMC;

模拟输出:

(1)输出耦合方式:交流耦合;

(2)DAC芯片数量:1片;

(3)全功率输出带宽:6GHz ;

(4)满量程输出电流:16~26mA可调;

(5)输出阻抗:50 Ohm;

(6)连接器: SSMC ;

时钟:

(1) 支持内参考或外部参考:

10MHz,功率-5~10dBm

(2) 支持外部采样时钟最高:

3 GHz; 功率-5~10dBm

(3) 输入阻抗:50 Ohm;

(4) 耦合方式:交流耦合;

(5) 连接器: SSMC ;

触发:

(1)触发输入:3.3V CMOS/TTL;

(2)触发输出:3.3V CMOS/TTL;

(3)最大频率:200MHz;

(4)连接器: SSMC ;

审核编辑 黄宇

-

连接器

+关注

关注

102文章

15919浏览量

145396 -

FMC

+关注

关注

0文章

111浏览量

20627

发布评论请先 登录

FMC子卡模块设计方案:FMC160-两路14位400Msps AD,两路16位400Msps DA FMC子卡模块

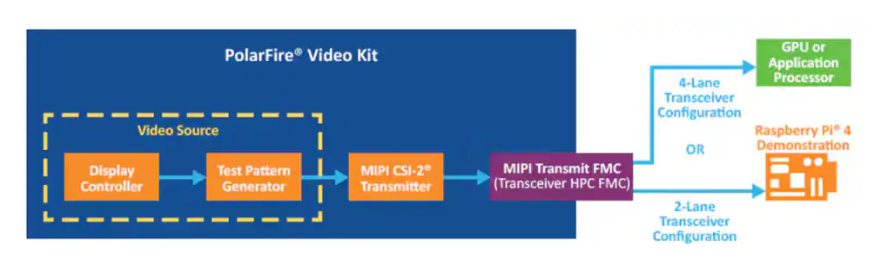

基于Microchip MIPI CSI-2 Transmitter FMC卡的技术解析与应用实践

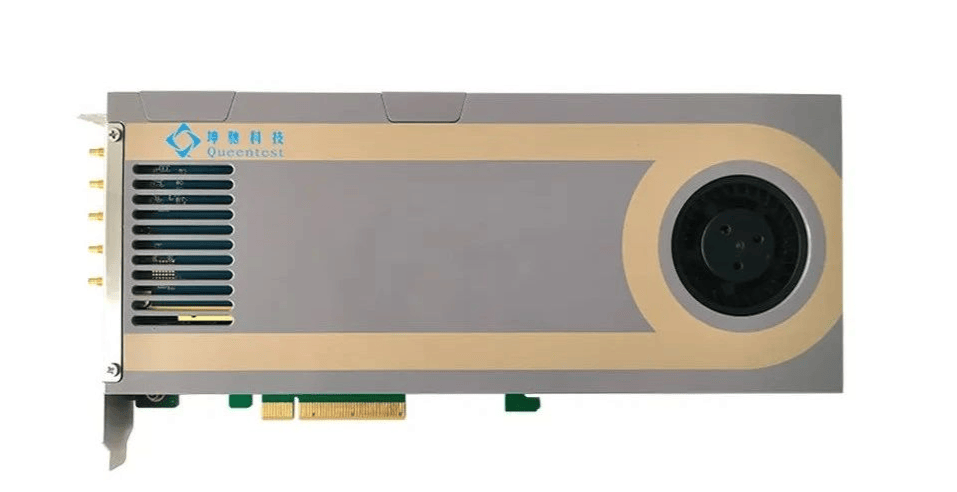

坤驰科技——双通道3GS/s高速数据采集卡

【FMC213】青翼凌云科技基于 VITA57.1 标准的 8 路 SFP+光纤通道数据传输 FMC 子卡模块

【FMC214】青翼科技基于 VITA57.1 标准的 4 路 3G/6G/12G SDI 高清视频传输 FMC 子卡模块

FMC子卡设计方案:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡

泰克TBS2000B数字存储示波器通道数量选择指南:从基础配置到场景化应用

EEPROM芯片内部的1路14bit ADC, ADC精度受使用通道数和采样率是怎么样的?

Why FPGA开发板喜欢FMC?

高速AD9172 AD9689 2通道 14bit 2GS/s FMC子卡

高速AD9172 AD9689 2通道 14bit 2GS/s FMC子卡

评论