被誉为「世界上最快的x86专业创客板」UP Squared的后继者,UP Squared V2保留了第一代UP Squared的优点,并于配备规格上进行了全面升级,性能更提升,同时更具成本效益。

在同样85×90mm(3.37"×3.54")的尺寸上,UP Squared V2的CPU性能提升了40%,拥有业界领先的高度扩展性和惊艳的I/O密度,在价格、性能或UP Squared社群上提供的外围开发选项方面都是无可匹敌的。

功 能 特 点

”

Part.

1

UP Squared V2采用Intel Celeron N6210/Pentium J6426处理器SoC(代号为Elkhart Lake),与UP Squared相比,CPU性能提高了40%,同时单线程性能提高了1.7倍,多线程性能提高了1.5倍。除此之外,UP Squared V2还配备了高达16GB的LPDDR4内存,数据处理速度更快,利于优化AI推理应用。

Part.

2

UP Squared V2配备第11代Intel UHD Graphics,性能是前一代的两倍,让UP Squared V2能通过HDMI 1.4、DP 1.2和eDP 1.3端口来支持多达三个同步4K显示器。

Part.

3

UP Squared V2加强了可扩展性,配备有M.2 2230 E-Key、M.2 2280 M-Key和SATA III插槽,支持AI、PCIe和Wi-Fi模块, 并透过板载TPM 2.0促进网安。

UP Squared V2拥有杰出的高密度I/O配置,接口也是用户友善设计,不再需要使用板上40针HAT的I2S,只需专用的高清音频连接器,即可将音频功能整合进实际应用。

UP Squared只配备了10针的UART,而升级版的UP Squared V2多增加了额外的RS-232/422排针,为工业应用提供了更友善的使用接口,同时RS-232/422引脚更进一步延伸了数据传输距离。

产 品 简 介

”

Intel Pentium Celeron SoC 处理器

板载 LPDDR4 内存,最大支持 16 GB

板载 eMMC 存储,最大支持 64 GB

千兆以太网 (全速) RJ-45 x 2

USB 3.2 Type A x 3

40 针 GPIO x 1

DP 1.2 / HDMI 1.4b / eDP 1.3

RS232/422 排针 x 1

M.2 2230 E-Key x 1

M.2 2280 M-Key x 1

SATA3 x 1

TPM 2.0

12V 直流输入, 5A

-

处理器

+关注

关注

68文章

20329浏览量

254863 -

cpu

+关注

关注

68文章

11326浏览量

225873 -

X86

+关注

关注

5文章

300浏览量

45565

发布评论请先 登录

uM-FPU V2 浮点协处理器:功能特性与应用指南

AA Boost Module V2:便捷的电源解决方案

如何在 VisionFive v2 上使用外部 GPU?

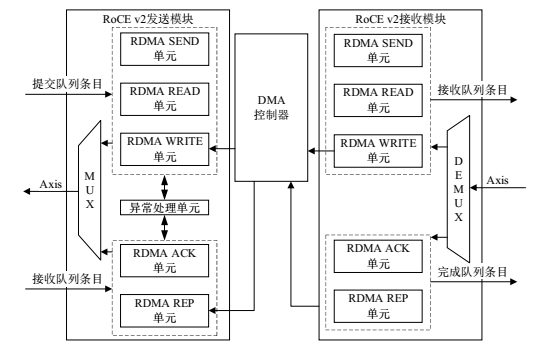

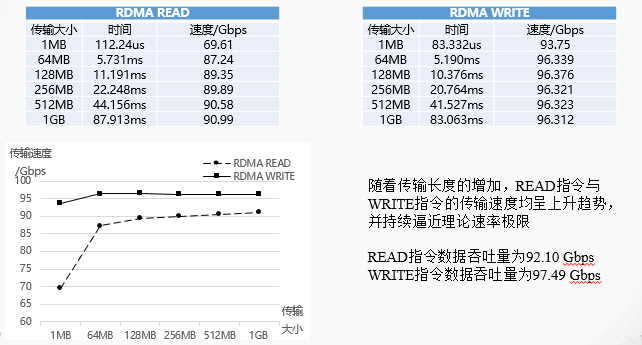

RDMA设计46:RoCE v2原语功能:单边语义

RDMA设计44:RoCE v2原语功能验证与分析

RDMA设计37:RoCE v2 子系统模型设计

RDMA设计30:RoCE v2 发送模块2

RDMA设计29:RoCE v2 发送及接收模块设计2

RDMA设计28:RoCE v2 发送及接收模块设计

RDMA设计19:RoCE v2 发送及接收模块设计

AURIX™ Audio Application Kit for AURIX™ lite Kit V2 深度解析

uIO-Stick v2 用户指南:设计、应用与安全要点

RDMA设计5:RoCE V2 IP架构

思尔芯原型验证系统助力昆明湖V2成功启动GUI OpenEuler

RDMA over RoCE V2设计1:为什么要设计它?

UP Squared V2全新升级

UP Squared V2全新升级

评论