设计目标:

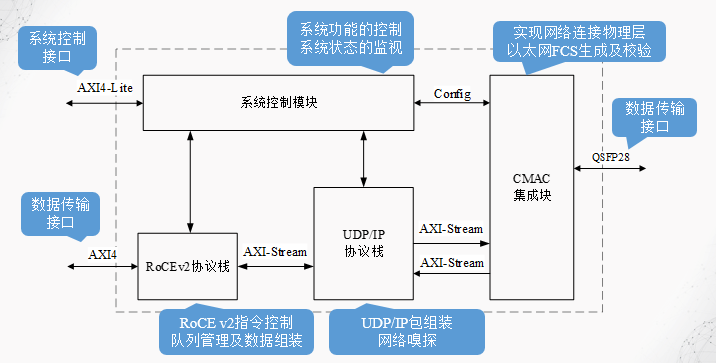

RDMA技术采用无感传输机制,消除传统网络传输中需要CPU介入下的多重数据复制与内核参与环节,实现直接跨主机内存访问的机制。其设计目标为优化分布式环境下的数据传输效率,降低CPU负载。

RoCEv2基于标准网络的以太网、网络层和传输层(UDP)协议,这可以使得RoCEv2的网络流量可以经过传统的网络路由器路由。之前RDMA简介1~8有对相关资料介绍,这里强调的是:它是目前性价比最高的RDMA实现方式,虽然IB模式在一些高校应用较多,但因为它的专有特性,价格较贵,难广泛用于产品中。

设计思考

基于PC-PC或GPU-GPU之间RDMA设计已有较多厂商投入,虽然有的大厂投入几年后折羽而归,但不影响PC领域成熟应用产品的推广。这里主要讨论在FPGA上设计RDMA over RoCE V2,虽然已有xilinx的ernic应用,但是性价比以及国产化需求还是有其发展空间。这里讨论设计需要着重考虑地方:

1)通用性

一般项目中的数据采集前端基于 FPGA 进行开发。第一,各数据采集前端使用的 FPGA型号各不相同,需要实现的设计能够工作在多种不同型号 FPGA 上;第二,为了降低设计部署成本,需要实现的设计能够在脱离 CPU 控制下独立运行和控制传输;第三,一些厂商不愿意采用私有化协议,主要是考虑其被迫被捆绑,私有协议也就意味着难以与其他系统兼容,一旦存在功能或性能设计不足,只能前功尽弃。考虑到以上三点需求,设计时建议采用纯逻辑电路实现。

2)高性能

数据采集前端得到的数据,数据块大小不固定、数据速率也不尽相同。同时对于数据传输的需求也并不相同,存在一对一、一对多、多对多等多种传输情况。面对大量离散数据时,需要增加 RDMA 队列数量及深度,同时灵活调整数据包大小来保证传输性能,而面对大量连续数据请求时,则可通过减少队列数量的方式来降低功耗。

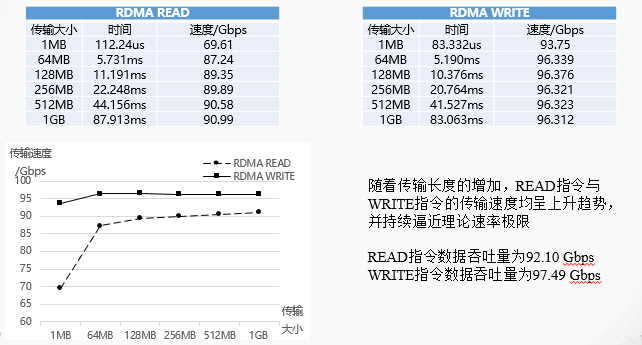

同时,在面对一对多或多对多传输需求时,则要求设计能够正确地处理网络拥塞情况并正确地进行流量控制。因此,需要实现完备的队列管理及拥塞处理功能,在满足性能要求的同时适应不同的应用环境。具体要求为使用 QSFP28 及以上光纤接口,在传输不小于 256 MB 的连续数据时,数据传输速率不小于 90 Gbps。在传输包大小为 4KB 时,延迟不高于 10 μs、包吞吐量不小于 1000 kpps。这里也只是简要指标分析,上面这些指标在PC-FPGA之间实现较容易,在FPGA-FPGA之间还是有一些挑战。这也反映竞争环境下适者生存,最后生存的不大可能是大多数。虽然我们设计的IP性能(包括我们A, FPGA-FPGA)早已超越这些指标,相信其他厂家也能满足。

3)易集成、用户操作简便

实现的 RDMA 协议栈和控制逻辑,应能够简易地集成到应用生产环境中,并提供简易的用户操作方式来实现数据传输控制及队列控制。因此,设计需要使用标准化接口,同时尽可能地降低资源占用率,并具备 DMA 数据传输功能。

4)稳定性

这里强调的是,如果只是预研项目,就不大需要考虑稳定性,其特有的功能和性能才是项目需要重点解决的。但是作为商用IP,就需要考虑其稳定性,不能出现上次可以,这次就工作不正常,或者性能下降明显情况。

它涉及到几个因素:

1)高速接口的匹配性:RDMA数传通道一般采用AXI总线,它需确保IP核与FPGA的如AXI4-Stream/AXI4-Lite等兼容性,避免因协议不匹配导致传输错误;

2)时序优化:一般它需要跨时钟域设计,因此对时钟同步、信号路径规划和资源分配等关键因素需要重点考虑;

3)存储资源分配:合理设计FIFO深度,(一般采用2的整数次幂深度设计)和RAM块数量,避免因资源不足导致数据丢失或性能下降。

这里给出IP读写性能情况:

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

链接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

审核编辑 黄宇

-

FPGA

+关注

关注

1655文章

22283浏览量

630290 -

高速传输

+关注

关注

0文章

38浏览量

9269 -

RDMA

+关注

关注

0文章

85浏览量

9558

发布评论请先 登录

RDMA设计7:系统控制模块设计

RDMA设计6:IP架构2

RDMA设计4:技术需求分析2

RDMA设计1:开发必要性1之设计考虑

RDMA over RoCE V2设计1:通用,稳定及高性能!

RDMA over RoCE V2设计2:ip 整体设计考虑

RDMA over RoCE V2设计1:为什么要设计它?

RDMA over RoCE V2设计1:为什么要设计它?

评论