01

绘制精细电路的第一步

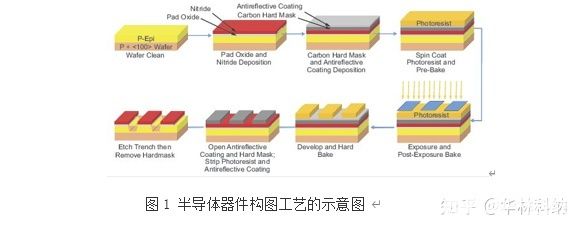

金属-氧化物半导体场效应晶体管(MOSFET)的革命,让我们可以在相同面积的晶圆上同时制造出更多晶体管。MOSFET体积越小,单个 MOSFET的耗电量就越少,还可以制造出更多的晶体管,让其发挥作用,可谓是一举多得。可见,制造更小的MOSFET成了关键因素,并且想制成微细的电路,第一步就是“绘制”。

我们以饼干烘培做比喻来说明一下。假设想在面饼上压出数百个“幸福之翼”形状的饼干,一个一个做显然是很费力的,那要采用什么样的方法呢?

最好的办法就是利用模具,先把面饼擀平擀宽烘培后,用饼干模具(印章)压出想要的形状来。这样一来,一次压出100个饼干也不会太吃力。

再想一想,如果想把做好的饼干卖给孩子们,就得把饼干做得更小,那要怎么办?当然,饼干模具就要变得更小。本篇文章的主角就是相当于“饼干模具”的“***”。半导体制造与饼干烘培的最大区别在于,MOSFET越小,在相同面积的晶圆上,就可以制造出越多的MOSFET,这也就越受客户的青睐。两个小的MOSFET远比一个大的MOSFET更实用。

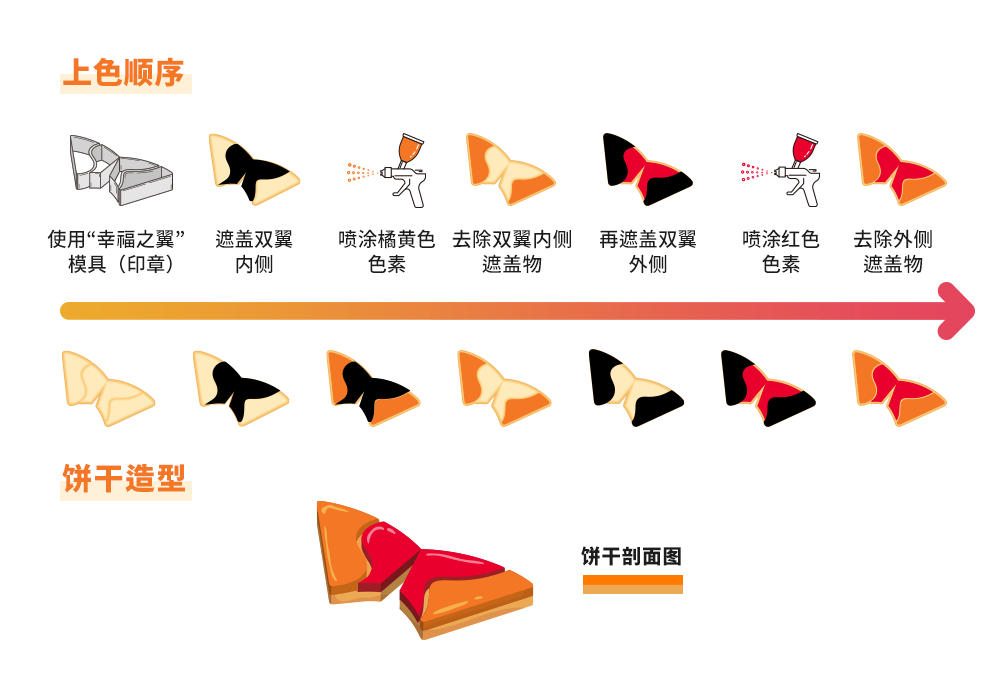

半导体的制造其实就是不断重复上述工艺。继续以做饼干为例,如果糕点师想给“幸福之翼”饼干上色,要怎么办?

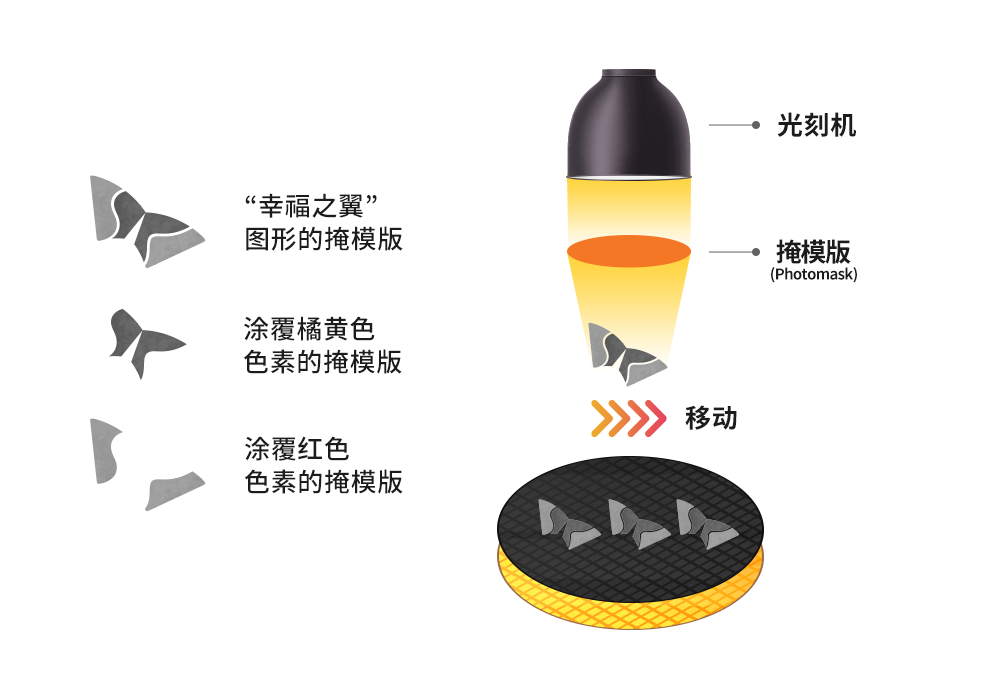

▲ 图2: 给“幸福之翼”饼干上色的顺序

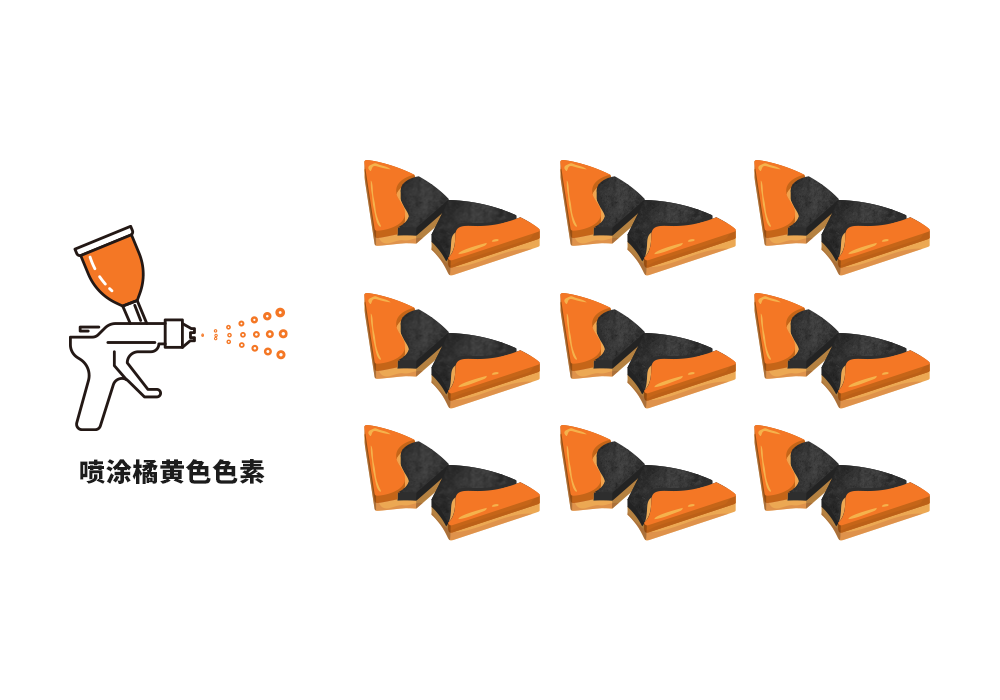

▲ 图3: 如果能成批向数十个饼干喷涂色素,速度就会更快。

图2和3揭示了快速做出更多饼干的方法:先在面饼上压出许多造型相同的饼干,然后遮盖不想上色的部位,再向整个面饼喷涂色素。这样就可以轻松快速地做出特定造型和颜色的饼干了。说到这里,也许善于思考的读者就要发问:这么多的双翼内侧黑色遮盖物(见图3),要怎么制作?下面我们会说到这一点,这其实就是光刻工艺的核心。

饼干只有面饼和色素(红色、橘黄色)两层,但半导体结构却复杂得多,由数十层堆叠组成:包括电子元件层还有层层堆叠的金属布线层等。这也是我们说光刻是半导体制程关键工艺的原因。

02

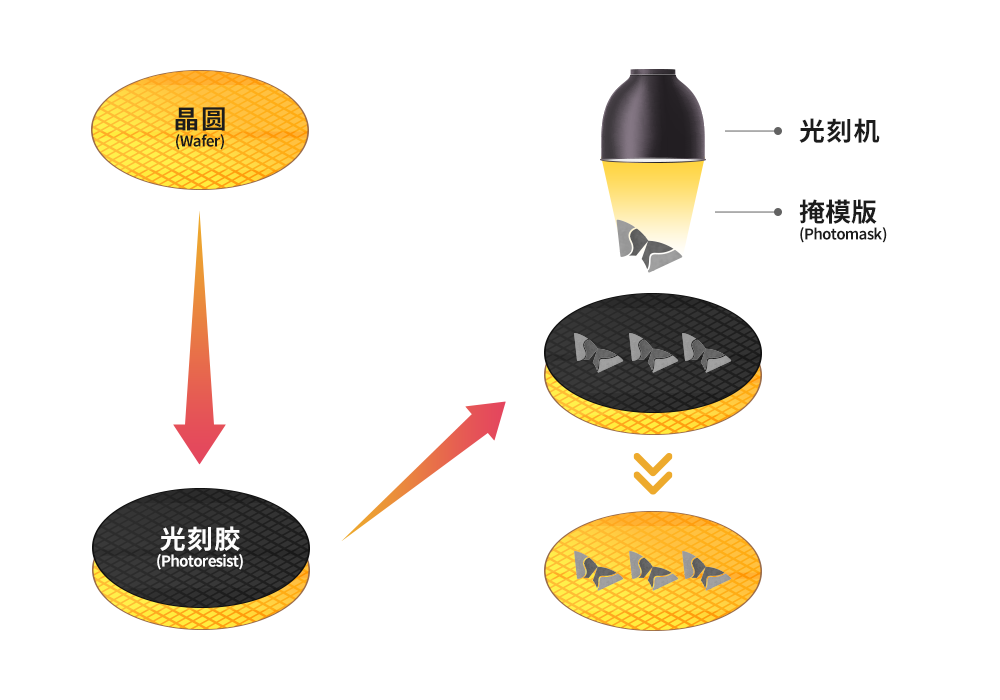

模具的制作过程:光刻工艺

半导体制造商把上面我们所说的制作饼干模具(遮盖物)的过程叫做光刻工艺。光刻工艺的第一步就是涂覆光刻胶(Photoresist)。光刻胶经曝光后化学性质会发生变化。具体而言,就是在晶圆上涂覆光刻胶后,用光(激光)照射晶圆,使光刻胶的指定部分的性质发生改变。

▲ 图4: 光刻工艺基本步骤

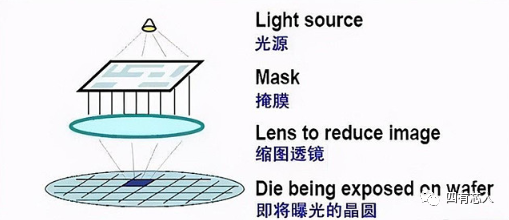

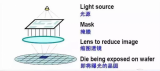

如果直接用激光照射整个晶圆,那么光刻胶的所有部分都会发生质变,所以需要使光源通过特定形状的母版,再照射到晶圆上,这个母版就叫掩模版(Photomask)。光源通过掩模版照射到晶圆上,即可将掩模版的图案转印到晶圆上。

在晶圆上绘制图形后,还要经显影(Develop)处理,即在曝光后,除去曝光区光刻胶化学性质发生变化的部分,从而制作出所需的“饼干模具”。简言之,光刻工艺可以概括为使光源通过掩模版照射到涂敷光刻胶的晶圆表面,以将掩模版图形转印到晶圆上的工艺。

03

光刻胶(Photoresist)

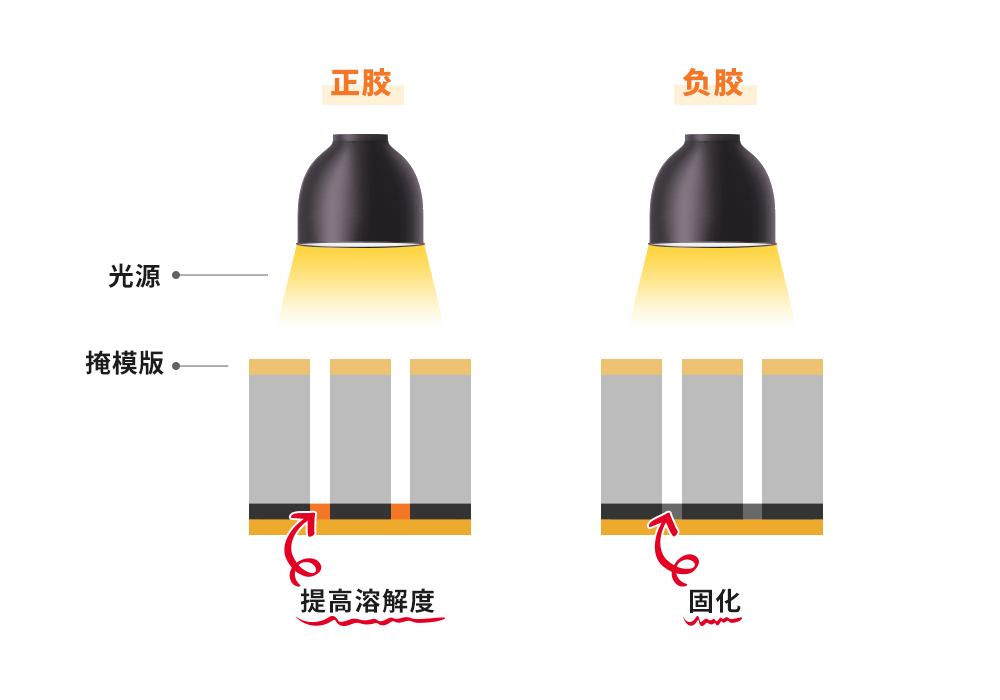

如上所述,光刻胶经曝光后,其化学性质会发生改变。更准确地说,经曝光后,光刻胶在显影液中的溶解度发生了变化:曝光后溶解度上升的物质称作正性光刻胶(正胶),反之则为负性光刻胶(负胶)。为了更好区分,我们可以把最直观可见的物质理解为正胶。正胶经显影处理后,被曝光的区域溶于显影液,在后续的刻蚀、沉积等工艺中,质变的部分会被刻蚀去除掉,而没有被曝光部分不会受后续工艺的影响。

半导体制造商一般会根据工艺的目的选择合适的光刻胶。例如,负胶经曝光而固化的部分,在显影过程中,因吸收部分显影液而容易膨胀、变形,不适合绘制精细图形。因此,绘制精细图形通常采用正胶。但负胶却具有成本低以及在刻蚀(Etching)工艺中抗刻蚀能力更强的的优点。

▲ 图5: 正性光刻胶(正胶)与负性光刻胶(负胶)。

选好光刻胶后,就得用涂布机(Coater)涂抹光刻胶。通过涂布机的高速旋转,滴落到晶圆的光刻胶可均匀伸展到整个晶圆表面。

光刻胶涂好后,应去除沾染在晶圆背面或边缘的多余胶水,再放入烘箱内加热烘烤,使溶剂蒸发,为下一道工艺做准备。

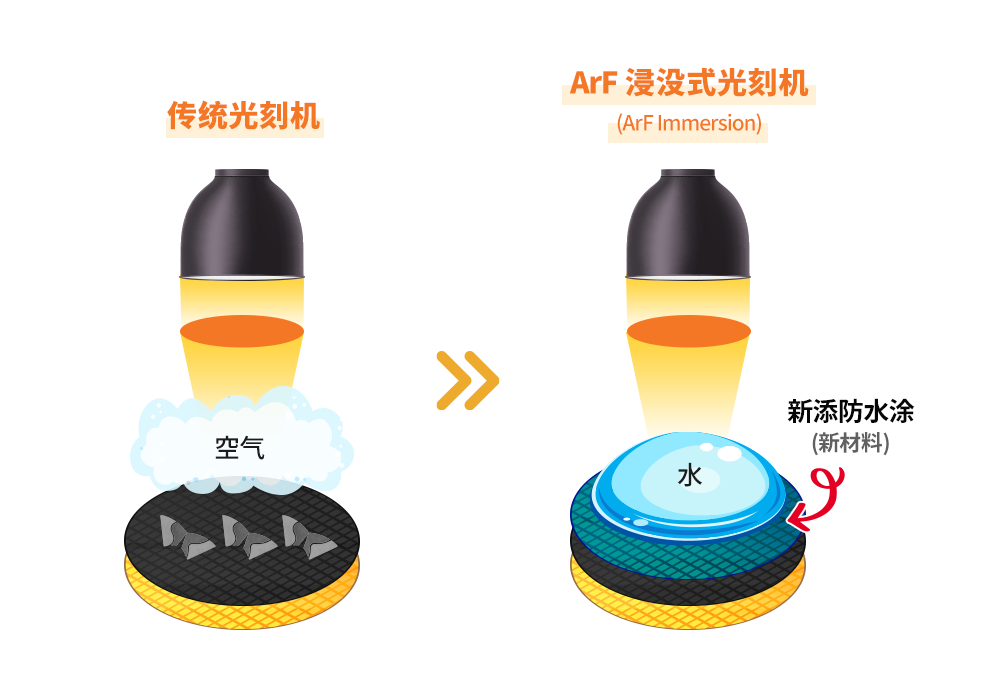

随着时代的发展,光刻胶的结构也变得越来越复杂。我们通常说“涂覆光刻胶”,但其实,大部分的光刻胶并不是一层,而是多层结构。底部抗反射涂层(BARC,Bottom Anti-reflective Coatings)就是其中的一种。随着微细化技术的进一步升级,***照射的光在晶圆表面被反射,进而影响到图形的绘制。为解决这一技术问题,在涂覆光刻胶前,可先将抗反射涂层涂覆在晶圆表面,以减少底部光的反射(因涂覆在光刻胶的底部,故称为Bottom)。此外,随着以水为介质的浸没式光刻设备ArF Immersion1问世,可以抖出水分并且不会损伤的防水涂层(顶部抗反射涂层,Top Anti-Reflective Coat)便应运而生。

在此我们要把重点放在理解如何克服引进新技术后的新挑战。以EUV***2为例,高能量的极紫外线击中光刻胶并发生反应后会污染掩模版。为解决这一技术难题,一方面应深入研究光刻胶材料,另一方面要通过引进掩模版保护膜(Pellicle)解决这一问题。

1ArF浸没式***(ArF immersion):以水取代***内光的介质(空气),从而进一步改善性能

2EUV***:采用极紫外线绘制超精细图形的***

04

掩模版(Photomask)

▲ 图6: ***运作图示

涂覆好光刻胶后,下一步就是在光刻胶上绘制图形。为此,需要一种名为掩模版的透明版。掩模版分为光可通过的透明区和遮光的不透明区。光源通过掩模版把图形投射到光刻胶上,从而将掩模图形转印到晶体上。设计掩模图形时会考虑光的干涉效果,因此,掩模版的图形与我们实际想绘制的图形会有所不同。

掩模版的图形设计其实就是半导体设计,这决定了半导体的用途。比如,用于DRAM、NAND闪存等存储器制造的掩模版会有很多肉眼看不到、非常有规律的重复的图形;而用于CPU、GPU等逻辑半导体(Logic Semiconductor)的掩模版,结构则相当复杂。

此外,半导体制造需要多个掩模版。使用掩模版曝光后,在随后的刻蚀、沉积和氧化工艺中再经多种处理,然后再重复上述过程,堆叠半导体的下一层。可见,所谓“设计”,其实就是为赋予芯片一定功能,不断制作用于绘制半导体各层的掩模版的过程。

掩模版是事先预备好的。因此,下一步就是找准曝光的起始位置,即对准(Alignment)。在之前的文章中我们也说过,在半导体制程工序中,光刻工艺可能需要反复数十次。半导体内细微图形的间隔仅为数十纳米,因此,误差一旦累积数十次,就很可能造成严重不良。因此,需要在曝光之前,寻找在前端工艺已形成的对准标志(Alignment Mark)。

05

曝光(Exposure)

终于到了曝光阶段,这是实际投射光源的阶段。把光(激光)投射到晶圆一个芯片大小的狭窄区域,待曝光一定时间后,***将向旁边稍加移动,重复上述过程。

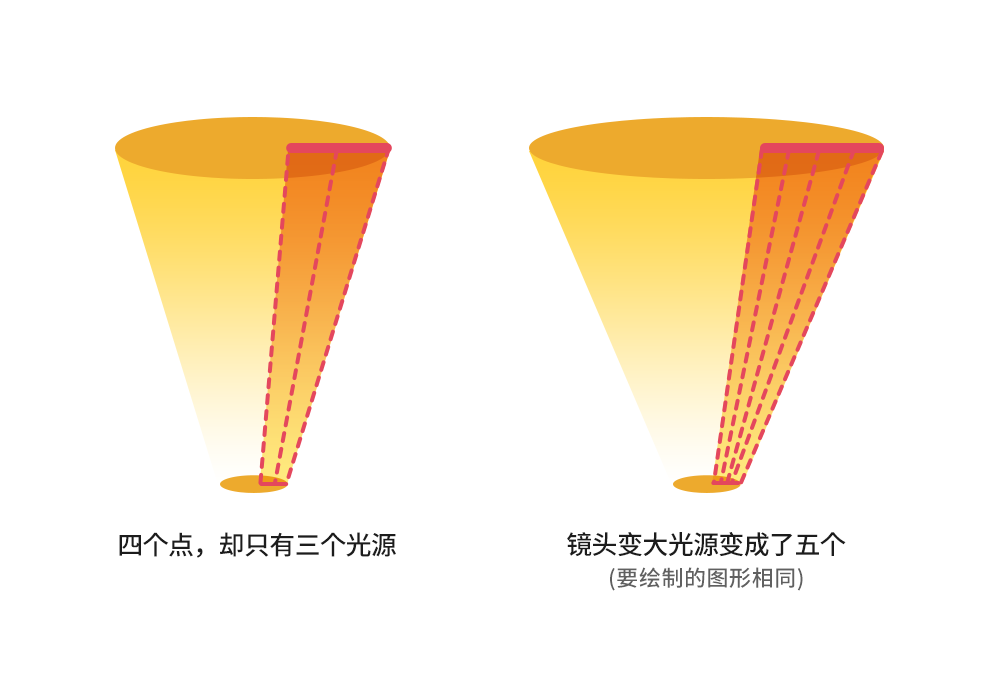

***分辨两物点的能力叫做“物镜的分辨能力(鉴别率)”。物镜分辨能力的公式为d=λ/(2NA) (λ:入射光的波长,NA:表示物镜的数值孔径)。物镜的分辨能力越高,两物点间最小距离d越小,即两物体仿佛重合为一个物体,很难分辨。因此,掩模版绘制再精细的版图也无法转印到实际的晶圆表面上。

可见,降低分辨能力非常重要。上述公式给我们揭示了两种方法:一是通过调节入射光的波长来克服。增加激光的能量可缩短入射光的波长。我们经常在新闻中听到的极紫外线(EUV,Extreme Ultraviolet Lithography)***正是通过将深紫外线(DUV,Deep Ultraviolet Lithography)***的波长缩短至1/14(=提高光能),实现精细图形绘制的;另一方面,还可通过提高物镜的数值孔径(NA)来寻找突破口。提高光源镜头数值孔径,或使用高折射率的介质增加物镜的数值孔径。高数值孔径极紫外线(High NA EUV)***就是采用了提高光源镜头数值孔径的方法,而常用的深紫外线***(ArF immersion)则采用了高折射率介质的方法。

物镜的数值孔径其实很难直观去理解,<图7>揭示了一种相对较通俗的理解方法。相信读者可以从中理解光源镜头变大,分辨率就会提高(变小)的原理。

▲ 图7: 物镜的数值孔径与物镜的分辨能力

寻找***的光源可非同小可。直到21世纪初,科研人员们还在不断发现更好的光源。但从找到193nm的氟化氩(ArF)激光,到发现13.5nm的极紫外线作为光源,科学家们足足花了10多年的时间。这主要缘于光的性质,光的波长越短,越不容易发生折射,且容易被材料吸收。

此外,曝光对半导体的生产量也非常重要。从上述讲解中可以看出,曝光与氧化工艺不同,无法同时处理数十个晶圆,即无法打造可以一次处理直径为300mm的晶圆的均匀光源,***每次只能曝光1~4个芯片。最新版***每台约1000亿韩元以上,相当昂贵,但每小时也只能处理100张左右的晶圆。仅投入到曝光工艺的资金就是氧化工艺的12倍*。对于极紫外线来说,与其说“是否能作为光源”重要,不如说“是否能提高处理量,实现商业价值”更加重要。为解决这一问题,不仅要从光源入手,还要从材料方面入手,寻找对少量光也能敏感反应的光刻胶材料。

曝光结束后,就要检测晶圆的套刻(Overlay)误差。套刻,是为测量***的对准精度而在晶圆上做的小标识。每次曝光时围绕同一个中心,以不同大小的标记套刻标识,就可测量曝光的对准程度或晶圆是否有所偏离等。但套刻工艺与对准(Alignment)工艺不同,不会检测每一个晶圆的套刻精度。

06

显影(Develop)

光刻胶曝光后,曝光区光刻胶的化学性质会发生改变。这些变质的光刻胶要用显影液溶解后去除,这一工艺被称作显影(Develop)。

当然,在进入显影工艺前,要把晶圆放入烘箱烘烤,这样可以进一步促进曝光区光刻胶的性质变化,这一过程被称作曝光后烘烤(PEB,Post Exposure Bake)。

经PEB后,在晶片涂覆显影液,去除变质的光刻胶部分,必要时还可进行清洗(Rinse)。清洗时,要根据光刻胶的材料选择合适的清洗溶液。而清洗设备也是种类繁多,且往往要在处理速度和良率之间做权衡。

经上述一系列过程,半导体的“饼干模具”终于制成了。最后,在这“模具”的缝隙涂覆所需的材料,或削减不需要的部分等,经一番完善工作后在表面雕刻晶体管和金属布线即可。

07

***的发展与纵向思考

从上述对光刻工艺的讲解中,相信读者已经明白以死记硬背的方式去学习一门技术有多么地徒劳。在193nm的氟化氩(ArF)激光光源遇到瓶颈时,科学家们还没有发现EUV,但微细化的脚步又不能停止。所以,研究人员们就试图缩短相同光源的波长,进而研发出了氟化氩浸没式***,从而使半导体行业向100nm以下级别迈出了一步。当然,这不是仅通过光刻工艺就可以解决的,还需要前后端工艺的共同努力。

▲图8: 为研发ArF浸没式***所引进的新技术

使用浸没式光刻设备,就要在晶圆上滴落高折射率的液体(水)。问题是半导体工艺非常精细,小小的误差也会“酿成大错”,比如,液体的不纯物有可能导致半导体产品的瑕疵,或光刻胶被水溶解后被清洗掉等。为攻克这些技术难关,人们进一步研发了可以制成高纯度水的技术以及在光刻胶上形成易去除的防水涂层的技术。在光刻胶上新涂覆了一层防水层后,显影工艺当然也要相应做出改变。

这些改变,需要由半导体行业持续努力解决。最近,SK海力士与材料公司联手,共同研发了干法光刻工艺流程*。

我们在前一篇(氧化工艺)中也曾说到,干法工艺,顾名思义就是没有水的介入。也就是说,这是一种与之前完全不同的崭新工艺技术。它像沉积工艺那样在光刻胶表面上形成薄膜,在显影过程中也不清洗。需研发这些技术的理由不胜枚举,但最重要的,就是微细化水平已经达到了极致,***绘制出的精细图形,在涂覆和清洗光刻胶的过程中会被破坏。

08

结语 :成功绘制不等于结束

在本篇文章中,我们快速浏览了光刻工艺,通过该工艺,图形的绘制已经完成。下一步就需要在绘制的图形上添加点什么或削减不需要的部分。虽说光刻工艺很重要,但也不能忽视其他工艺。因为制作微细模具(光刻工艺)和利用这个模具完成所需的操作可是完全不同的问题。

EUV***

-

MOSFET

+关注

关注

151文章

10802浏览量

234894 -

半导体

+关注

关注

339文章

31222浏览量

266441 -

场效应晶体管

+关注

关注

6文章

425浏览量

20706 -

光刻机

+关注

关注

31文章

1201浏览量

49010 -

EUV光刻机

+关注

关注

2文章

129浏览量

15870

原文标题:半导体前端工艺|第三篇:光刻——半导体电路的绘制

文章出处:【微信号:SKhynixchina,微信公众号:SK海力士】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

浅谈半导体制造中的光刻工艺

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

光刻机工艺的原理及设备

《炬丰科技-半导体工艺》光刻前 GaAs 表面处理以改善湿化学蚀刻过程中的光刻胶附着力和改善湿蚀刻轮廓

半导体光刻技术基本原理

半导体光刻工艺培训资料

半导体光刻是什么

什么是光刻工艺?光刻的基本原理

光刻工艺的基本知识

半导体光刻工艺 光刻—半导体电路的绘制

半导体光刻工艺 光刻—半导体电路的绘制

![[<b class='flag-5'>半导体</b>前端<b class='flag-5'>工艺</b>:第三篇] <b class='flag-5'>光刻</b>——<b class='flag-5'>半导体</b><b class='flag-5'>电路</b>的<b class='flag-5'>绘制</b>](https://file1.elecfans.com/web2/M00/B1/DB/wKgZomVdgPSAWsXlAAH9_6nQJHk959.png)

评论