本文转自公众号,欢迎关注基于DWC2的USB驱动开发-发送相关的寄存器DMA寄存器详解 (qq.com)

前言

上一篇我们介绍了IN端点,发送,DMA相关的两个寄存器,这一篇继续讲另外的几个寄存器。

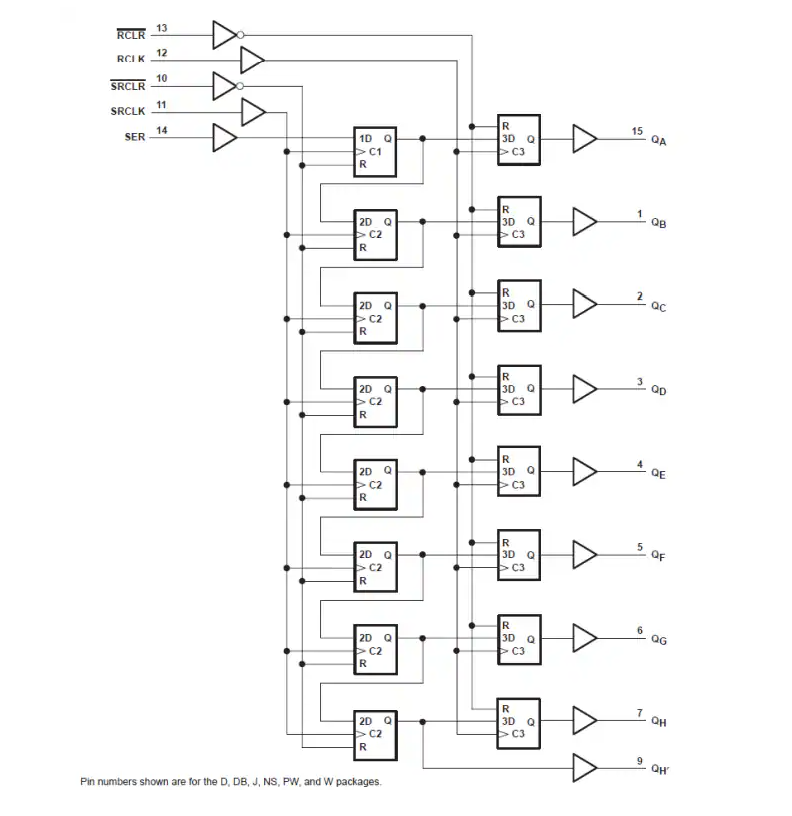

DIEPCTLi

偏移地址 0x900+i*20

该寄存器控制端点的属性,使能等,是端点操作的核心寄存器

传输使能与禁能

Bit31和bit30

其实这里名字Enable和Disable取的并不合适,这里实际并不是指的端点的使能和禁能,更确切的说应该是启动和停止DMA对描述符连链表,DMA缓冲数据的处理,启动和停止端点数据的传输。

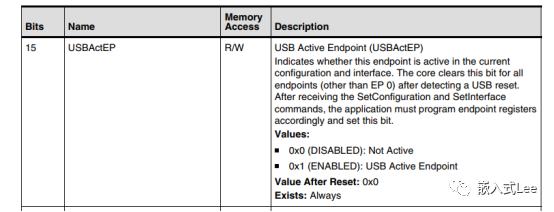

端点的使能也就是激活应该是bit15。

软件在准备好描述符( Scatter/Gather DMA )即DIEPDMAi以及描述符链表后,置位该位,硬件就会开始处理该描述符。对于非Scatter/Gather DMA 的DMA则是准备好DMA对应的缓冲区也是配置DIEPDMAi后使能该位硬件开始DMA处理。当然这里DMA处理描述符和DMA缓冲区实际就是搬运数据到TxFIFO中去,所以要TxFIFO有空闲才会进行。

注意硬件在发送完数据后产生相应的中断时会自动清除该位即SETUP的完成,数据发送完成时,即相当于自动流控,发送完后硬件自动Disable,软件重新配置相应的描述符和DMA再重新Enable。否则不Disable此时软件还没准备好描述符和DMA就会没有数据可发。

另外手动置位EPDis时 EPEna也会清零,两者互斥。

而EPDis表示停止传输,软件只能在EPEna之前置位过才能置位该位,在停止中断中硬件自动清除该位。

注意置位后不是一定数据传输马上就停止了,要到停止中断才能确认是停止了。

即DIEPINTi寄存器的bit1 EPDisbld为1.

端点激活

硬件收到复位信号后清除该位(EP0的不置位,因为EP0要默认使能,用于控制传输进行枚举),软件在设置配置,设置接口的标准请求时置位该位。

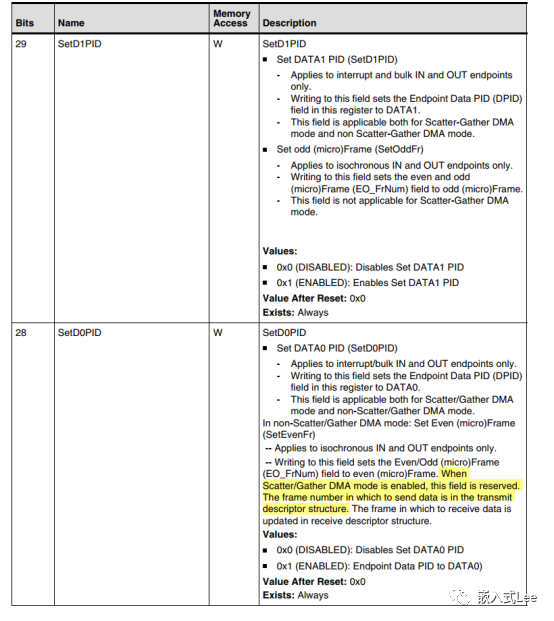

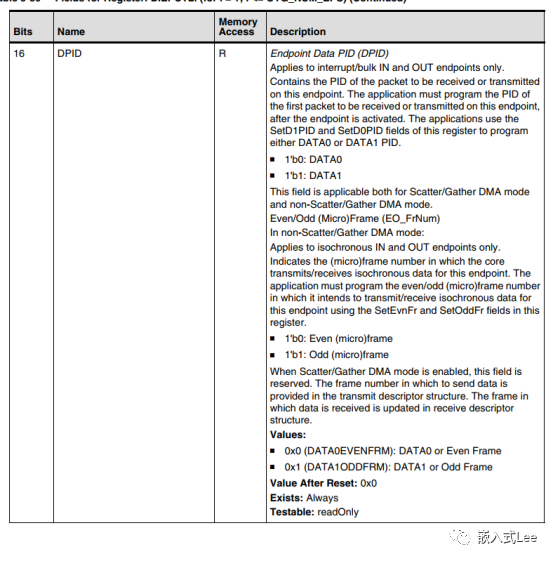

PID设置

设置PID,注意Scatter-Gather DMA模式是在描述符中设置PID的,所以这里保留

Bit16可以查看当前的PID状态

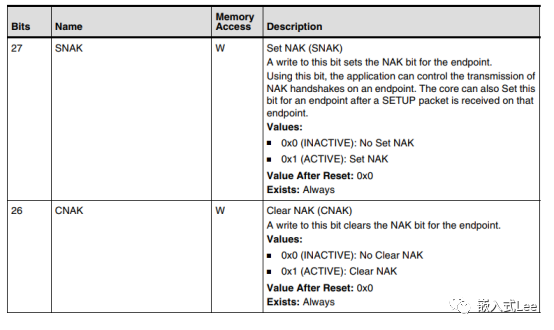

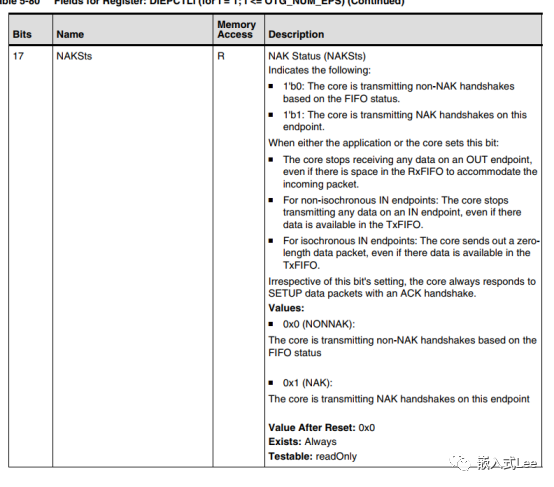

NACK操作

软件设置SNAK该位以发送NACK用于流控

注意硬件在SETUP完成后也会置位改位,所以软件在开启新的传输时需要置位CNAK和EPEna以停止NACK和启动传输。

DIEPINTi的bit6 INEPNakEff置位表示SNAK设置NACK生效。

Bit17 NAKSts表示当前是否出于NAK状态

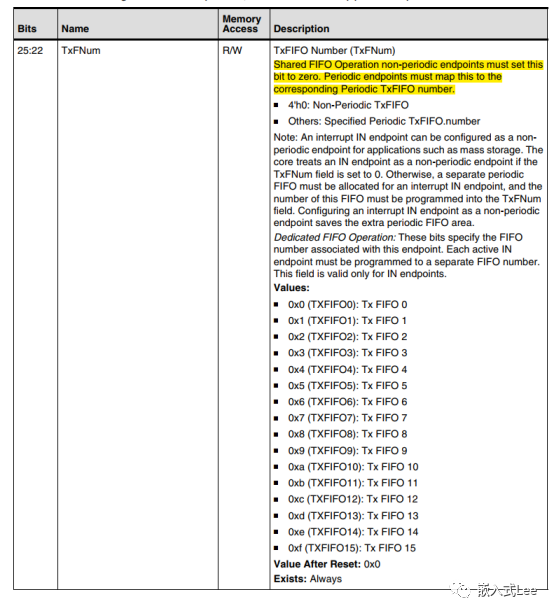

发送FIFO号

Shared FIFO模式非周期端点共用一个发送FIFO所以这里必须为0,

只有独立发送FIFO模式,或者周期端点,则每个发送IN端点可以对应一个独立的TxFIFO

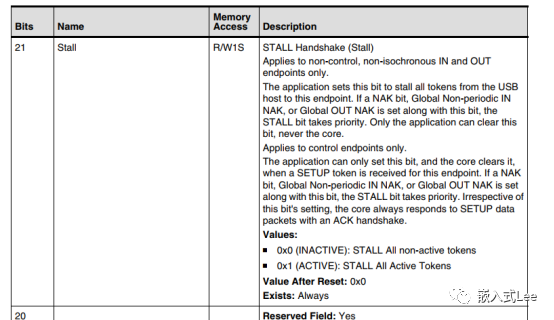

STALL

软件置位该为以产生STALL的ACK

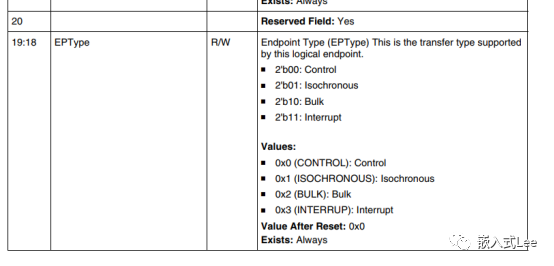

端点类型

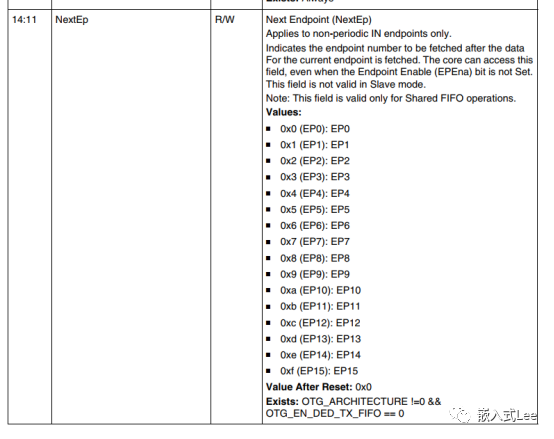

下一个端点

Shared FIFO模式才有,必须要DMA模式才有(Slave

模式不需要)

对于每个发送端点独立FIFO模式也不需要,因为都是独立控制的,

只有Shared FIFO模式共享FIFO所以才需要链表告诉DMA下一个处理哪个端点

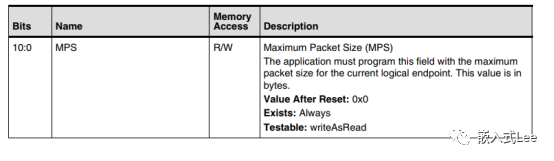

端点最大包大小

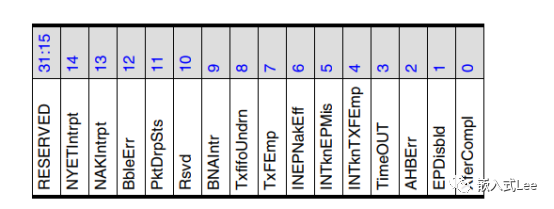

DIEPINTi****中断状态

这里是某个端点详细的中断原因,其中中断的使能是总的中断使能控制DAINTMSK,即控制哪一个端点的中断使能,

其中bit0 XferCompl表示发送完,是最重要的中断状态

DIEPTSIZi

发送大小寄存器

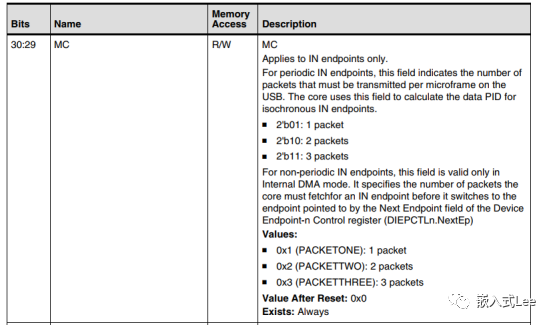

一个微帧发送包数MC

注意Scatter-Gather DMA在描述中配置,不使用该寄存器的MC

该位只有内部DMA的非Scatter-Gather DMA模式使用

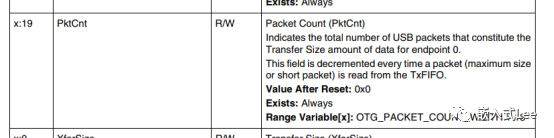

包数

注意每搬运完一个包到TxFIFO,该值会递减,所以可以看该寄存器看已经搬运完的包数

同样注意Scatter-Gather DMA在描述中配置,也不使用该寄存器

传输大小

指定一次DMA传输的大小

同样注意Scatter-Gather DMA在描述中配置,也不使用该寄存器

该值也会根据已经处理完的数据量递减

其中x 由GHWCFG3的bit4:0可以看到

DTXFSTSi

该寄存器可以看指定端点对应的TxFIFO剩余空闲的空间大小

实例

Scatter/Gather DMA模式

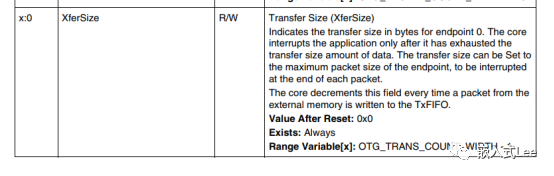

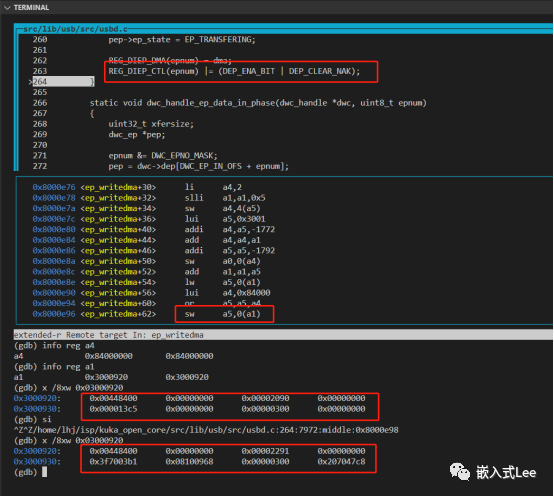

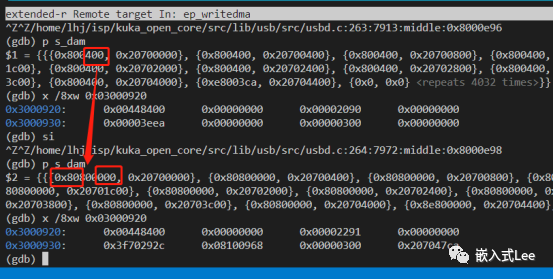

核心代码如下即配置DMA地址,使能EPEna,清除NACK。这里没有贴出描述符的填充过程。

void ep_writedma(uint32_t dma, uint8_t epnum)

{

REG_DIEP_DMA(epnum) = dma;

REG_DIEP_CTL(epnum) |= (DEP_ENA_BIT | DEP_CLEAR_NAK);

}

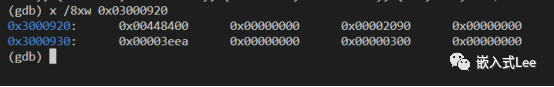

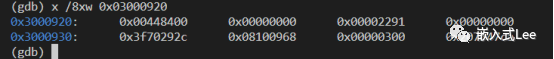

如下是EPena置位前后寄存器值,该位软件置位后传输完后硬件自动清零

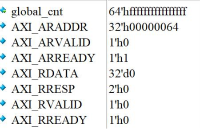

DIEPINT1 的bit0 XferCompl置位说明DMA处理完了

Bit9 BNAIntr置位说明DMA处理完后面没有描述符需要处理了。

DIEPDMA1,DIEPDMAB1变为了0x08100968和0x207047c8这个上一篇文章已经分析过了

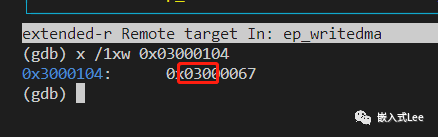

DTXFSTS1为0x00000300

DIEPTXFi 0x104+(i-1)*4

看到TxFIFO1的大小是0x300,也就是都发送完了TxFIFO中又都空闲了

DIEPTSIZ1由0x13C5变为了0x3F7003b1.

EPEna之后

可以看到描述的状态也变为了DMA Done,长度也变为了0表示发送完了。

总结

以上是IN端点发送数据,DMA和端点相关需要配置的寄存器,需要注意的是Scatter/Gather DMA模式 一些状态,比如发送包数,长度放在了描述符中去了。

熟悉以上寄存器对编写驱动控制IN端点发送数据至关重要,一些寄存器也可以给调试提供信息。

-

寄存器

+关注

关注

31文章

5620浏览量

130444 -

usb

+关注

关注

60文章

8480浏览量

285967 -

dma

+关注

关注

3文章

582浏览量

106284 -

驱动开发

+关注

关注

0文章

142浏览量

12727 -

DWC2

+关注

关注

0文章

35浏览量

403

发布评论请先 登录

ICSSSTUB32866B:DDR2可配置寄存器缓冲器的技术解析

Renesas ICSSSTUAF32869A:DDR2的14位可配置寄存器缓冲器

Renesas ICSSSTUAF32865A:DDR2 28位可配置寄存器缓冲器详解

深入解析IDT74SSTUBH32865A:DDR2的28位1:2寄存器缓冲器

IDT74SSTV16857:14位带SSTL I/O的寄存器缓冲器详解

IDT74SSTU32864/A/C/D/G:1.8V SSTL I/O的1:1和1:2寄存器缓冲器详解

PI74SSTVF16857 14位寄存器缓冲器:特性与应用详解

SN74SSTVF16857 14位寄存器缓冲器:设计与应用详解

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器

Renesas IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器详解

NVMe高速传输之摆脱XDMA设计32:寄存器功能验证与分析2

TPIC6B595 8位功率移位寄存器技术文档总结

SN74LV594A:2-5.5V带输出寄存器的8位移位寄存器技术解析

基于DWC2的USB驱动开发-IN端点发送相关的寄存器详解

基于DWC2的USB驱动开发-IN端点发送相关的寄存器详解

评论