在Allegro软件16.6版本及以上版本,增加了显示网络名称的功能,方便进行布线设计。本文向大家讲解,如何将网络命令进行显示,具体的操作步骤如下所示:

01第一步

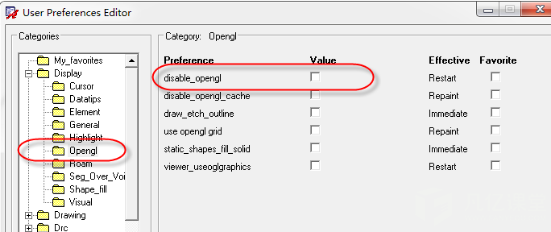

首先将Opengl模式开启,进入用户参数设置界面,在Display显示界面选择Opengl,右侧的第一项复选框不要勾选,如图1所示;

图1 开启Opengl模式示意图

02第二步

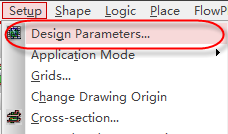

开启Opengl模式之后,重新启动PCB软件,打开设计参数选项,点击Setup-Design Parameters,如图2所示;

图2 打开设计参数设置示意图

03第三步

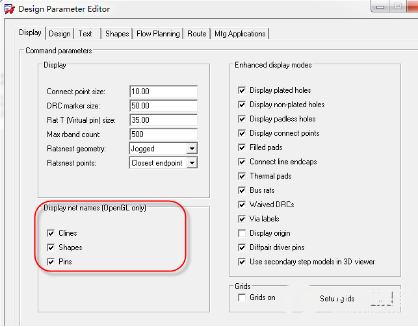

进入设置界面以后,选择Display选项,在Display net name的选项中,将下面三项的复选框进行勾选,目前只支持在走线、铜皮、焊盘上显示网络,如图3所示;

图3 显示网络命令参数设置示意图

04第四步

设置完参数之后,回到PCB界面,这样网络名称就会在走线、铜皮、焊盘上进行显示了。

上述,就是在Allegro软件中,在走线、铜皮、焊盘上显示网络名称的方法解析。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

allegro

+关注

关注

42文章

772浏览量

150488

发布评论请先 登录

相关推荐

热点推荐

12:如何把 PCB 上的铜皮扩大或缩小 I 芯巧Allegro PCB 设计小诀窍

背景介绍:我们在进行PCB设计时,经常需要等比例的将PCB上的铜皮扩大或者缩小,例如对按板框形状添加的Route keepin或者Package keepin区域进行内缩,而Allegro PCB设计工具提供的Z-Copy功能和Expand/Contract功能可以便捷的

发表于 04-16 17:08

09. 如何把PCB上的图形快速切换到不同的层? | 芯巧Allegro PCB 设计小诀窍

背景介绍: 我们在进行PCB设计时,通常会需要将绘制好的铜皮、走线或者其他图形转换到另外一层,Allegro PCB设计工具的Change或者Cross Copy等功能,可以快速实现这

发表于 04-10 10:58

07. 如何在Allegro中设置可以走线但不能铺的铜区域?| 芯巧Allegro PCB 设计小诀窍

背景介绍:我们在进行PCB设计时,经常需要绘制一些禁止铺铜但是允许走线的区域,如果我们直接使用Route Keepout绘制的话,虽然可以实现在此区域内禁止铺铜的效果,但是走线在此区域

发表于 04-09 17:23

05. 如何在 Allegro 中沿着板子轮廓走线?| 芯巧Allegro PCB 设计小诀窍

的走线模式,很难实现这样的走线需求,而Allegro PCB设计工具提供的Contour Mode(轮廓

发表于 04-03 16:46

03. 如何把 PCB 板上的线变成铜皮?| 芯巧Allegro PCB 设计小诀窍

线需要进行开窗刷锡膏时,也可以通过将走线转换成SolderMask层的铜皮来实现。 下面我们就开始分享具体的使用方法及步骤:一、线构成的非矢

发表于 04-03 16:40

01. 如何在 Allegro 中快速区别不同网络?| 芯巧Allegro PCB 设计小诀窍

Allegro PCB设计小诀窍系列--如何在Allegro中快速区别不同网络背景介绍:Allegro PCB设计工具可以通过高亮操作将选中

发表于 04-03 15:51

技术资讯 I Allegro 设计中的走线约束设计

本文要点在进行时序等长布线操作的时候,在布线操作的时候不管你是走蛇形线还是走折线,约束管理器会自动帮你计算长度、标偏差,通过精确控制走线长度,来实现信号的时序匹配。约束设计就是一套精准

Allegro Skill布线功能之删除Dangling介绍

高速pcb布线完成之后,需要检查pcb板上是否存在多余的走线、过孔以及孤岛铜皮等情况,那么多余的走线以及过孔被称为Dangling line

Allegro Skill布线功能之RF相邻铜皮挖空介绍

在高速PCB设计中,对于射频信号的走线,其相邻层挖空的设计具有重要作用。射频信号通常需要严格控制阻抗(如50Ω),当射频走线线宽增加以降低插入损耗时,参考层距离的增加是必要的。通过挖空

PCB单层板LAYOUT,QFN封装的中间接地焊盘走线出不来怎么办?

PAD为悬空状态,不能和外部接地网络连接。现有的封装不能满足布局需求,就只能修改封装设计。下面介绍几种修改方案提供参考。1、芯片的4个边角的管脚进行切角,这样中间接地焊盘就可以从4个边角位置走

发表于 04-27 15:08

Allegro小技巧 | 如何在走线、铜皮、焊盘上显示网络名称

Allegro小技巧 | 如何在走线、铜皮、焊盘上显示网络名称

评论