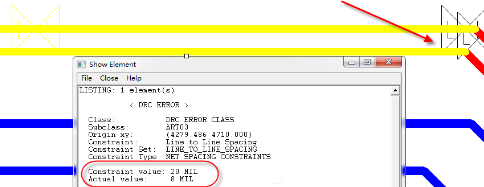

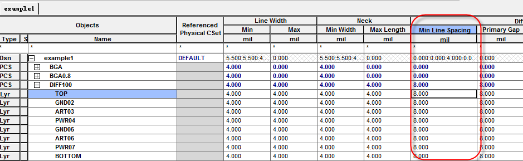

在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如1所示:

图1 差分信号对内报错示意图

如图2所示,差分信号到其它信号的间距是20mil,但是差分按照阻抗线宽走线,间距是8mil,所以出现DRC的错误。

本文向大家介绍如何将所有的差分线的设置到其它信号的间距是20mil并满足自身的阻抗间距不报错,具体操作步骤如下:

01规则设置

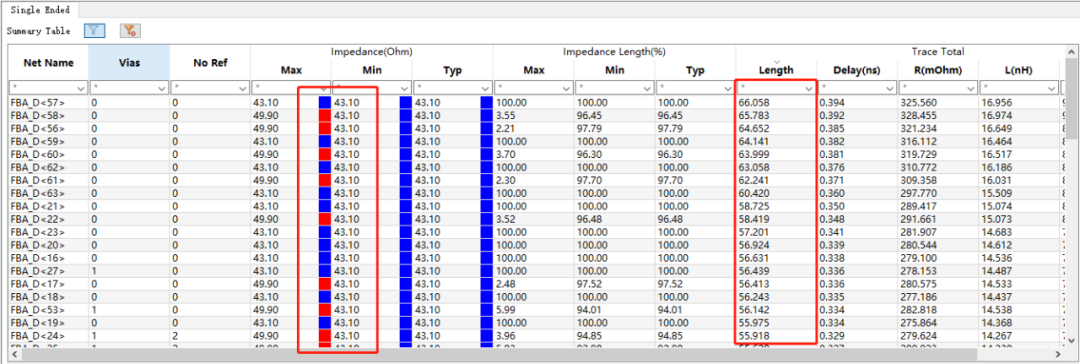

打开规则管理器,执行菜单命令Setup-Constrains,在下拉菜单中选择Constraint Manager,进行规则设置,左侧选择Physical Constraint Set,如图2所示,点击all layers;

图2 进入物理规则设置示意图

02设置差分默认间距

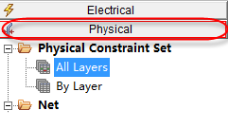

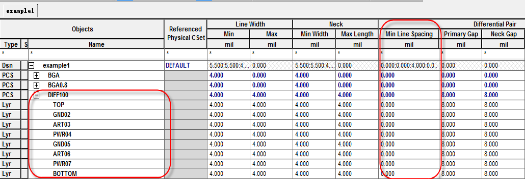

差分走线设置的规则,是DIFF100的规则,在差分属性的Min Line Spacing最小间距,目前是0,如图3所示,我们将其设置为差分默认的间距8mil,如图4所示;

图3默认差分间距设置示意图

图4 差分最小间距设置示意图

03PCB界面

设置完成以后,回到PCB界面,如图5所示,差分线已经不会报错了,对内满足阻抗要求,对外到其它信号满足20mil间距。

图5差分信号不报错示意图

-

PCB设计

+关注

关注

396文章

4907浏览量

94052

发布评论请先 登录

Allegro更新原理图导入网表后,Xnet混乱何解?

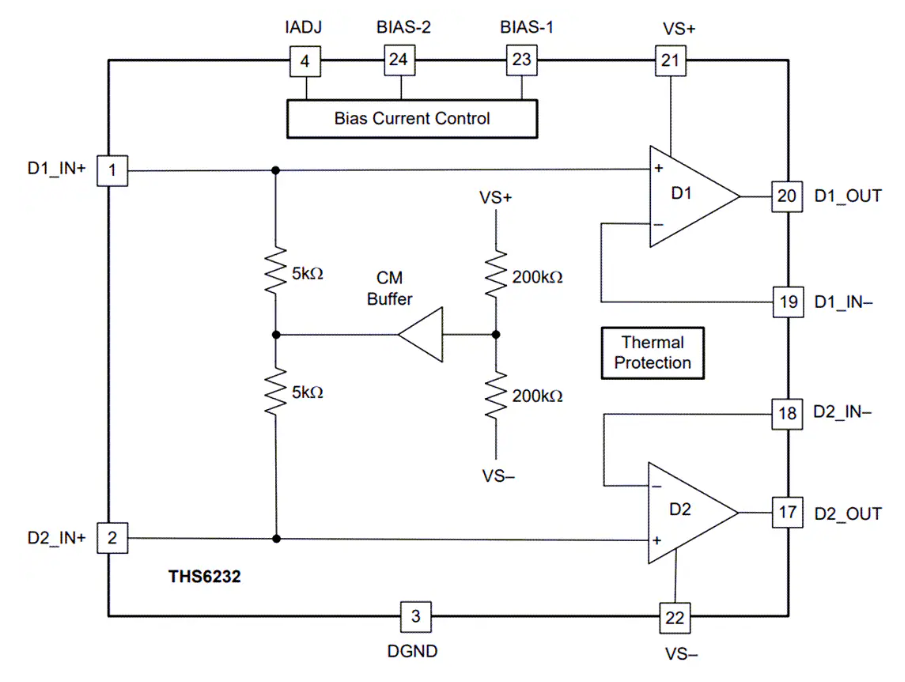

Texas Instruments THS6232差分线路驱动器数据手册

凡亿Allegro Skill工艺辅助之Gerber设置导出

CCG2 type-c to DP 在layout时的注意事项是什么,差分线阻抗多少欧?

Allegro Skill布线功能-添加差分过孔禁布区

DAC5675A差分输入端差分线长、线距是否有特殊要求?

ADS5474在PCB布线时,数据输出和时钟输出共16对差分线需不需要保持等长,如果要的话误差可以控制在多少个mil?

DA3482的LVPECL输入接口电路配置图,这里差分线分别连150欧的电阻接地有什么作用?

浅谈瑞盟科技·MS2574/2574T/2574SS——高速、四通道差分线路驱动器

Allegro小技巧 | 如何设置差分线能够有效减少报错

Allegro小技巧 | 如何设置差分线能够有效减少报错

评论