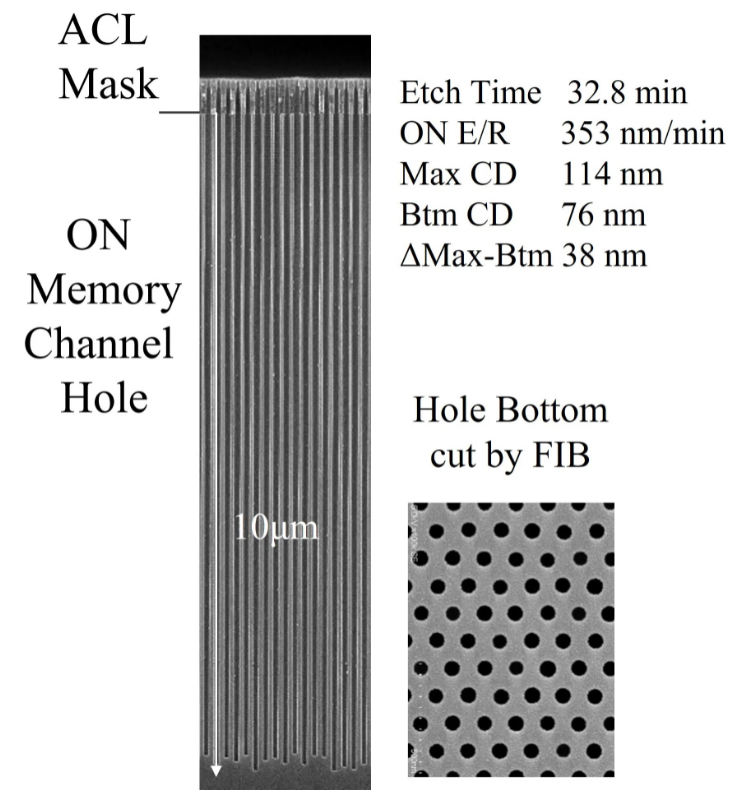

东京电子9日宣布,成功开发出了可以用于制造400段以上堆砌而成的3d nand闪存的“存储器洞蚀刻技术”。研究组开发的新技术首次使电蚀在低温下也能应用,发明了具有很高蚀觉速度的系统。

这一创新技术可在短短33分钟内完成10微米深度的刻蚀,比以往的技术大大缩短了时间。东京电子方面表示:“如果应用该技术,不仅有助于制造高容量3d nand,还可以减少84%的地球变暖危险。”

东京电子表示,开发该技术的小组将于6月11日至16日在日本京都举行的“2023年招待所集成电路技术及工程研讨会”上发表最新成果和报告书。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

3D

+关注

关注

9文章

2993浏览量

113870 -

刻蚀

+关注

关注

2文章

217浏览量

13686

发布评论请先 登录

相关推荐

热点推荐

SK海力士321层4D NAND的诞生

)领域也不断推进技术革新,强化竞争力。NAND产品的数据存储量取决于单元1(cell)堆叠的高度,而提升堆叠层数正是竞争力的关键所在。

什么是Flash闪存以及STM32使用NAND Flash

电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。

分类

NOR和NAND是市场上两种主要的非易失闪存技术。

在1

发表于 07-03 14:33

SK海力士UFS 4.1来了,基于321层1Tb TLC 4D NAND闪存

电子发烧友网综合报道,SK海力士宣布公司成功开发出搭载全球最高321层1Tb(太比特,Terabit)TLC(Triple Level Cell)4

闪存冲击400层+,混合键合技术传来消息

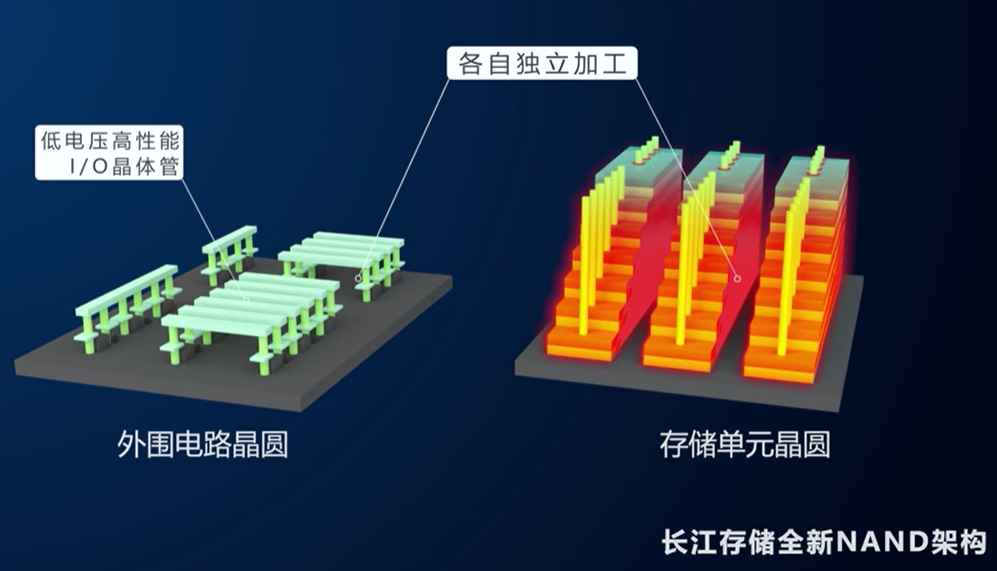

电子发烧友网综合报道,据韩媒报道,三星近日与长江存储签署了3D NAND混合键合专利许可协议,从第10代V-NAND开始,将使用长江存储的专利技术

发表于 02-27 01:56

•948次阅读

铠侠与闪迪发布下一代3D闪存技术,实现4.8Gb/s NAND接口速度

两家公司预展第十代3D闪存技术,为性能、能效和位密度设立新标准旧金山,国际固态电路会议(ISSCC)——铠侠株式会社与闪迪公司联合发布一项尖端3D闪

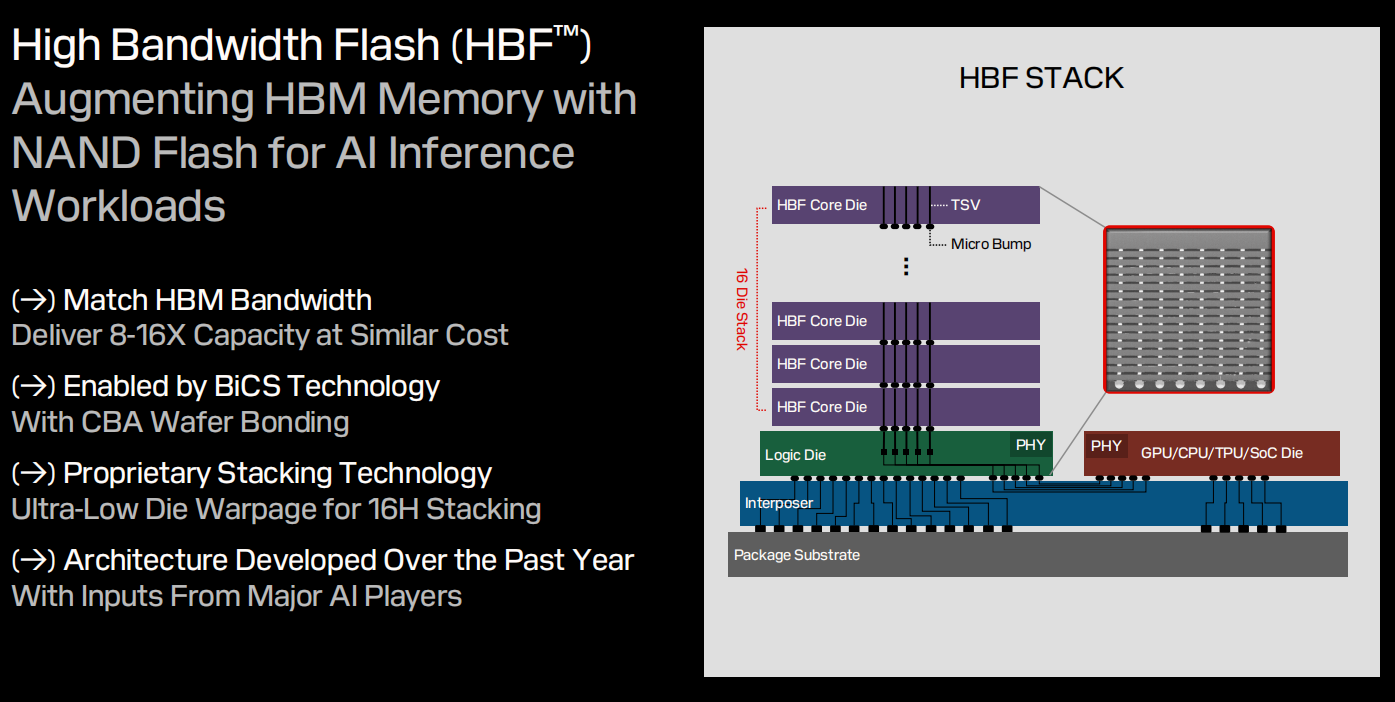

不再是HBM,AI推理流行,HBF存储的机会来了?

NAND闪存和高带宽存储器(HBM)的特性,能更好地满足AI推理的需求。 HBF的堆叠设计类似于HBM,通过硅通孔(TSVs)将多个高性能闪存核心芯片

芯片3D堆叠封装:开启高性能封装新时代!

在半导体行业的快速发展历程中,芯片封装技术始终扮演着至关重要的角色。随着集成电路设计复杂度的不断提升和终端应用对性能、功耗、尺寸等多方面要求的日益严苛,传统的2D封装技术已经难以满足市场的需求。在此背景下,芯片

2.5D和3D封装技术介绍

。 2.5D封装将die拉近,并通过硅中介连接。3D封装实际上采用2.5D封装,进一步垂直堆叠die,使die之间的连接更短。通过这种方式直接集成IC,IC间通信接口通常可以减少或完全

3D打印技术,推动手板打样从概念到成品的高效转化

代表性的新科技之一。这种新兴技术能够大大缩短从概念到成品的时间周期,还能显著提高手板打样的机动性和生产成本,使得产品开发过程变得愈发高效便捷。

近数年,3D打印技术在全球的应用范围不断

发表于 12-26 14:43

东京电子成功开发400层堆叠3D NAND闪存技术

东京电子成功开发400层堆叠3D NAND闪存技术

评论