动手能力哪家强?

在推特上看到一个19岁的博主,耗时整整3年,纯手工自制1200个晶体管的CPU。

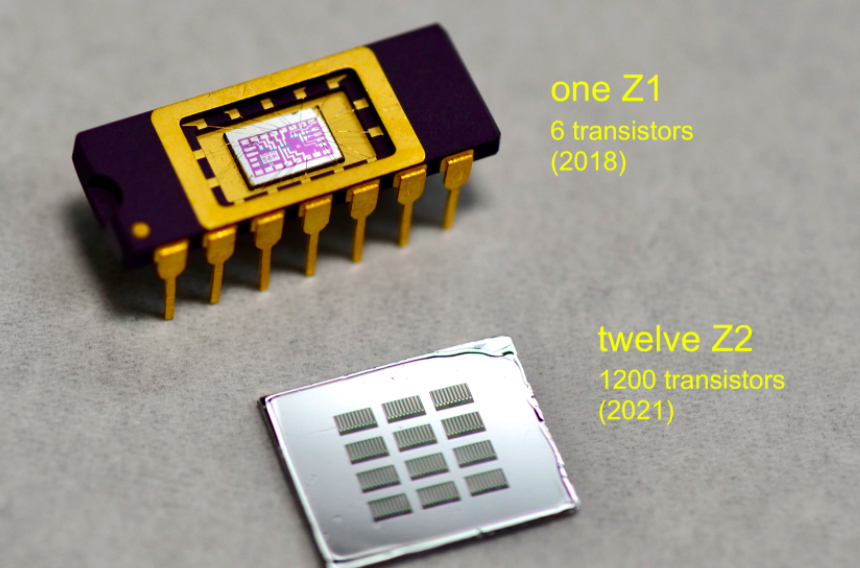

这位叫做 Sam Zeloof 的美国大学生,最终打造出1200个晶体管的CPU! 在10微米的多晶硅栅极工艺上实现,命名为Z2。 重点是,与英特尔上世纪70年代闻名于世的处理器4004使用了相同技术。

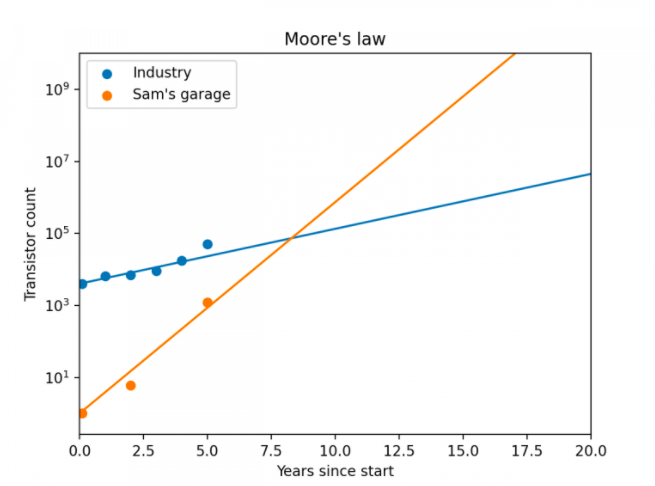

PS排阵列,车库自制,超越「摩尔定律」 这款Z2芯片由第一代升级而来。 18年,17岁的他曾制作了首个集成电路Z1,有6个晶体管。

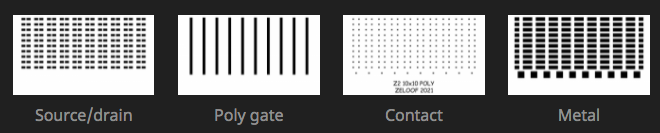

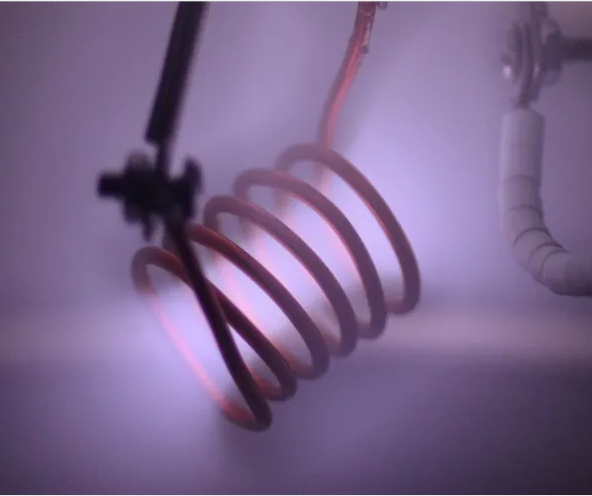

和以前一样,整个过程在他的「车库工厂」进行,使用不纯的化学品,自制的设备,没有无尘室。 首先,Zeloof 在 Photoshop 中布局了一个简单的 10x10 晶体管阵列。

一列中的10个晶体管共享一个共同的栅极连接,每行串联在一起,与相邻的晶体管共享一个源极/漏极。

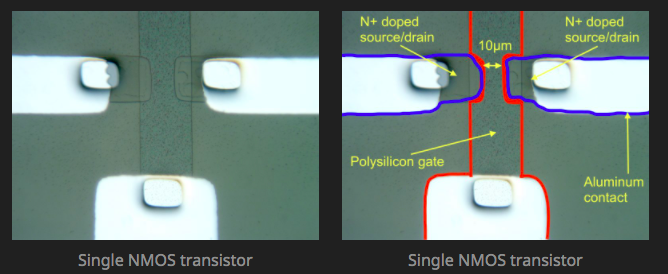

单个10微米 NMOS 晶体管样子如下,金属层有些不对齐,红色的轮廓是多晶硅,蓝色是源极/漏极。

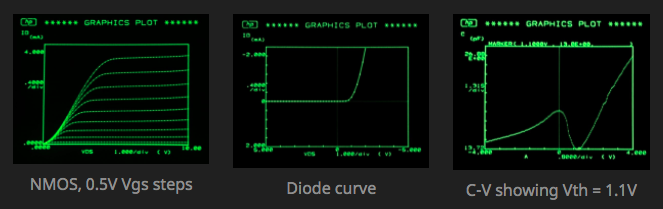

之前,Zeloof 一直采用金属栅极工艺制作。 铝栅极是与其下面的硅沟道具有很大的功函数差异,从而导致高阈值电压(>10V)。 比如,吉他失真踏板和环形振荡器 LED 闪光器,由于这两种材料阈值电压值高,都需要一个或两个 9V 电池来运行电路。

为了节省功耗,Zeloof 选用多晶硅栅极工艺,性能得到提升,自对准栅极就不会产生高阈值电压。 这使得这些芯片与2.5V 和3.3V 逻辑电平兼容。

图纸设计好后,接着切割晶片,对多晶硅栅极进行蚀刻。

Zeloof改进了工艺流程,采用自对准方法,选择高温扩散而不是离子注入进行掺杂。

因为硅片上已经有了各种材料,所以他只需要找到一层薄薄的 SiO2 (大约10nm) ,然后是厚一点的多晶硅 (300nm)。 结果显示,Z2 比 Z1 有了飞跃性的进步。 改用多晶硅栅极工艺大大降低了功耗,但由于没有纯净的化学品和没有洁净室,产量很低。

Zeloof 表示,「我已经做了15个芯片(1500个晶体管),并知道至少有一个完全功能的芯片和至少两个大部分功能,这意味着良率低于 80%,而不是100%。」 视频开篇,Zeloof 调侃自己车库造芯超越摩尔定律。

网友还顺便嘲笑了「挤牙膏」厂英特尔,到了2025年

Zeloof :我终于做到了5nm。 英特尔:这是我们最新的10nm+++++++ 工艺。 极客少年,造芯梦 那么,2018年,Sam Zeloof 究竟做了什么? 尽管CPU芯片制造门槛越来越高,但天才少年Zeloof并没有放弃梦想。 2018年,17岁的他还只是一名高三学生,但他已经成功制作了首个集成电路Z1,拥有6个晶体管,使用5微米的PMOS工艺。

在接受The Amp Hour采访时,Zeloof提到此次发明的灵感源自于YouTube频道,Jeri Ellsworth在个人频道中演示了如何不用特殊工具来切割硅片、自制硅晶体管的方法。

受此启发,Zeloof计划在Jeri Ellsworth的基础上来制作集成电路。

这样一位传奇的少年,可以说是一位资深的电子爱好者。 他在高中时就开始自己制作芯片,并在家里学习了制造芯片所需的信息和机器。 他从eBay上买来零部件和材料,打造成一个半导体制造实验室。 这位才华横溢的少年认为,尝试制造芯片是一种了解半导体和晶体管内部运作情况的方法。

从2017年起,他开始在博客介绍自己的项目,Zeloof收到了很多积极的反馈。 一些上世纪70年代的资深工程师也为Zeloof提供了很多建议,希望他能开发出一种相对简单的方法,克隆4004芯片技术,从而更好的为自己开发芯片服务。

Zeloof表示,「我开始阅读旧书,研究一些旧的专利,因为新书介绍的制作流程需要非常昂贵的设备。」

-

芯片

+关注

关注

463文章

54411浏览量

469151 -

cpu

+关注

关注

68文章

11326浏览量

225863 -

晶体管

+关注

关注

78文章

10439浏览量

148576

原文标题:纯手工打造!19岁天才少年自制1200个晶体管的CPU

文章出处:【微信号:单片机与嵌入式,微信公众号:单片机与嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

电压选择晶体管应用电路第二期

晶体管的定义,晶体管测量参数和参数测量仪器

英飞凌功率晶体管的短路耐受性测试

0.45-6.0 GHz 低噪声晶体管 skyworksinc

多值电场型电压选择晶体管结构

晶体管架构的演变过程

下一代高速芯片晶体管解制造问题解决了!

华为发布天才少年挑战课题发布 五大主题方向课题放榜

无结场效应晶体管详解

19岁天才少年自制1200个晶体管的CPU

19岁天才少年自制1200个晶体管的CPU

评论