IC封装的热特性对于IC应用的性能和可靠性来说是非常关键的。本文描述了标准封装的热特性:热阻(用“theta”或Θ表示),ΘJA、ΘJC、ΘCA,并提供了热计算、热参考等热管理技术的详细信息。

引言

为确保产品的高可靠性,在选择IC封装时应考虑其热管理指标。所有IC在有功耗时都会发热,为了保证器件的结温低于最大允许温度,经由封装进行的从IC到周围环境的有效散热十分重要。本文有助于设计人员和客户理解IC热管理的基本概念。在讨论封装的热传导能力时,会从热阻和各“theta”值代表的含义入手,定义热特性的重要参数。本文还提供了热计算公式和数据,以便能够得到正确的结(管芯)温度、管壳(封装)温度和电路板温度。

热阻的重要性

半导体热管理技术涉及到热阻,热阻是描述物质热传导特性的一个重要指标。计算时,热阻用“Theta”表示,是由希腊语中“热”的拼写“thermos”衍生而来。热阻对我们来说特别重要。

IC封装的热阻是衡量封装将管芯产生的热量传导至电路板或周围环境的能力的一个标准。给出不同两点的温度,则从其中一点到另外一点的热流量大小完全由热阻决定。如果已知一个IC封装的热阻,则根据给出的功耗和参考温度即可算出IC的结温。

Maxim网站(制造商、布线、产品、QA/可靠性、采购信息)中给出了常用的IC热阻值。

定义

以下章节给出了Theta (Θ)、Psi (Ψ)的定义,这些标准参数用来表示IC封装的热特性。

ΘJA是结到周围环境的热阻,单位是°C/W。周围环境通常被看作热“地”点。ΘJA取决于IC封装、电路板、空气流通、辐射和系统特性,通常辐射的影响可以忽略。ΘJA专指自然条件下(没有加通风措施)的数值。

ΘJC是结到管壳的热阻,管壳可以看作是封装外表面的一个特定点。ΘJC取决于封装材料(引线框架、模塑材料、管芯粘接材料)和特定的封装设计(管芯厚度、裸焊盘、内部散热过孔、所用金属材料的热传导率)。

对带有引脚的封装来说,ΘJC在管壳上的参考点位于塑料外壳延伸出来的1管脚,在标准的塑料封装中,ΘJC的测量位置在1管脚处。对于带有裸焊盘的封装,ΘJC的测量位置在裸焊盘表面的中心点。ΘJC的测量是通过将封装直接放置于一个“无限吸热”的装置上进行的,该装置通常是一个液冷却的铜片,能够在无热阻的情况下吸收任意多少的热量。这种测量方法设定从管芯到封装表面的热传递全部由传导的方式进行。

注意ΘJC表示的仅仅是散热通路到封装表面的电阻,因此ΘJC总是小于ΘJA。ΘJC表示是特定的、通过传导方式进行热传递的散热通路的热阻,而ΘJA则表示的是通过传导、对流、辐射等方式进行热传递的散热通路的热阻。

ΘCA是指从管壳到周围环境的热阻。ΘCA包括从封装外表面到周围环境的所有散热通路的热阻。

根据上面给出的定义,我们可以知道:

ΘJA = ΘJC + ΘCA

ΘJB是指从结到电路板的热阻,它对结到电路板的热通路进行了量化。通常ΘJB的测量位置在电路板上靠近封装的1管脚处(与封装边沿的距离小于1mm)。ΘJB包括来自两个方面的热阻:从IC的结到封装底部参考点的热阻,以及贯穿封装底部的电路板的热阻。

测量ΘJB时,首先阻断封装表面的热对流,并且在电路板距封装位置较远的一侧安装一个散热片。如下图1所示:

图1. ΘJB的测量过程示意图.

ΨJB是结到电路板的热特性参数,单位是°C/W。文章JESD51-12–Guidelines for Reporting and Using Package Thermal Information,明确指出热特性参数与热阻是不同的。与热阻ΘJB测量中的直接单通路不同,ΨJB测量的元件功率通量是基于多条热通路的。由于这些ΨJB的热通路中包括封装顶部的热对流,因此更加便于用户的应用。关于ΨJB参数的更多详细说明请参考JEDEC标准的JESD51-8和JESD51-12部分。

设计者可以通过热量建模或直接测量的方式确定ΘJB和ΨJB的值。对上述任意一种方式,参见下面的步骤:

将功耗控制在适合ΘJB或ΨJB的范围内。

测定管芯温度,通常用一个芯片上的二极管来实现。

测定在距封装边缘小于1mm处的PCB温度。

测定功耗。

ΨJT是衡量结温和封装顶部温度之间的温度变化的特征参数。当封装顶部温度和功耗已知时,ΨJT有助于估算结温。

热计算

结温

TJ = TA + (ΘJA × P)

其中:

TJ = 结温

TA = 周围环境温度

P = 功耗,单位为W

TJ也可用ΨJB或ΨJT的值来计算,如:

TJ = TB + (ΨJB × P)

其中:

TB = 距离封装小于1mm处的电路板温度

TJ = TT + (ΨJT × P)

其中:

TT = 在封装顶部的中心处测得的温度。

注意:产品数据资料给出了每个器件所允许的最大结温。

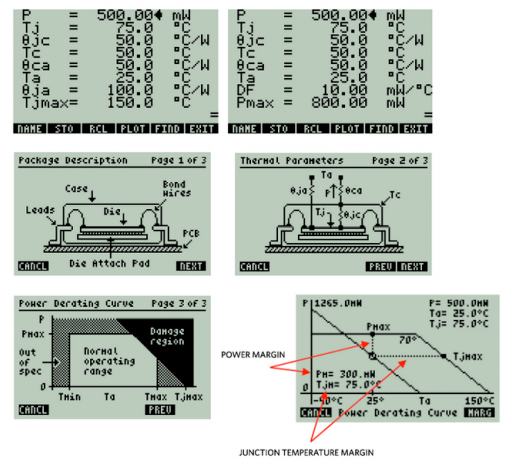

最大允许功耗

Pmax = (TJ-max - TA) / ΘJA

Maxim产品中列出的最大允许功率是在环境温度为+70°C和最大允许结温为+150°C的条件下给出的。

降额系数

该系数描述了在环境温度高于+70°C时,每升高1°C所应降低的功耗值,单位为mW/°C。

降额系数 = P / (TJ - TA)

其中:

TA的典型值为+70°C (商用)。

TJ是最大允许结温,典型值为+150°C。

为了得到在环境温度超过+70°C时(例如,对于扩展温度范围的+85°C)的最大允许功率,可通过下面公式进行计算:

Pmax85C = Pmax70C - (降额系数 × (85 - 70))

热特性及测试条件

IC封装的热特性必须采用符合JEDEC标准的方法和设备进行测量。在不同的特定应用电路板上的热特性具有不同的结果。据了解JEDEC中定义的结构配置不是实际应用中的典型系统反映,而是为了保持一致性,应用了标准化的热分析和热测量方法。这有助于对比不同封装变化的热性能指标。

JEDEC规范可在这里得到:JEDEC。注意JEDEC标准涵盖了不同的热应用场合。

JEDEC规范名称

JESD51: Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)

JESD51-1: Integrated Circuit Thermal Measurement Method—Electrical Test Method (Single Semiconductor Device)

JESD51-2: Integrated Circuit Thermal Test Method Environmental Conditions—Natural Convection (Still Air)

JESD51-3: Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-4: Thermal Test Chip Guideline (Wire Bond Type Chip)

JESD51-5: Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms

JESD51-6: Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air)

JESD51-7: High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-8: Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board

JESD51-9: Test Boards for Area Array Surface Mount Package Thermal Measurements

JESD51-10: Test Boards for Through-Hole Perimeter Leaded Package Thermal Measurements.

JEDEC51-12: Guidelines for Reporting and Using Electronic Package Thermal Information.

JEDEC多层热测试电路板规范JESD51-7摘要

High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-7规范中描述的热测试电路板非常适合Maxim IC的应用。

材质:FR-4

板层:两个信号层(顶层和底层)和两个中间层。

成品板厚:1.60 ±16mm

金属厚度

顶层和底层:2盎司铜(成品厚度0.070mm)

两个中间层:1盎司铜(成品厚度0.035mm)

介质层厚度:0.25mm到0.50mm

板尺寸:76.20mm x 114.30mm ±0.25mm (对于某一边小于27mm的封装)。

元件层的布线

测试设备放在电路板中心位置,并根据此进行布线。走线从封装本体向外延伸至少25mm。对于引脚间距为0.5mm或更大的封装,线宽应为0.25 ±10%,对引脚间距更小的封装来说,线宽应与引脚宽度相等。走线类型和走线端接规范在JESD51-7中有详细的说明。

底层的布线

器件层端接到通孔的布线可以通过走线或线缆(22 AWG或更小的铜线)连接到边缘连接器。JESD51-7规范中详细列出了不同线宽对应的电流限度。

除通孔隔离布线模式外,电源和地平面应当保持完整,且与边缘连接器的距离应当大于9.5mm。

带裸焊盘的封装

对于带裸焊盘(EP)的封装(如QFN封装,DFN封装(双列扁平无外伸引脚),EP-TQFP封装),其热特性中非常重要的一点是裸焊盘焊点下方的散热过孔的设计。在典型的热特性电路板设计中,会有一个包含4个、9个或16个通孔的阵列,就近连接到地平面上。通孔数量超过25个以后,散热改进基本趋于平缓,不会再有显著的改善。理解电路板上的散热通孔与系统热特性之间的对应关系是十分重要的。关于带裸焊盘封装的电路板设计请参见JESD51-5。

焊接覆盖率

用户焊接电路板时,应当保证焊点的覆盖率达到50%或者更高,当焊点的空白面积接近50%或更多时,将会由于未连接到散热通孔而对热阻产生严重的影响。

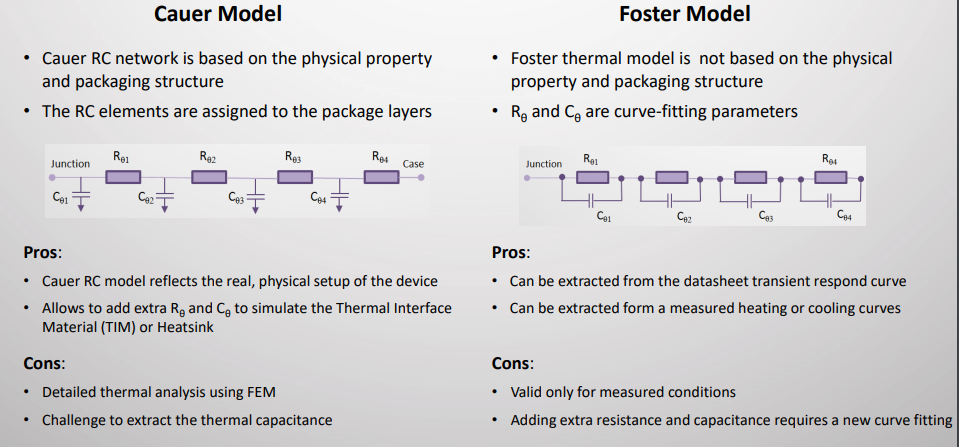

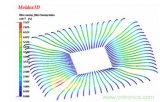

热建模

采用FLOTHERM®和其它的热分析软件可以对封装和系统实现精确的热预测。适当的热模型与经验数据相结合,可以精确地反映实际应用的情况。

电路设计工具,如PSPICE或Cadence® toolscan可用来建立简单的封装热模型。封装可以表示成电阻的形式,以电阻网络的方式连接到电路板上。确认封装模型符合经验数据后,该模型可用来预估封装结构的变化情况,包括:管芯尺寸、裸焊盘尺寸、带有保险丝的引脚、或连接到平面的地线数量。这些假设分析模型对于封装结构的定制能够给出相当精确的预估

审核编辑:郭婷

-

电路板

+关注

关注

140文章

5253浏览量

106483 -

封装

+关注

关注

128文章

9140浏览量

147894 -

PCB

+关注

关注

1文章

2265浏览量

13204

发布评论请先 登录

IC封装热阻的定义与量测技术

IC封装的热特性

IC封装原理及功能特性汇总

关于IC封装原理及功能特性分析和介绍

热阻和热特性参数的关键要点

涨知识:IC封装原理及功能特性汇总

基于RC热阻SPICE模型的GaNPX®和PDFN封装的热特性建模

IC封装的热特性

IC封装的热特性

评论