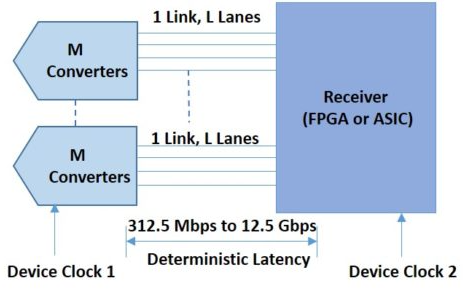

您的PCB可以处理高达12.5Gbps的速度吗,感到惊讶,对吗?JESD204B标准为串行接口提供高达12.5Gbps的比特率。这种升级允许设计人员在FPGA/ASIC上使用更少的收发器,从而减少I/O数量和封装尺寸。新标准正在高速数据转换器应用中迅速采用,例如无线基础设施收发器、软件定义无线电、医疗成像系统以及雷达和安全通信。

多个串行通道和高达 12.5G 的转换器

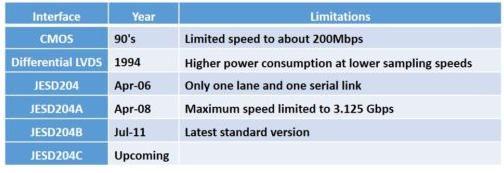

回到10年前,设计人员使用传统的单端CMOS接口,将速度限制在200Mbps左右。然后是差分LVDS,改善了信号线和电源上的噪声耦合。该接口的局限性是在较低的采样速度下功耗较高。这给了CMOS接口存在的理由,至今仍在使用。随着更快的ADC的发展,需要比并行LVDS更节能的数字接口,这种需求催生了JESD204,一种高速串行链路,将单个或多个数据转换器连接到数字逻辑器件,JESD3A的数据速率高达125.204 Gbps,JESD12B的数据速率高达5.204Gbps。

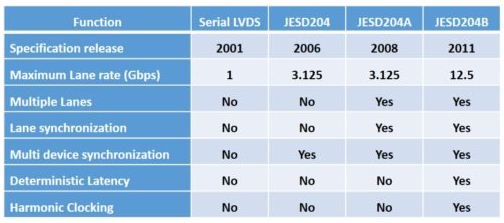

为了选择使用LVDS或各种版本的JESD204串行接口规范的最佳转换器产品,比较每个接口的特性和功能是有用的。下表提供了简短的表格比较。

为什么我们关心JESD204B?

符合JESD204B标准的数据转换器以更高的速率串行化和传输数据,从而减少数据转换器或FPGA上的引脚数量。

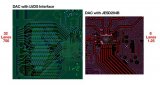

布局简单,路线更方便,因为船上的车道要少得多。

更小的封装尺寸和更低的成本。

减少对偏斜管理的需求,因为数据时钟嵌入在数据流中。

JESD204B接口可适应不同分辨率的数据转换器。这样就无需对未来的ADC和数模转换器(DAC)的收发器/接收器(Tx/Rx)板(逻辑器件)进行物理重新设计。

JESD204B标准通过使用确定性延迟简化了多通道同步。

很明显,JESD204B是先进数据采集系统设计的首选接口。该标准减少了高速数据转换器与FPGA和其他设备之间的数字输入和输出数量。更少的互连简化了布局,并有可能实现更小的外形尺寸。

审核编辑:郭婷

-

收发器

+关注

关注

10文章

3842浏览量

111532 -

无线电

+关注

关注

63文章

2216浏览量

119902 -

PCB

+关注

关注

1文章

2365浏览量

13204

发布评论请先 登录

AD9680 JESD204B接口的不稳定会导致较大的电流波动,怎么解决?

JESD204B的系统级优势

串行LVDS和JESD204B的对比

JESD204B串行接口时钟的优势

FPGA高速数据采集设计之JESD204B接口应用场景

FPGA高速数据采集设计之JESD204B接口应用场景

jesd204b ip核支持的线速率

JESD204B的优势

JESD204B FPGA调试软件加快高速设计速度

在Xilinx FPGA上快速实现 JESD204B

FPGA 的高速数据采集设计之JESD204B部分详解

搭载JESD204B编码的高速数据采集开发板

JESD204B是否真的适合你

JESD204B:高达12.5Gbps高速数据采集的新替代方案

JESD204B:高达12.5Gbps高速数据采集的新替代方案

评论