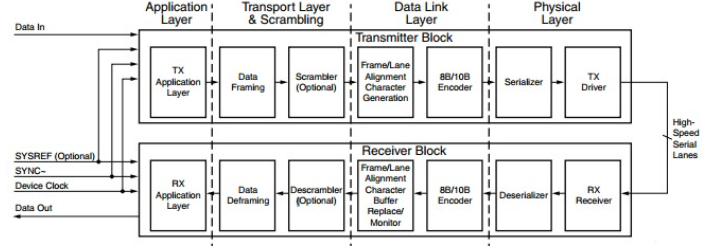

JESD204B规范是JEDEC标准发布的较新版本,适用于数据转换器和逻辑器件。如果您正在使用FPGA进行高速数据采集设计,您会听到新的流行词“JESD204B”。与LVDS和CMOS接口相比,这一较新的版本具有显著的优势,因为它包括更简单的布局和更少的引脚数。JESD204B标准采用分层架构,由3层组成,从顶部的传输层开始,延伸到中间的链路层和底部的物理层。镜像是接收器侧的结构,采用自下而上的方法(物理层->链路层->传输层)。每一层都有一个独特的功能要执行。

JESD204B 变送器流量

传输层将转换样本映射到成帧非加扰八位字节和从中映射转换样本。加扰层可以选择采用这些八位字节并对其进行加扰或解扰,以便通过扩展频谱峰值来降低EMI效应。加扰将在发射器中完成,解扰将在接收器中完成。数据链路层是将可选的加扰八位字节编码为 10 位字符的位置。该层也是进行控制字符生成或检测的地方,以进行车道对齐监控和维护。物理层是串行器/解串器或(SERDES)层,负责以线速发送或接收字符。JESD204B协议栈在发送路径中有<>个功能块,在接收路径中有<>个功能块,如下图所示。

JESD204B协议栈

JESD204B寻址数据同步,正被汽车、医疗成像、雷达和其他军用航空和工业应用所采用。JESD204B正在迅速获得模拟供应商的支持,这些供应商正在考虑将高速ADC和DAC与可编程SOC连接,所有这些SOC均可与片上串行收发器配合使用,以充分利用JESD204B串行带宽。

Synopsys 为 JESD100A/B 提供 204% 基于原生 SystemVerilog/UVM 的 VIP,具有一套全面的协议、方法、验证和生产力功能,可加速验证收敛。VIP中的每一层都满足特定需求,传输层定义数据>八位字节>帧的映射,并由传输层参数汇总。链路布局主要由 8b/10b 编码、链路同步和链路监控的定义组成。该层通过 SYNC~ 接口检测并报告各种链路错误。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

6242浏览量

243548 -

转换器

+关注

关注

27文章

9460浏览量

157152 -

JEDEC

+关注

关注

1文章

38浏览量

17944

发布评论请先 登录

JESD204B的系统级优势

在Xilinx FPGA上快速实现JESD204B

串行LVDS和JESD204B的对比

JESD204B串行接口时钟的优势

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

JESD204B协议有什么特点?

JESD204B协议介绍

JESD204B的优势

JESD204B SystemC module 设计简介(一)

JESD204B是FPGA中的新流行语吗

JESD204B是FPGA中的新流行语吗

评论