点击上方蓝字关注我们

芯片设计流程概述

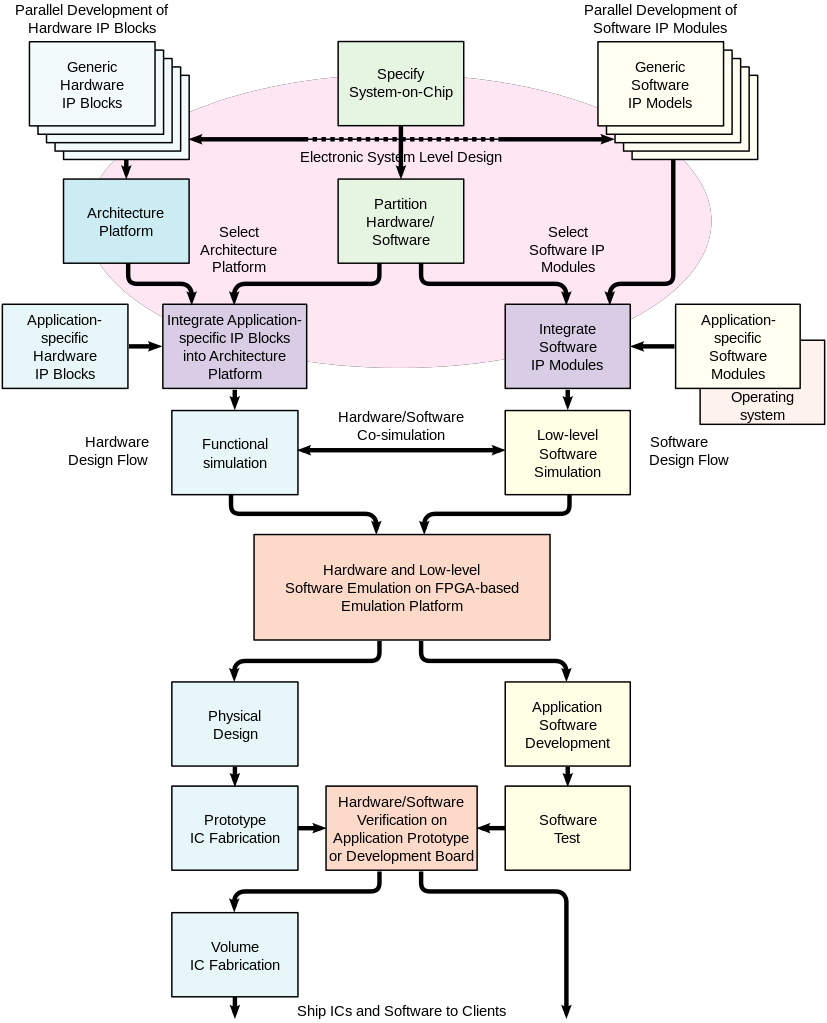

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。

1. 规格制定

芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2. 详细设计

Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3. HDL编码

使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4. 仿真验证

仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Synopsys的VCS,还有Cadence的NC-Verilog。

5. 逻辑综合――Design Compiler

仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)。

逻辑综合工具Synopsys的Design Compiler。

6. STA

Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。

STA工具有Synopsys的Prime Time。

7. 形式验证

这也是验证范畴,它是从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

形式验证工具有Synopsys的Formality。

前端设计的流程暂时写到这里。从设计程度上来讲,前端设计的结果就是得到了芯片的门级网表电路。

Backend design flow :

1. DFT

Design For Test,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。

DFT工具Synopsys的DFT Compiler

2. 布局规划(FloorPlan)

布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。

工具为Synopsys的Astro

3. CTS

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。

CTS工具,Synopsys的Physical Compiler

4. 布线(Place & Route)

这里的布线就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。

工具Synopsys的Astro

5. 寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。

工具Synopsys的Star-RCXT

6. 版图物理验证

对完成布线的物理版图进行功能和时序上的验证,验证项目很多,如LVS(Layout Vs Schematic)验证,简单说,就是版图与逻辑综合后的门级电路图的对比验证;DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求, ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气 规则违例;等等。

工具为Synopsys的Hercules

实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题,在此不说了。

物理版图验证完成也就是整个芯片设计阶段完成,下面的就是芯片制造了。物理版图以GDS II的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路,再进行封装和测试,就得到了我们实际看见的芯片。

往期推荐

往期推荐

扫码二维码

获取更多精彩

FPGA设计论坛

原文标题:芯片设计流程概述

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22491浏览量

638935

原文标题:芯片设计流程概述

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

晶圆划片机工作原理及操作流程详解

晶圆划片机工作原理及操作流程详解在半导体制造后道工艺中,晶圆划片机是核心精密装备,核心功能是将完成前道光刻、刻蚀工序的整片晶圆,精准切割为独立芯片(Die),其切割精度直接决定芯片良率与封装效率

半导体芯片键合技术概述

键合是芯片贴装后,将半导体芯片与其封装外壳、基板或中介层进行电气连接的工艺。它实现了芯片与外部世界之间的信号、电源和接地连接。键合是后端制造中最关键的步骤之一,因为互连质量直接影响器件的可靠性、性能和可扩展性。

芯片ATE测试详解:揭秘芯片测试机台的工作流程

ATE(自动测试设备)是芯片出厂前的关键“守门人”,负责筛选合格品。其工作流程分为测试程序生成载入、参数测量与功能测试(含直流、交流参数及功能测试)、分类分档与数据分析三阶段,形成品质闭环。为平衡

借助 AI 从流程可视化到流程优化的 6 个步骤

借助 Minitab Solution Center与 Simul8,将日常流程损耗转化为可量化的效能提升 生活各处都看到流程的影子,无论是逛杂货店、排队买咖啡,还是收拾行李准备度假。你是否曾发现

航天级抗辐照电源芯片研发全流程:从设计到上市的10大核心环节

电源管理芯片是电子设备的“能量心脏”,而国科安芯ASP3605作为一款 航天级抗辐照DC/DC Buck电源芯片 (其裸die常作为核心模块用于航天集成电源方案),其研发流程需额外攻克极端太空环境下

使用6e00系列的芯片,clc计算流程求解?

大家好,请教个问题,我在使用6e00系列的芯片,调试时遇到了疑惑:clc单元,设置所有的系数为0,pwm_period为0x13870, 反馈值也是0,期望值也是0,此时应该输出0才对,但是此时

发表于 11-09 23:06

ADI Power Studio工作流程与工具概述

ADI Power Studio是一套面向应用工程师及高级电源设计用户的综合性产品系列,能够有效简化整个电源系统的设计流程,提供从初步概念到测量和评估的全程支持。Power Studio提供统一

芯片开封(Decap)的流程

在集成电路分析领域,芯片开封(Decapsulation,简称Decap)是一项至关重要的技术环节。无论是进行失效分析还是反向工程研究,芯片开封都是打开微观世界大门的第一把钥匙。这项技术旨在精确移除

霍尔芯片盐雾试验测试流程

霍尔芯片盐雾试验的测试流程涵盖预处理、试验箱配置、样品放置、参数控制、周期测试、结果评估及报告生成等关键环节,具体流程如下: 1、样品准备与预处理: 清洁:使用乙醇或氧化镁溶液等非研磨性清洁剂彻底

电源芯片一次筛选:复杂流程下的高要求与高效应对

一次筛选:芯片可靠性的“第一道防线”在集成电路从设计到量产的全流程中,一次筛选是保障产品质量的核心环节。它位于封装测试阶段前端,通过多维度的严格测试,如电性能测试、环境应力筛选(如高低温、湿度测试

Thread标准认证概述

本篇知识库文章概述了开发人员如何将其Thread物联网设备进行Thread Group认证所需的步骤,并重点介绍使用Silicon Labs(芯科科技)的EFR32无线射频器件的相关流程。

芯知识|广州唯创电子语音芯片开发全流程解析:从选型到量产的实践指南

一、语音芯片开发的核心逻辑与价值定位在智能化设备井喷式发展的背景下,语音交互已成为人机界面的重要入口。广州唯创电子作为国内领先的语音芯片方案商,其开发流程设计始终围绕功能适配性、开发效率和量产可靠性

芯片设计流程概述

芯片设计流程概述

评论