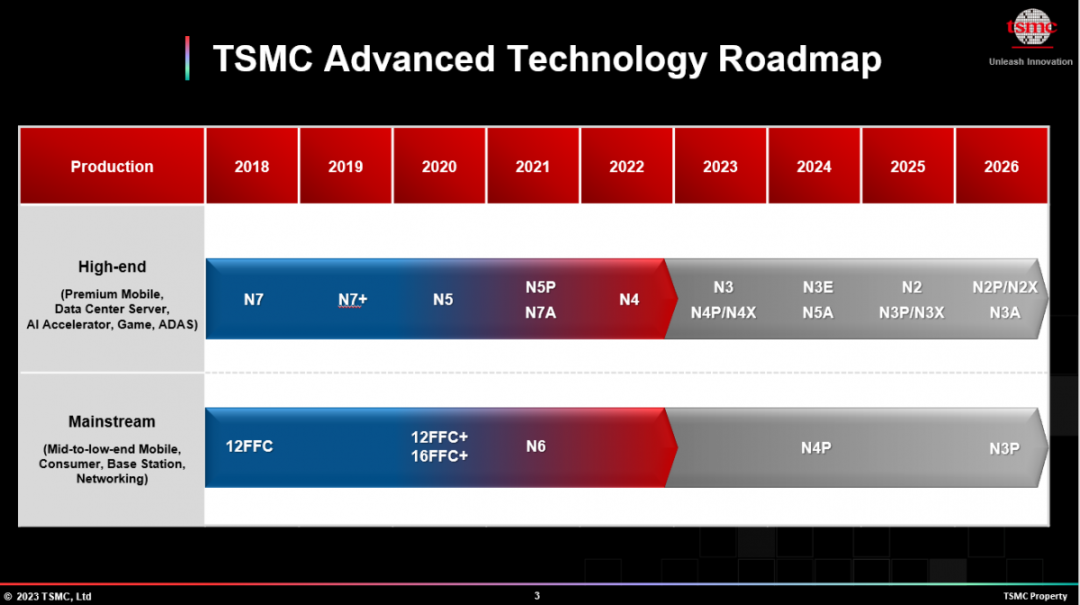

上个月的2023北美技术研讨会上,台积电又又又透露了一些N2家族工艺节点的新消息——计划中的2nm工艺节点会在2025-2026年到来。结合这次的消息,以及过去1、2年三星和Intel透露相关各自2nm节点的消息,本文尝试展望一下2025年以后的2nm工艺。

有关未来工艺展望,或者foundry厂路线图,是这几个主要市场参与者给予市场信心的关键。所以虽然3nm都还没真正拿在我们手上,Intel、三星、台积电也早就在宣传再靠后的2nm,甚至更先进的工艺了,即便其中的某些八字都还没一撇。

上个月的2023北美技术研讨会上,台积电又又又透露了一些N2家族工艺节点的新消息——计划中的2nm工艺节点会在2025-2026年到来。那么结合这次的消息,以及过去1、2年三星和Intel透露相关各自2nm节点的消息,本文尝试展望一下2025年以后的2nm工艺。

需要指出的是,以现如今半导体制造尖端工艺的复杂度和成本投入,即便foundry厂公布了技术路线图,未来的变数也依然可能非常大——甚至连节点量产时间都只能做个参考。三星几年前就曾说过3nm工艺有望于2020年全面上线;Intel早于2010年说过2017年就上马7nm工艺;台积电的放卫星名场面更多...所以本文的所有内容,在2025年之前就仅供参考。

最早的2nm,可能来自Intel?

从路(fang)线(wei)图(xing)计划表来看,台积电和三星的一致口径是2nm工艺预计于2025年开始量产——但起码也是2025年下半年或者更晚的时间。

这里需要注意的问题是,“开始量产”“准备好量产”并非芯片问世时间。比如如果台积电N2工艺将在2025年下半年开始量产,则N2工艺的芯片真正上市至少需要等到2026年;且从营收的角度来看,N2工艺产生的营收也要到2026年才会反映到财报中。

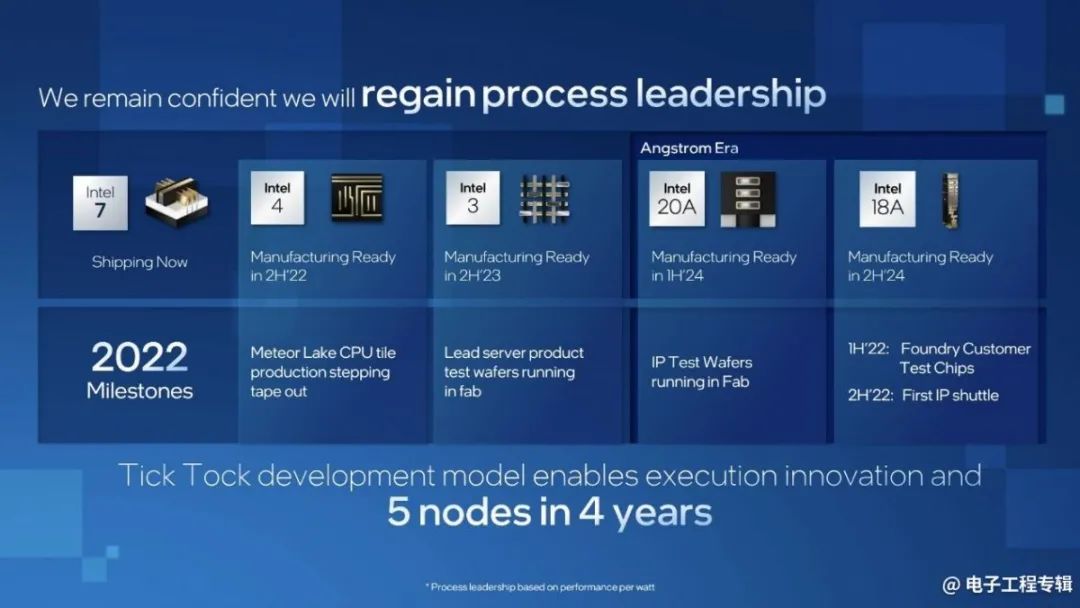

Intel这边:自从7nm/5nm时代,在半导体制造工艺技术上被台积电和三星赶超,Intel就改变了技术迭代策略。从2022年Intel投资者会议更新过的计划表来看,Intel 20A工艺——通常可看作是Intel版本的2nm工艺,即便Intel现在在市场宣传上很忌讳去谈x nm——“准备好量产”的时间是2024年上半年。

今年2月Intel在国内举办的战略媒体沟通会上再度确认了Intel 20A“测试芯片已流片”。不过需要注意的是,因为现在foundry厂的工艺名称(比如Intel 20A, TSMC N2, Samsung 2GAP)越来越放飞自我,而工艺名称并不代表晶体管或器件的实际物理尺寸,加上现在我们并不十分清楚这三家的“2nm”工艺的器件尺寸,所以仍然很难在同一平台上去说这三者是同代工艺。

Intel 20A工艺的后续工艺是18A——也是Intel此前宣称要重返半导体制造工艺王座的一代节点,预期“准备好量产”的时间已经被提前到了2024年下半年。如果各家foundry厂的未来工艺能如期交付,则显然Intel会是最快的。

但如前文所述,尖端制造工艺foundry厂有放卫星的传统——当然这也不是他们想看到的。毕竟尖端制造工艺的技术难度和成本攀升速度,造就了大量的不确定性。

全部切换至GAAFET的一代工艺

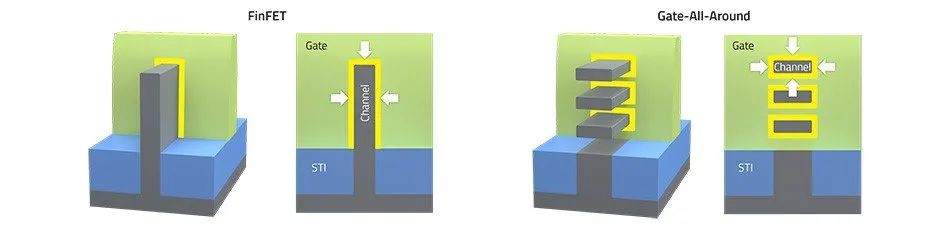

关注尖端制造工艺的同学应该都知道,三星在3nm这代工艺上就要开始采用GAAFET结构的晶体管上,替换用了这么多年的FinFET。GAA全称gate-all-around——有关GAAFET器件结构,我们此前已多有撰文提及。从示意图就不能看出,原先的fin被横置过来——横置以后叫做nanosheet。

这种结构的晶体管有效沟道宽度不仅灵活,而且比FinFET更大,能够在器件整体尺寸缩减的情况下,达成更高的驱动电流、更出色的性能、更低的漏电流。调整nanosheet的宽度和数量,是能够表现这种结构的灵活性的;则在更高性能、更低功耗之间就有了更大的选择余地。

台积电决定在N2工艺上采用nanosheet,而Intel则决定在Intel 20A工艺节点上采用RibbonFET。这些都是GAAFET结构的具体实施。

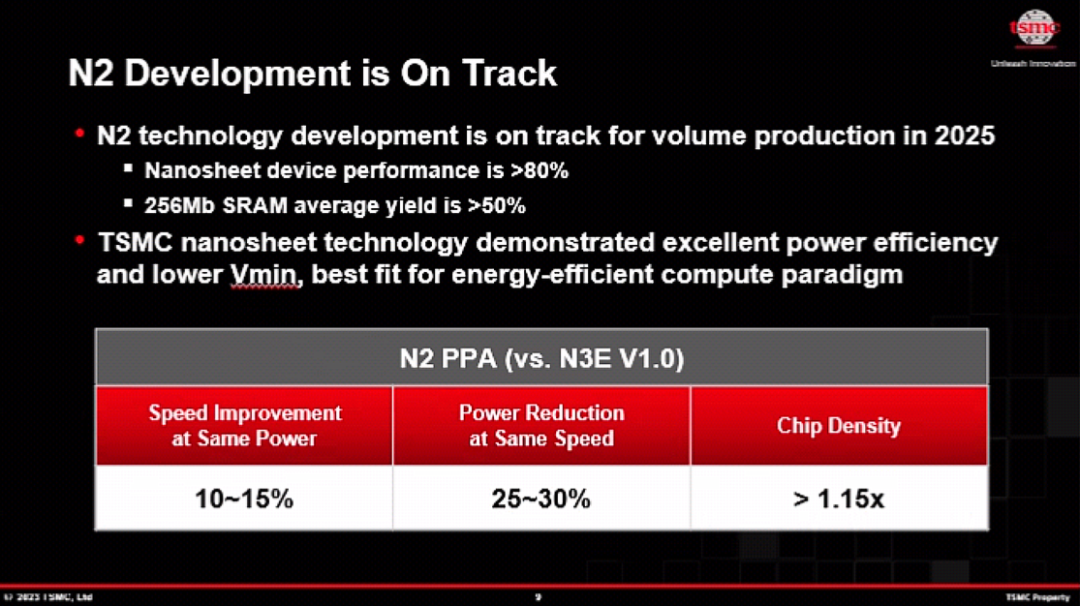

目前对外公开了结构、2nm节点迭代造成密度与性能变化的,台积电似乎是唯一一个。台积电在去年的技术研讨会上提到,和N3E工艺相比,在相同功耗、相同晶体管数量的情况下,N2工艺能够带来性能方面10%-15%的提升;或者同频率与复杂度下功耗25%-30%的下降;晶体管密度提升1.1倍。

性能、功耗数字变化,就台积电工艺节点迭代的传统来看,算是比较合理的。而且需要考虑到换晶体管结构,前期经验不足导致的效率问题。但晶体管密度只提升1.1倍,就显得非常拉垮。但需要注意这里的1.1倍密度提升,是基于一颗典型芯片包含50%的逻辑电路、30%的SRAM单元,以及20%的模拟电路。

通常我们说N5→N3工艺1.6倍晶体管密度提升,是特指逻辑电路。工艺节点之间,模拟和存储电路部分的器件尺寸微缩速度通常总是慢于逻辑电路的。而且近两代先进工艺节点,这两者的微缩幅度尤其小。但无论如何1.1x都不是个很理想的数字。

在今年的技术研讨会上,台积电似乎更新了这个数字,变为>1.15x——对比对象当然仍是N3E。其实N3E相比N3的器件密度,传说还变大了(这也是N3可能被抛弃的一个体现)。比较正面的信息是,在本次活动上台积电说N2技术开发仍在轨道上,且不变的是2025年进入量产。

台积电表示在正式进入大规模量产之前,其GAA晶体管性能正好于目标规格的80%,且256Mb SRAM测试芯片的平均良率已经超过了50%。据说能效和Vmin等方面的数据都比较理想,“非常适用于能效计算”需求。最近Synopsys才发布新闻稿说正与台积电合作,针对N2工艺推进数字与定制设计EDA流程。

除了台积电的另外两家,似乎尚未就2nm工艺公布什么像样的数字。Intel只是说Intel 4相比Intel 7会有20%的每瓦性能提升;Intel 3相比Intel 4则有18%的每瓦性能提升;Intel 20A相比Intel 3有15%的每瓦性能提升。

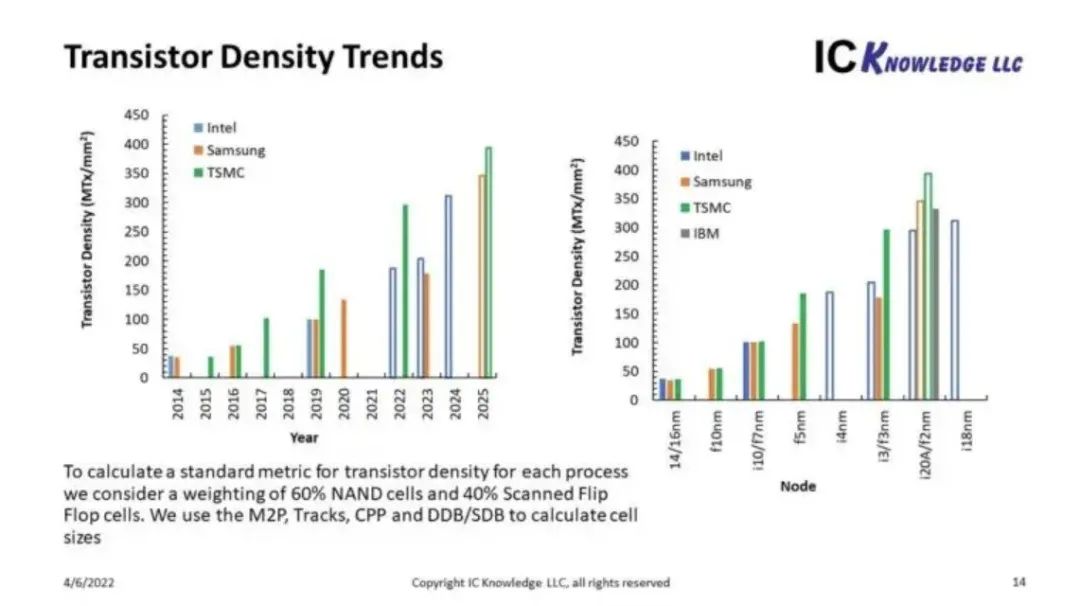

Scotten Jones去年4月写过一篇文章,提到Intel 20A相比上代工艺会有1.6x密度提升——这说的当然就是逻辑电路的晶体管典型统计方式了。

来源:IC Knowledge

从当时他给出的预测图来看,如果只看晶体管密度,那么台积电和三星仍将在绝对值上于2nm工艺节点上有所领先。这大约也能解释Intel 20A的推出时间将早于台积电N2和三星2GAP。或者说Intel 20A大概是实现了差拍/错位竞争的。

的确在先进制造工艺越往后发展的当下,器件物理尺寸变化在不同的foundry厂之间可能会呈现出很大的不同;不同foundry厂的工艺也越来越难以划归到某一个统一的nm节点下。当然也可能是Intel的技术偏向性、竞争的市场领域有差异。但需要指出,IC Knowledge的这份数据可靠性是存疑的。

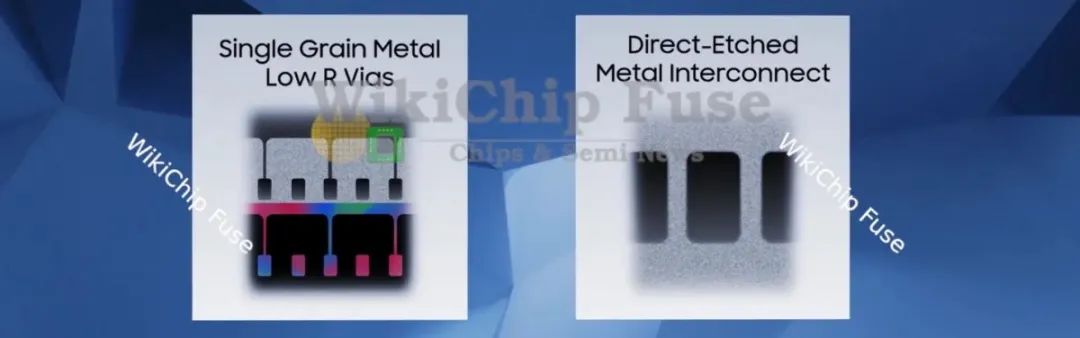

来源:WikiChip Fuse

有关三星2GAP的消息是最少的,我们能够搜到有关三星2GAP的消息,大部分都是相关其2025年这个时间节点的。三星Foundry公开有关2GAP为数不多的信息是,2GAP会达成更高的晶体管密度——具体到晶体管结构上,MBCFET(也就是GAAFET)会多一片nanosheet,也就达成了总共4片nanosheet。这一点倒是和Intel的RibbonFET类似,目的都是进一步提升驱动电流。

来源:WikiChip Fuse

另外三星去年还曾提过正着力在部分金属层堆栈的提升上,包括single grain metal(着力于低电阻),以及direct-etched metal interconnect。

有关晶背供电(backsidepowerdelivery)

不过在三星2GAP工艺上,我们还了解到一则信息:那就是三星2nm会采用名为“BSPDN”的技术,全称backside power delivery network。三星是在SEDEX 2022上提到这则消息的。The Lec报道说BSPDN的概念最早是IMEC于2019年谈到的;IEDM 2021上也有相关2nm工艺的paper提到过backside power delivery。当时这篇paper提到,对应的设计相比于frontside power delivery达成了44%的性能提升、32%的能效提升。

关注过我们此前对Intel制造工艺解读的同学,对于这里的backside power delivery应该不会陌生——这也是未来半导体制造工艺的趋势了。实际上Intel、台积电的计划表上也都能看到这项技术的实施。

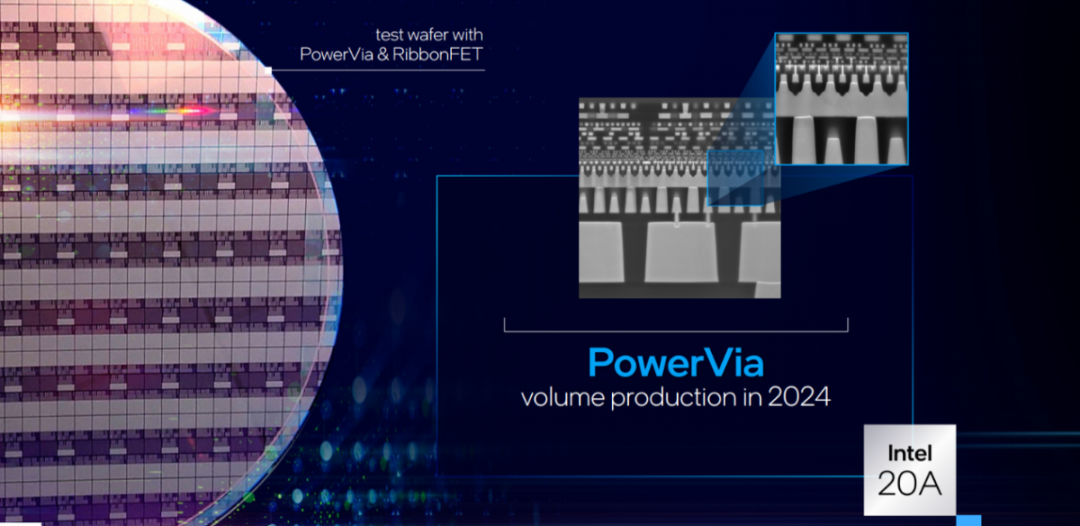

Intel在此前的技术介绍中谈到过Intel 20A工艺准备采用一种名为PowerVia的技术,也就是backside power delivery。可能在具体实施上,三家的方案会存在一些差异。Intel的PowerVia是将供电网络,或者叫电源轨全部移到晶体管另一侧。传统的互联技术,供电和信号线路是混杂在一起的——或者说都在同一侧,对性能和功耗都会有影响。

因为传统方案在设计上需要确保没有信号干扰,供电线路往往就是信号通路的干扰,而互联信号通路本身也会对供电电阻产生影响。所以将两者分开放到晶体管两侧,也就能够解决问题。如此,供电网络可以直接连接晶体管,不需要通过上方的互联堆栈;而信号互联也能更为密集,信号传输效率,包括延迟表现也有了提升;电力互联部分电阻也减少了。最终也就实现了性能、功耗、面积的优化。

三星此前在SEDEX 2022上介绍说,和frontside power delivery网络不同的是,BSPDN采用backside方式;frontside这一面放逻辑功能,而backside一面则用于供电或信号路由(signal routing)。主体上也是把供电网络放到背面,尝试解决传统方案的各种路由拥塞问题。

就三家的放嘴炮程度(不是)来看,于backside power delivery这一技术上可能落后的是台积电。从去年年中台积电的欧洲技术研讨会来看,2nm时代最初的N2工艺不会用上backside power delivery方案,或者叫backside power rails。台积电当时没说是什么原因。不过AnandTech此前报道说,台积电发现这项技术会增加不少额外工艺步骤,台积电期望在最初的GAAFET实施上避开这些环节。

台积电N2缺失backside power delivery可能是N2的晶体管密度提升并不大的原因之一。2026年的N2P工艺才会用上这个技术,以期解决BOEL流程中via电阻增加的更多问题,当然也会对应的提升晶体管性能、降低功耗。将供电网络和数据连接进行解耦,在过去这么多年来都是foundry厂的技术热点。

只不过台积电并未提到N2P将会带来多大程度的性能、功耗表现、晶体管密度的提升。AnandTech说backside power rails能够带来“个位数功耗表现提升”和“两位数的晶体管密度提升”——如此看来,N2P相比N2会是个比较大幅度的同代演进。

最后值得一提的是,从台积电目前的计划表来看,其N2工艺家族还有个N2X工艺——类似于N3时代的N3X,是个性能增强版工艺,主要面向HPC类别的应用,比如说高端CPU处理器。具体情况未知。

从前述所有资料来看,预期台积电N2和2GAP最早与我们正式见面需要等到2026年,早如Intel 20A的问世起码也得到2025年了——而且这些时间的可靠性都还相当值得怀疑。不过2nm时代的市场竞争或许会变得更加惨烈,不仅是因为器件新结构的全面变迁和技术迭代,还在于Intel和三星都有在2nm节点与台积电一较高下的决心。

审核编辑 :李倩

-

台积电

+关注

关注

44文章

5787浏览量

174739 -

工艺

+关注

关注

4文章

708浏览量

30109 -

半导体制造

+关注

关注

8文章

493浏览量

25827

原文标题:聊聊2025年要到来的2nm工艺

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

2nm“诸神之战”打响!性能飙升+功耗骤降,台积电携联发科领跑

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

全球首款2nm芯片被曝准备量产 三星Exynos 2600

今日看点丨三星美国厂2nm产线运作;《人工智能生成合成内容标识办法》正式生效

三星代工大变革:2nm全力冲刺,1.4nm量产延迟至2029年

台积电2nm良率超 90%!苹果等巨头抢单

台积电2nm制程良率已超60%

手机芯片进入2nm时代,首发不是苹果?

台积电加大亚利桑那州厂投资,筹备量产3nm/2nm芯片

2025年全球半导体产业十大看点

台积电设立2nm试产线

2025年半导体行业竞争白热化:2nm制程工艺成焦点

台积电2nm工艺将量产,苹果iPhone成首批受益者

台积电分享 2nm 工艺深入细节:功耗降低 35% 或性能提升15%!

聊聊2025年要到来的2nm工艺

聊聊2025年要到来的2nm工艺

评论