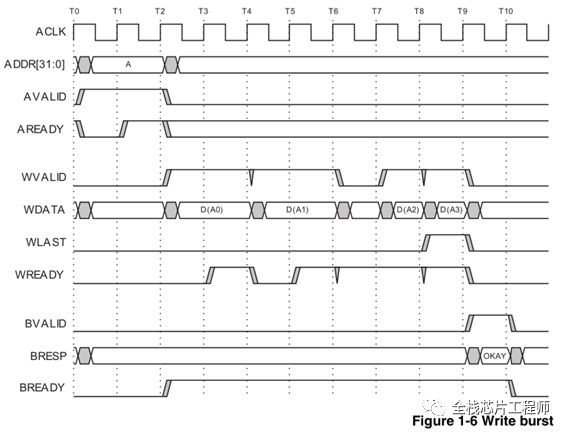

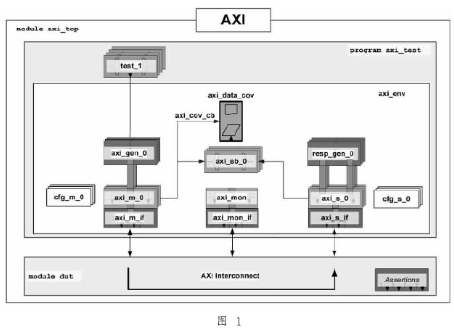

生成的IIP代码用AMBA VIP进行仿真,发现突发写应答不符合协议,按照协议,突发写只需要在写完成后,回复一个应答信号即可。

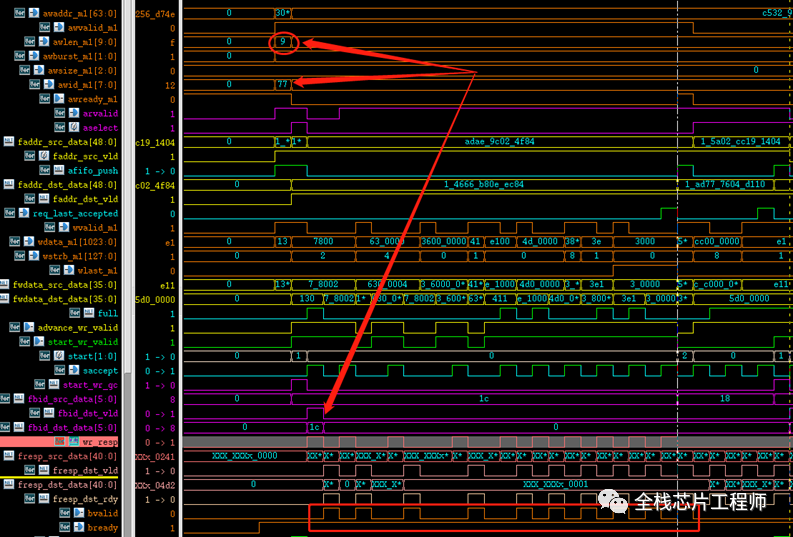

而波形是burst每个写操作响应通道都在应答,且只有第一个应答有正确的ID。

可以看到仿真波形是burst写期间,写通道一直在回复bvalid,而且只有第一个回复的ID是正确的,原因是每写一次resp_fifo就会把bid_fifo的值给清掉。

我们应该改成最后一次写wlast时,才清掉bid_fifo并同时给一次resp信号即可。

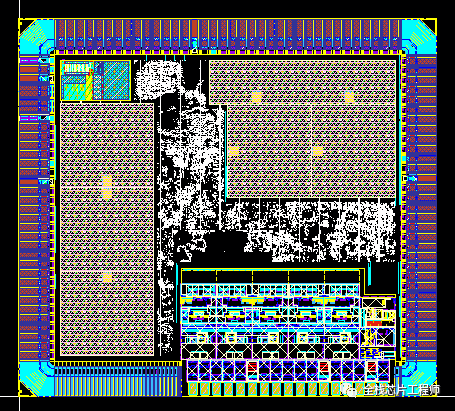

实战MCU+ISP图像处理芯片版图

实战ISP图像算法效果

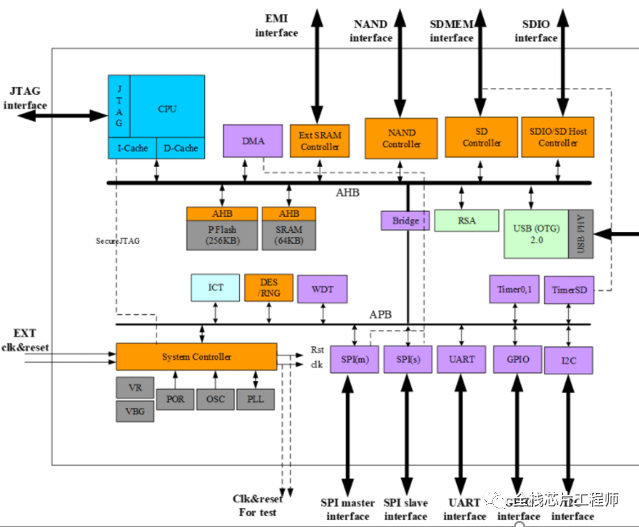

以项目驱动的方式介绍MCU芯片全流程设计的方法;

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FIFO芯片

+关注

关注

0文章

10浏览量

9125 -

AMBA

+关注

关注

0文章

70浏览量

16118 -

axi协议

+关注

关注

0文章

8浏览量

2453

原文标题:AXI IIP突发写的bug定位

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

利用开源uart2axi4实现串口访问axi总线

,可以实现跨fpga平台使用。利用uart2axi4我们可以通过python,轻松访问axi4_lite_slave寄存器,大大方便fpga工程师进行系统调试和定位bug。

NVMe IP之AXI4总线分析

。AXI4协议规定了数据传输的信号描述、通道特性和握手机制,并指定了事务的过程和属性,例如突发数据传输的数量、每次传输的字节大小、突发类型和保护类型。

1.1 AXI4总线类型

AMB

发表于 06-02 23:05

玩转Zynq连载3——AXI总线协议介绍1

● 基于特定地址进行的突发传输●通过独立的读和写通道实现低成本直接内存访问(DMA)●支持无序数据传输●提供多级寄存器锁存的支持,实现更好的时序收敛 1.1 AXI版本介绍AXI协议是

发表于 05-06 16:55

Vivado中AXI互连的突发模式

我一直在使用精简版的AXI接口,但我需要使用突发模式来加快传输速度。我不太了解如何更改界面,有人可以告诉我如何在Vivado中更改我的IP以使用突发模式吗?非常感激

发表于 04-15 07:21

高级可扩展接口(AXI)简介

主机和从机用于交换信息。优先级仲裁器确定当前哪个主机使用该总线,而中央解码器执行从机选择。突发执行操作可能需要花费多个总线周期才能完成。每个突发传输都包括一个地址和控制阶段,随后是一个数据阶段。 AXI

发表于 09-28 10:14

ARM系列 -- AXI协议资料汇总(一)

。 2、AXI通道之间的关系前面说到AXI的五个通道是独立的,但通道间必须保持一定的约定关系:写回复必须在一次写事务的最后一个写数据之后读数据必须在接收到读地址信号之后通道间握手必须满

发表于 04-08 09:34

AXI接口协议详解

4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;AXI

发表于 04-08 10:45

看看Axi4写通道decoder的设计

读写分离的设计在Axi4总线中,读和写通道是完全相互独立,互不干扰。故而无论是在设计Decoder还是Arbiter时,均可以采用读写分离的方式。如前文所述,SpinalHDL在基于Axi4总线

发表于 08-03 14:27

AXI 总线和引脚的介绍

1、AXI 总线通道,总线和引脚的介绍 AXI接口具有五个独立的通道: (1)写地址通道(AW):write address channel (2)写数据通道( W): write d

发表于 01-05 08:13

•1.1w次阅读

高级可扩展接口(AXI)简介

主机和从机用于交换信息。优先级仲裁器确定当前哪个主机使用该总线,而中央解码器执行从机选择。突发执行操作可能需要花费多个总线周期才能完成。每个突发传输都包括一个地址和控制阶段,随后是一个数据阶段。AXI

关于AXI BRAM控制器的相关内容

所有与axis主设备的通信都是通过一个5通道的axis接口进行的。所有写操作都在AXI总线的写地址通道(AW)上启动,该通道指定了写事务的类型和相应的地址信息。

AXI3与AXI4写响应的依赖区别

上面两图的区别是相比AXI3,AXI4协议需要确认AWVALID、AWREADY握手完成才能回复BVALID。为什么呢?

AXI IIP突发写的bug定位如何解决?

AXI IIP突发写的bug定位如何解决?

评论