ADS127L11是德州仪器在2021年发布的高分辨率高采样率ΣΔADC,在评估其噪声和有效分辨率的时候可以运用本文论述的基于Histogram Analysis的方法。

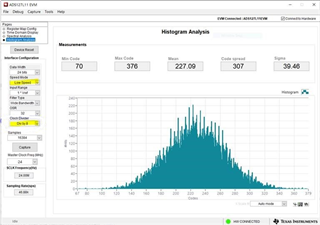

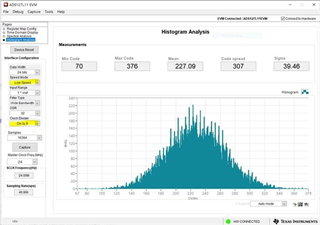

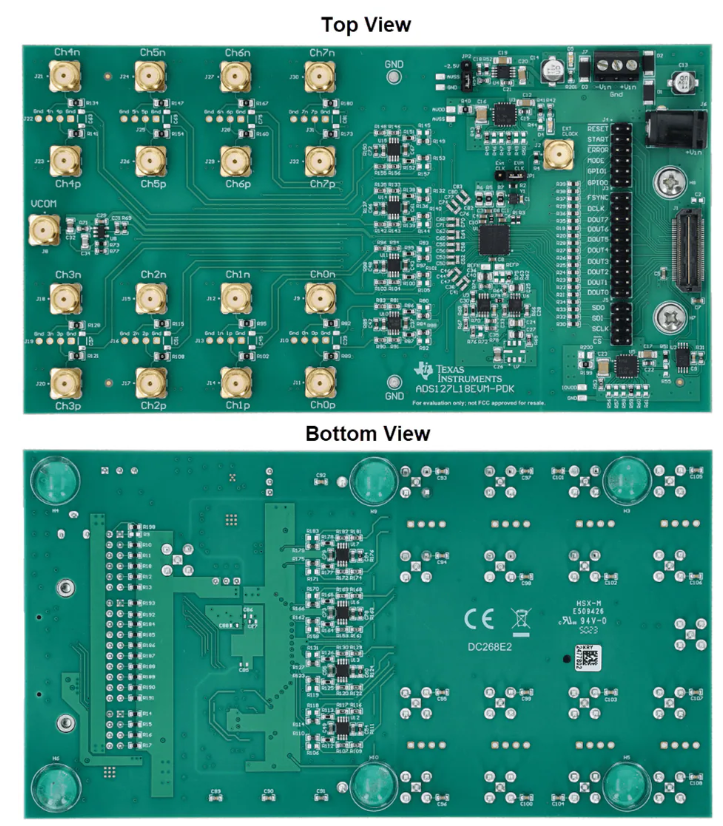

首先给ADS127L11EVM输入一个稳定的直流电压源,该直流源需要深度去耦以减少输入的噪声影响,然后对其进行大量的重复采样。采样的统计结果会显示在ADS127L11EVM-PDK GUI的Histogram Analysis界面中。如图1统计了16384次采样结果。

图1. ADS127L11EVM-PDK GUI的Histogram Analysis

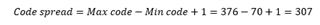

Code spread是ADC输出code的峰峰值,在图1中为307。

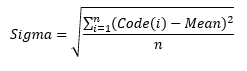

在统计结果中,还有一个名为Sigma(σ)的参数,它的定义为统计结果的标准差。

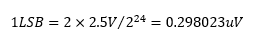

其中Code(i)是每次采样的结果,n是采样样本量16384,Mean是所有样本的平均值,在图1中为227.09。我们可以利用Sigma计算出有效分辨率。选择ADC的输入范围为±2.5V,则满幅度范围为FSR为5V,1LSB的值为,

可以运用Code spread和Sigma分别计算出噪声的峰峰值(Vpp)和均方根值(Vrms)。

运用可以计算出有效分辨率,

运用可以计算出无噪声代码分辨率Noise Free Code Resoltuion。超过这个位数的输出代码是没有明确解析的,所以要保守的评估ADC的分辨率可以用这个指标。

需要注意本文计算的有效分辨率和有效位数ENOB是有区别的。ENOB的定义是在输入满量程正弦波的时候,通过测量信纳比(SINAD)得到的。

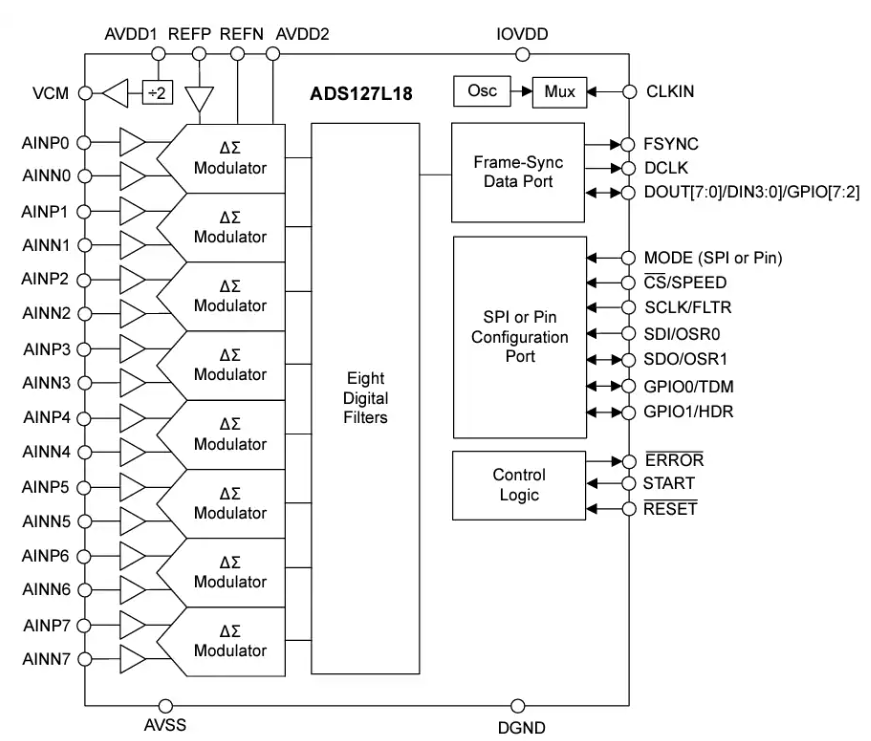

还要注意ADS127L11能支持高的采样率,尤其在High Speed Mode的时候,需要为参考输入和ADC输入选择合适的buffer(比如THS4551)以提供足够的驱动能力,否则Histogram Analysis就会引入因驱动能力不足而导致的误差。REF6225集成了buffer,适合用于ADS127L11的参考。

ADS127L11EVM默认的输入时钟是24MHz。在使用Low Speed Mode的时候需要将Clock Divider设置为Div by 8以满足该模式最高3.2MHz时钟频率的要求。

审核编辑:郭婷

-

adc

+关注

关注

100文章

7374浏览量

553670 -

电压源

+关注

关注

2文章

423浏览量

34553 -

分辨率

+关注

关注

2文章

1118浏览量

43244

发布评论请先 登录

ADS127L11和ADS127L01相比主要突出的特点有哪些?

基于Histogram Analysis的方法

ADS127L11资料介绍

理解和运用ADS127L11EVMGUI中的HistogramAnalysis

ADS127L11 400kSPS、宽带宽、24位、Δ-Σ ADC数据表

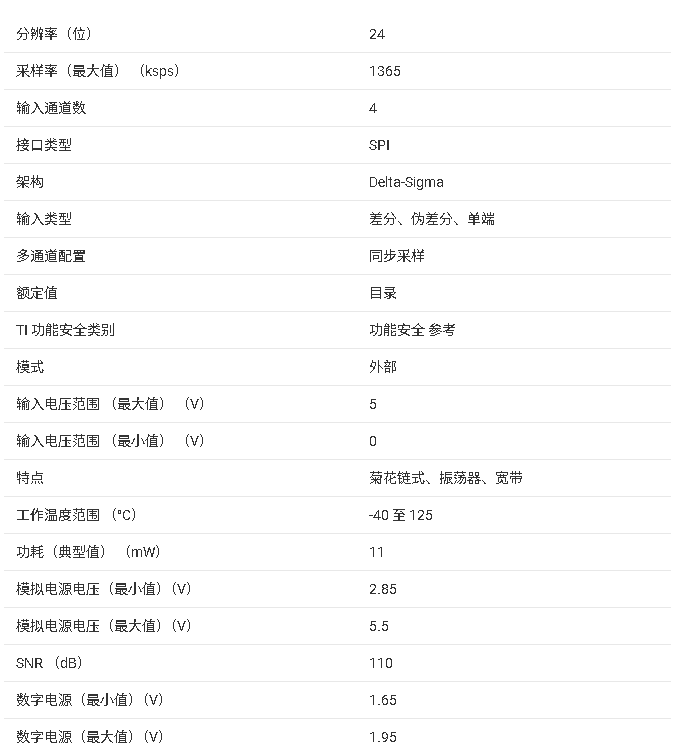

Texas Instruments ADS127L18 24 位模数转换器数据手册

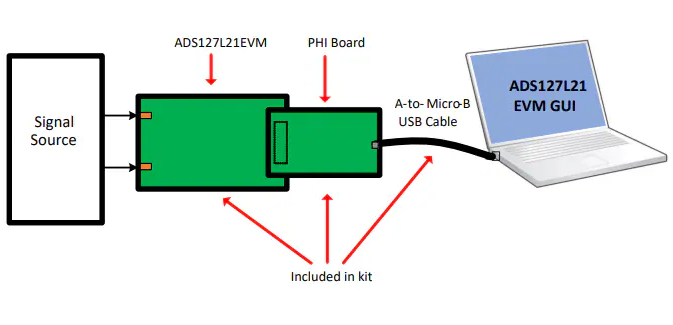

Texas Instruments ADS127L18EVM-PDK 评估模块(EVM)数据手册

ADS127L21EVM-PDK评估套件技术解析与应用指南

ADS127L14/ADS127L18 ADC 产品文档总结

理解和运用ADS127L11EVM GUI中的Histogram Analysis

理解和运用ADS127L11EVM GUI中的Histogram Analysis

评论