DIP就是插件,采用这种封装方式的芯片有两排引脚,可以直接焊在有DIP结构的芯片插座上或焊在有相同焊孔数的焊位中。其特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。但是由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差。 DIP是最普及的插装型封装,应用范围包括标准逻辑 IC,存贮器 LSI,微机电路等。小外形封装( SOP)。派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP) 、TSSOP(薄的缩小型SOP)及 SOT(小外形晶体管)、SOIC(小外形集成电路)等。

DIP器件组装设计缺陷

01

PCB封装孔大

PCB的插件孔,封装引脚孔按照规格书绘制,在制版过程中因孔内需要镀铜,一般公差在正负0.075mm。PCB封装孔比实物器件的引脚太大的话,会导致器件松动,上锡不足、空焊等品质问题。

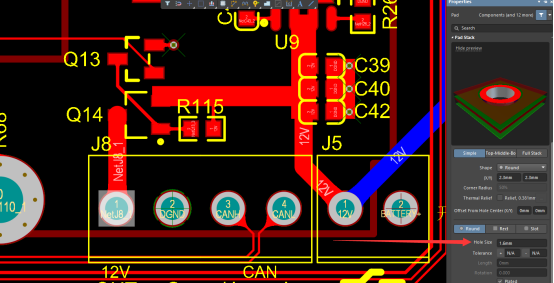

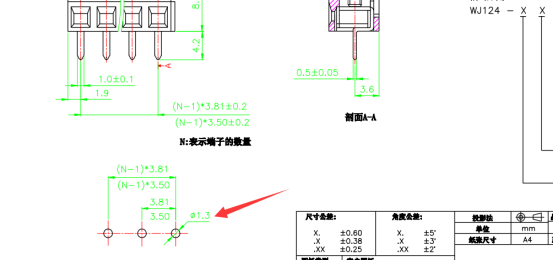

见下图:使用WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)的器件引脚是1.3mm,PCB封装孔是1.6mm,孔径太大导致过波峰焊时空焊。

接上图,按设计要求采购WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)的元器件,引脚1.3mm是正确的。

02

PCB封装孔小

PCB板中插件元器件焊盘上的孔小,元器件无法插入。此问题解决办法只能是把孔径扩大再插件,但是会孔无铜。如果是单双面板可以使用此方法,单双面板都是外层电气导通的,焊上锡可以导通。多层板插件孔小,内层有电气导通的情况下只能重做PCB板,因内层导通无法扩孔补救。

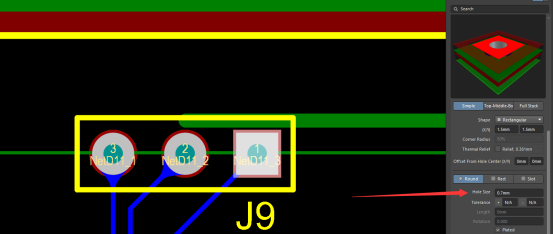

见下图

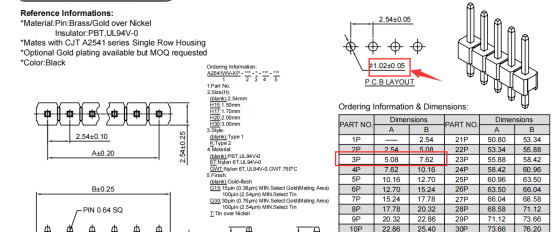

按设计要求采购A2541Hwv-3P_A2541HWV-3P(CJT)的元器件,引脚是1.0mm,PCB封装焊盘孔是0.7mm,导致无法插入。

接上图,按设计要求采购A2541Hwv-3P_A2541HWV-3P(CJT)的元器件,引脚1.0mm是正确的。

03

PCB封装引脚距离与元器件不符

DIP器件的PCB封装焊盘不只是孔径与引脚一致,而且引脚的间距同样要一样的距离。引脚孔的间距与器件不一致会导致器件无法插入,脚距可调的元器件除外。

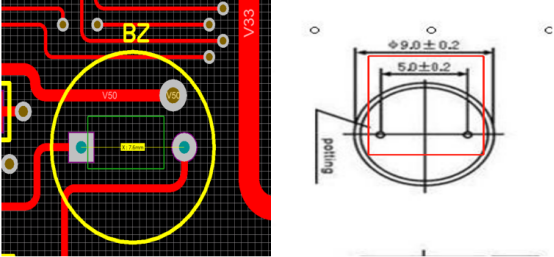

见下图:PCB封装引脚孔距是7.6mm,采购的元器件引脚孔距是5.0mm,相差2.6mm导致器件无法使用。

04

PCB封装孔距太近连锡短路

PCB设计绘制封装时需注意引脚孔的距离,引脚孔间距小即便是裸板能生成出来,在组装时过波峰焊也容易造成连锡短路。

见下图:可能因引脚距离小导致连锡短路,波峰焊连锡短路的原因有很多种,如果在设计端能够提前对可组装性进行预防,可降低问题的发生率。

DIP器件引脚上锡不足的真实案例

物料关键尺寸与PCB焊盘孔尺寸不匹配问题

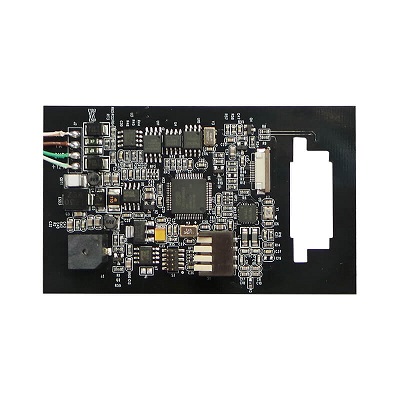

问题描述:某产品DIP过完波峰焊后发现,网络插座固定脚焊盘上锡严重不足,属于空焊。

问题影响:导致网络插座与PCB板的稳固性变差,产品使用过程中会导致信号pin脚受力,最终导致信号pin脚的连接,影响产品性能。造成用户使用中出现故障的风险;

问题延伸:网络插座的稳固性差,信号pin脚的连接性能差,存在品质问题。因此可能给用户带来安全隐患,最终造成的损失是不可想象的。

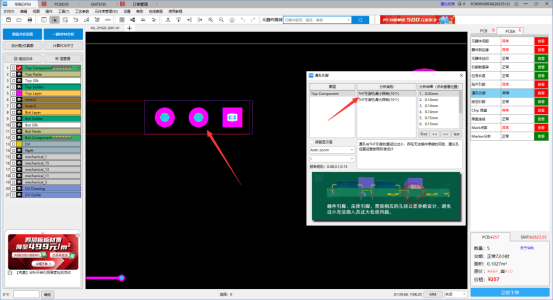

华秋DFM组装分析功能,对DIP器件的引脚有专项检查。检查项有通孔的引脚数、THT引脚限大、THT引脚限小、THT引脚的属性,引脚的检查项基本涵盖DIP器件引脚设计可能出现的问题。

在设计完成后使用华秋DFM组装分析,提前发现设计的缺陷,产品生产前解决设计异常。可避免在组装过程时出现设计问题,耽误生产时间、浪费研发成本。

近日,华秋DFM推出了新版本,可实现制造与设计过程同步,模拟选定的PCB产品从设计、制造到组装的整个生产流程,华秋DFM使BOM表整理、元器件匹配、裸板分析及组装分析四个模块相互联系,共同协作来完成一个完整的DFM分析。欢迎大家点击阅读原文下载体验!

华秋电子是一家致力于以信息化技术改善传统电子产业链服务模式的产业数智化服务平台,目前已全面打通产业上、中、下游,形成了电子产业链闭环生态,致力于为行业带来“高品质,短交期,高性价比”的一站式服务平台,可向广大客户提供媒体社区平台服务、元器件采购服务、PCB制造服务及可靠性制造分析服务、SMT贴片/PCBA加工服务,如有相关业务需求,请扫码填写以下表单,我们将为您对接专属服务。

点击上方图片关注我们

原文标题:【干货分享】 DFA分析预防DIP器件可焊性问题

文章出处:【微信公众号:电子发烧友论坛】欢迎添加关注!文章转载请注明出处。

-

电子技术

+关注

关注

19文章

935浏览量

60358 -

电子发烧友论坛

+关注

关注

5文章

198浏览量

1866

原文标题:【干货分享】 DFA分析预防DIP器件可焊性问题

文章出处:【微信号:gh_9b9470648b3c,微信公众号:电子发烧友论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

可焊性测试(SD)对LED车灯稳定性评估

从设计阶段排查预防PCB短路

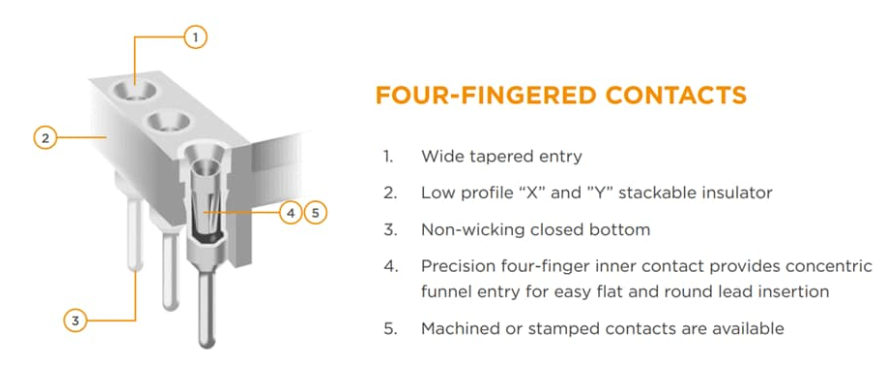

TE Connectivity DIP插座技术解析与应用指南

SMT与DIP在PCBA加工中的关键差异解析

SMT贴片加工“隐形杀手”虚焊假焊:如何用9招斩断质量隐患?

SMT贴片加工与DIP插件加工的不同

激光锡焊的温度控制原理分析

PCB丝印极性标记的实用设计技巧

焊点裂纹、虚焊频发?揭秘DIP后焊工艺中藏得最深的‘隐形杀手’!

ZSKY-JEB05DFA-SXEMI用于ESD保护的瞬态电压抑制器规格书

PCBA 加工必备知识:选择性波峰焊和传统波峰焊区别大揭秘

AEC-Q102认证之器件可焊性

【干货分享】 DFA分析预防DIP器件可焊性问题

【干货分享】 DFA分析预防DIP器件可焊性问题

评论