近日,Chiplet峰会在美国隆重举行,从会议的讨论可以得到的一个主题是:摩尔定律已死,我们只剩下封装了。本文作者Paul McLellan参会并对其进行了总结。

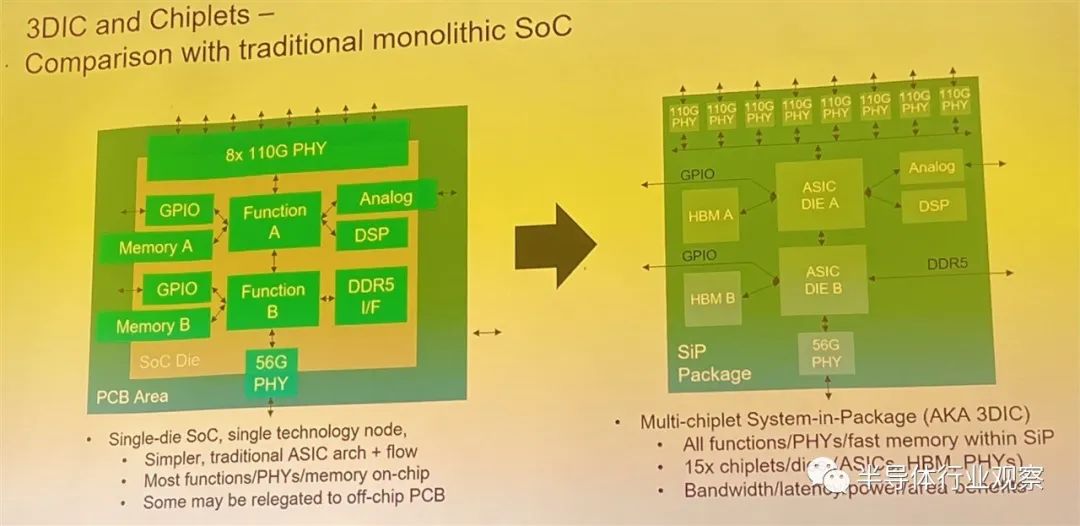

在他看来,如果您与片上系统 (SoC) 集成有任何关系,其中一切都在单个芯片上,那么您将来也会参与到小芯片(Chiplet)中去。这并不是说将来不再有单片集成,但很明显,对于最先进的节点(3nm、2nm 等),只有设计中受益于最先进工艺的部分将是在那个制程中设计,其他所有东西都将放在旧节点的小芯片上,通常称为 N-1 或 N-2 节点(参考 3nm,N-1 是 5nm,N-2 是 7nm)。

一两年前,每个关于 EDA 和设计的演讲都以通用的摩尔定律图(通常是通用的“设计差距”幻灯片)开始。但现在,摩尔定律可能已经过时或即将消亡。但即使如此,在小芯片会议上,戈登摩尔仍然是被引用的人,因为他在同一篇电子杂志文章中写了以下内容,他使用四个数据点来预测芯片上的晶体管数量每隔几年就会翻一番。他说的是十年左右,实际上是五十多年。他从同一篇文章中引用的另一句话是:

“用较小的功能构建大型系统可能会更经济,这些功能是单独封装和互连的。”

好吧,50 年后,那一天已经到来。Yole Group 预测到 2032 年基于小芯片的半导体市场将超过2050亿美元。三星代工厂估计超过 50% 的先进节点设计是基于小芯片的。

笔者表示,现在最大的芯片太大了,以至于它们超过了制造的最大标线片尺寸,根本无法很好地生产。

到目前为止的故事

峰会期间指出的一个例子是,四个 10x10mm die的良品率比单个 20x20 die高出 30%。近年来,使用 chiplet 解决这个问题的先驱经常出现在 HOT CHIPS 上,思科的“Suds”Sudhakar 透露,思科已经在 chiplet 上工作了十多年;只是没有在公开场合谈论它。最广为人知的早期基于中介层的设计是 Xilinx,它在硅中介层上将一个大型 FPGA 分成四个较小的裸片。

关于此主题的最新消息是 AMD 首席执行官苏丽莎 1 月份在 CES 上发表的主题演讲。她宣布(并展示)了 Instinct MI300。正如作者在一篇文章中所说:毫无疑问,Instinct MI300 是一个改变游戏规则的设计——数据中心 APU 混合了总共 13 个小芯片,其中许多是 3D 堆叠的,以创建一个具有 24 个 Zen 4 CPU 内核并融合了 CDNA 3 图形的芯片引擎和 8 堆 HBM3。总体而言,该芯片拥有 1460 亿个晶体管,是 AMD 投入生产的最大芯片。

像 AMD 和英特尔这样的公司已经完成了相当复杂的多芯片设计。NVIDIA 和 Apple 都创建了一些设计,其中两个大裸片使用互连桥接在一起以形成更大的设计,NVIDIA 的 Grace-Hopper 和 Apple 的 M1 Ultra 由两个 M1 Max 组成。所有这些基于小芯片的设计的共同点是它们都是在一家公司内完成的。这些小芯片旨在共同构建一个系统,在许多情况下使用专有接口。没有技术意义,更不用说商业意义了,例如,AMD 以外的其他人可以使用它的一个小芯片。

本次会议的主题之一是每个人都希望能够带着他们的超市购物车去小芯片商店(chiplet store),从货架上挑选他们想要的任何小芯片,然后能够组装一个系统级封装( SiP) 并依赖于它们一起工作。另一方面,每一个为此提出时间表的人都说至少是“五到十年”。一个很大的例外是 HBM,高带宽内存。没有人构建自己的 HBM,但有一个市场(JEDEC 已对各代 HBM 进行了标准化)。

中间情况是拥有关键小芯片的人,例如处理器,围绕它创建了一个生态系统。Ventana 表示它之所以这样做,是因为它的数据中心处理器可作为小芯片使用。处理器不能独立存在(首先,它不能启动操作系统),因此它必须被其他小芯片包围才能创建一个完整的系统。

所以今天的情况是,单一公司的多小芯片设计正在大量出货,一些小芯片正在尝试建立围绕它们的合作伙伴的生态系统,而小芯片商店的梦想还很遥远,以至于仍然是一个梦想暂且。

为什么选择小芯片?

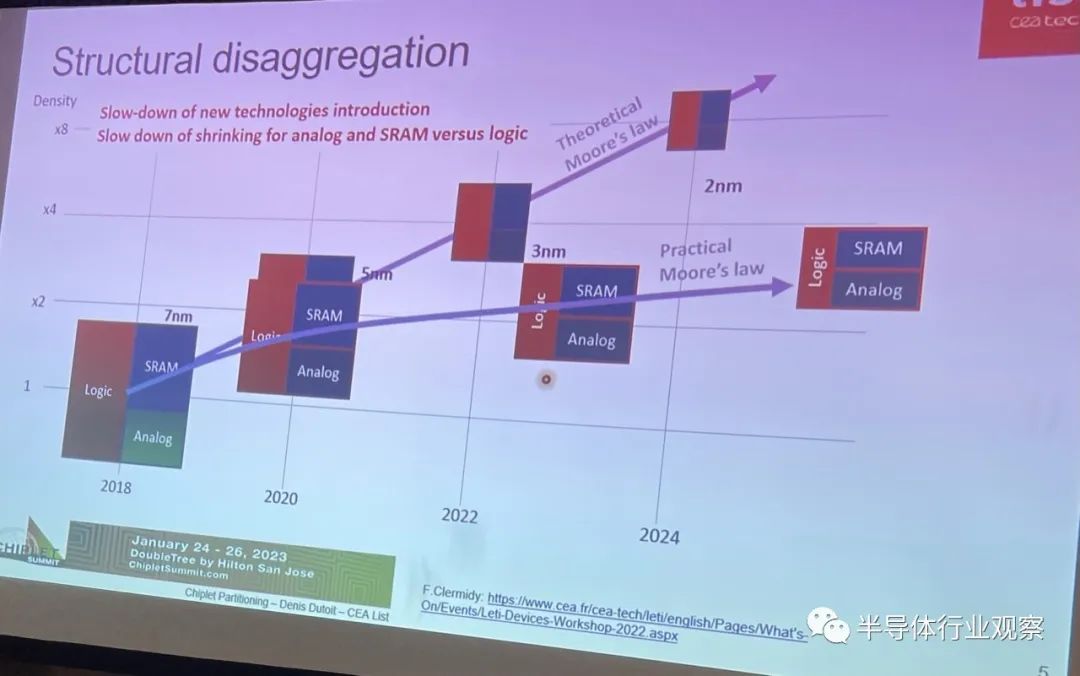

下图来自格勒诺布尔 CEA-List 的 Denis Dutoit,显示了在最先进的节点上使用小芯片的一大动机。直线对角线显示了摩尔定律,假设它同样适用于逻辑、存储器和模拟。变平的线显示了缩放是如何工作的。模拟不会扩展太多,如果有的话,内存扩展比逻辑慢得多。事实上,目前还不清楚 3nm 内存是否会比 5nm 内存小,这是最终缺乏缩放。

当缩放以这种方式运行时,将模拟和大型存储器移动到最新的工艺节点中几乎不会增加面积,但成本会更高。显而易见的反应是,“好吧,不要那样做”,不这样做的方法是将内存和模拟放在单独的小芯片上,这些小芯片采用不太先进的工艺制造(因此可能便宜得多)。例如,AMD 著名的 Zen2 SiP 有不同数量的处理器小芯片(我相信是 7nm)和一个内置 12nm FD-SOI 的 I/O 芯片。

在非常先进的节点中进行设计时将 I/O 放在单独的小芯片上的另一个原因是避免将用于 SerDes(以太网、PCIe 等)的测试芯片放在关键路径上。如果将 SerDes 放在最先进的节点上,则必须构建测试芯片并在真正的芯片流片之前对硅进行表征。使用已经存在的 SerDes 并在较旧的节点中看到硅,或者甚至像 AMD,在完全不同的工艺技术中使用它要容易得多。

有待解决的问题

在前文中,作者也总结道,单一公司的多 chiplet 设计正在大量出货,一些 chiplet 正在尝试建立围绕它们的合作伙伴生态系统,而 chiplet 商店的梦想已经足够遥远,仍然是一个梦想暂时。那么我们需要解决方案的技术问题,以便能够使用来自多家公司的小芯片进行基于小芯片的设计,这些公司没有预先计划让这些特定的小芯片协同工作。类比是你如何从不同的制造商那里购买芯片并将它们放在一块 PCB 上并拥有一个工作系统,即使设计芯片的公司从未计划过该特定系统。

当前,将基于小芯片的设计放在中介层(硅或有机)上已经成为主流,其中多个die甚至堆叠在一起。像这样的设计正在出货(例如,索尼的图像传感器有一个包含逻辑、存储器和传感器本身的三芯片堆栈)。然而,堆叠多个裸片通常需要硅通孔 (TSV),因此需要非常仔细地设计裸片,以便一切都对齐。我认为这将是一段很长的时间,如果在此之前你可以期待来自不同供应商的裸片以真正的 3D 方式堆叠的话。目前,任何真正的 3D 芯片堆叠都将由一家公司将大型设计划分为多个芯片来设计。还有主要的热挑战,而不仅仅是对齐所有 TSV 的挑战。

如果您打算进行基于小芯片的设计,你需要面对的另一个挑战是你的设计工具需要能够读入描述小芯片重要方面的内容。当中,有两个重要的标准化工作:

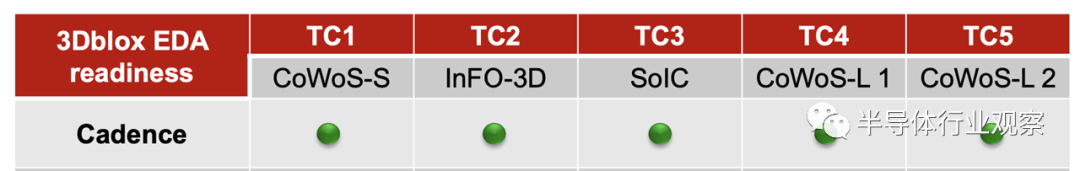

首先,台积电去年 10 月在 OIP 上宣布了 3Dblox,3Dblox 提供能够表示所有当前和未来 3D-IC 结构的通用语言结构、模块化 3D-IC 结构,使 EDA 工具和设计流程更加简单高效、确保标准化的 EDA 工具和设计流程符合 TSMC 3DFabric 技术;

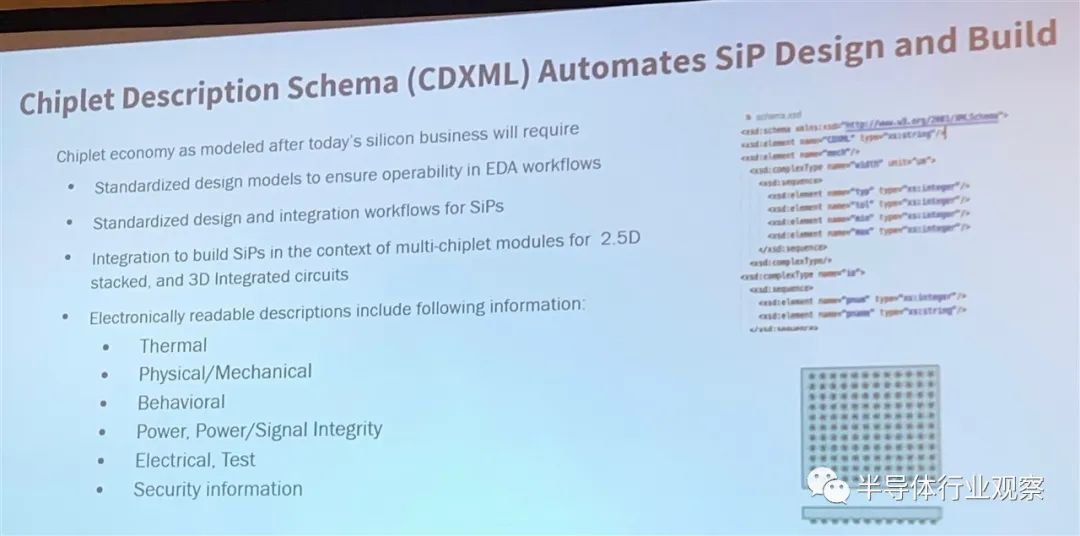

第二个标准称为 CDXML,代表芯片数据交换标记语言。该标准由开放计算项目基金会 OCP 开发。在 Chiplet 峰会的第一天,宣布 JEDEC 正在与 OCP 合作制定该标准,并将纳入JEDEC 的 Part Model Guidelines JEP30 。

有关小芯片讨论的另一热点问题是有关连接的。目前也有许多互连标准(以及一些专有的)。对于正在进行的基于小芯片的设计,似乎大多数都使用开放计算项目 (OCP)的BoW(Bunch of Wires )。

另一个有很多重量级人物支持的标准是 UCIe。UCIe 物理层包括链路初始化、训练、电源管理状态、通道映射、通道反转和加扰。UCIe 控制器包括 die-to-die 适配器层和协议层。适配器层通过链路状态管理以及协议和迁移格式的参数协商确保可靠传输。UCIe架构支持PCIe、CXL、streaming raw mode等多种标准协议。

不过,UCIe标准被峰会与会者认为“还没有完全准备好”,UCIe 标准的某些方面仍在开发中,但我想说的是,鉴于所有支持它的公司,峰会上公认的是“一旦完成, UCIe 就会获胜”。

此外,将多个小芯片封装到一个封装中不同于仅使用单个芯片。如果您使用单个芯片,则需要在封装成本和做好晶圆分类工作的成本之间进行权衡。测试仪很昂贵,因此在晶圆切割之前测试芯片的工作做得“太好”是在浪费金钱。当然,封装也要花钱,所以你不想浪费太多。——但是当你因为芯片坏了而浪费封装时,你并不是在浪费一个芯片,因为它已经坏了。

封装中的多个die的经济性完全不同。如果一个 die 逃脱了晶圆分类并且是坏的,那么当它与所有其他 die 封装时,您不仅浪费了一个坏的 die(以及封装的成本),您还在浪费同一个封装中的所有好 die也。此外,多个小芯片的封装成本远高于单个小芯片的封装成本。因此,在每个芯片进入组装过程之前对其进行彻底测试非常重要。这些裸片被称为 KGD,即 Known Good Die。

可以做一些事情来优化封装过程,例如计划能够测试仅插入一些裸片的封装。这允许在早期放入便宜的裸片然后进行测试,然后在最后放入昂贵的裸片(如最先进节点中的 CPU 或 GPU)。这避免了由于非常便宜的零件失效而牺牲非常昂贵的零件的问题。而测试多小芯片设计(甚至真正的 3D 设计)包含在IEEE 1838-2019 - IEEE 三维堆叠集成电路测试访问架构标准中。

来到安全方面,也存在很多问题。

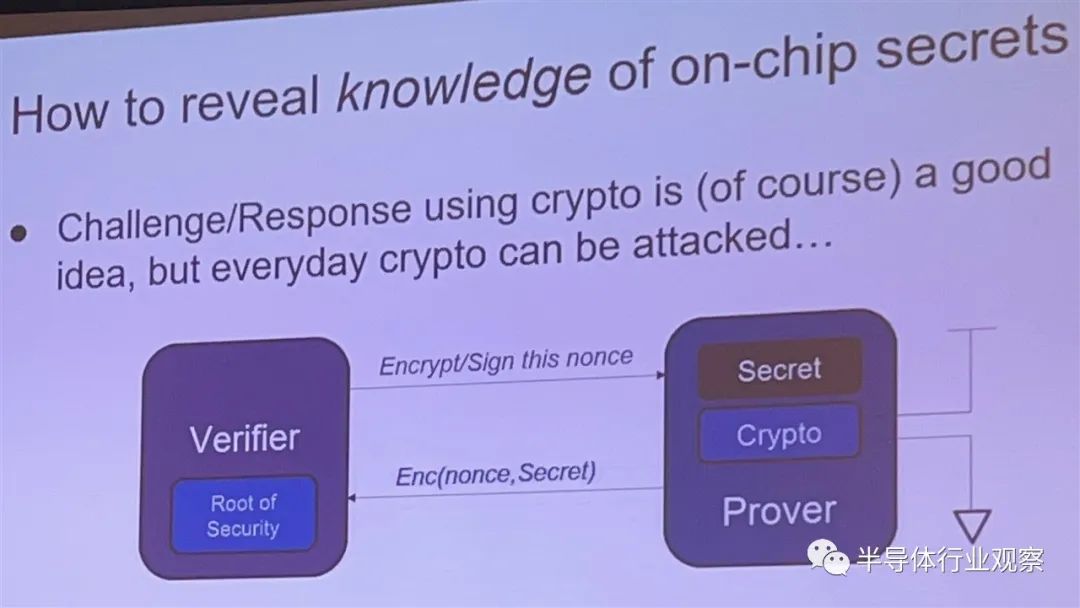

您可能知道处理安全性的现代方法是使用硬件信任根。但对于基于小芯片的系统,您需要决定的第一件事是您是否信任所有小芯片,或者是否有可能坏人以某种方式破坏了您从准陌生人那里获得的一个或多个小芯片. 您需要决定的下一件事是是否让一个小芯片负责安全性(包含带密钥的secure enclave等),然后验证所有其他小芯片是否安全。如果许多小芯片包含需要启动的微处理器,那么这可以集中处理,或者每个小芯片都必须处理自己的安全启动。

正如 Rambus Security 的斯科特·贝斯特 (Scott Best) 指出的那样,5 纳米设计非常复杂,几乎无法设计,更不用说逆向工程了。但是基于小芯片的设计更容易:当您将其分解为小芯片时,SiP 仅与最不安全的小芯片一样好。

更糟糕的是,虽然几乎不可能监控 5nm 芯片上的大量内部信号,但在多芯片设计中监控中介层上的信号更为可行。实际上,这意味着任何与安全相关的小芯片之间的通信都需要加密。当然,由于这些小芯片从未专门设计用于协同工作,所以这并不简单。处理此问题的通常方法是使用某种形式的挑战-响应,但这需要设计到每个小芯片中。实际上,需要为小芯片开发某种安全标准。

还有一点值得关注的是,如果芯片出现故障时会发生什么?鉴于您可能不了解所购买的所有小芯片的所有内部细节,您如何找到为此负责的小芯片?

虽然有些人认为这是一个大问题,但我不确定这与确定哪个 IP 块导致 SoC 故障,甚至板上的哪个芯片导致板级故障有什么不同。一种方法是预测这可能会发生,并有办法启用和禁用系统的各个方面。在微处理器中,这些被称为“chicken bits”。

在峰会期间,笔者还有了一些有趣的观察。

例如超级计算机是 HPC 的最高端,几乎总是使用 COTS 部件,即“商用现成”部件,如 Intel/AMD CPU、NVIDIA GPU、FPGA 等。正如劳伦斯伯克利实验室的 John Shalf 所说:我们知道我们负担不起从头开始制造自己的芯片。所以对他来说,小芯片是一个机会。他们可以使用商业小芯片(COTC?)并将它们紧密集成到系统中。

第二个随机的事情是汽车。汽车行业对小芯片持负面态度,因为与汽车所有振动相关的机械问题可能导致可靠性问题。请记住,汽车预计可以使用 20 年。另一方面,自动驾驶将像其他所有事情一样触及分划线限制,因此该行业也可能“硬着头皮”,因为他们无论如何都需要使用小芯片。

自动驾驶芯片的数量不足以证明成本是合理的。通过将来自不同供应商的小芯片组合在一个中介层上,总成本有望降低;另一方面小芯片比 PCB 更节能。因此需要这种集成以增加电动汽车的范围并仍然提供最大性能。

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54440浏览量

469405 -

超级计算机

+关注

关注

2文章

483浏览量

43490 -

晶体管

+关注

关注

78文章

10441浏览量

148612 -

chiplet

+关注

关注

6文章

499浏览量

13650

原文标题:Chiplet,还有不少难关要过

文章出处:【微信号:TenOne_TSMC,微信公众号:芯片半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

变频器过励磁增益及软件过流问题

拥抱Chiplet,大芯片的必经之路

多Chiplet异构集成的先进互连技术

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

西门子EDA如何推动Chiplet技术商业化落地

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

电能质量在线监测装置能区分暂态 / 稳态过压吗?

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

Chiplet与先进封装全生态首秀即将登场!汇聚产业链核心力量共探生态协同新路径!

Chiplet,还有不少难关要过

Chiplet,还有不少难关要过

评论