Chiplet仿真面临的挑战

Chiplet使系统扩展超越了摩尔定律的限制。然而,进一步的缩放给硅前验证带来了巨大的挑战。24日,芯启源EDA研发副总裁Mike Shei,工程及新产品副总裁Mike Li作了主题为"Incubating Chiplet - Challenges and Solution of New Emulators"的主旨演讲,并将讨论主题带入次日的"Next Great Breakthrough in Chiplets"专家研讨会。

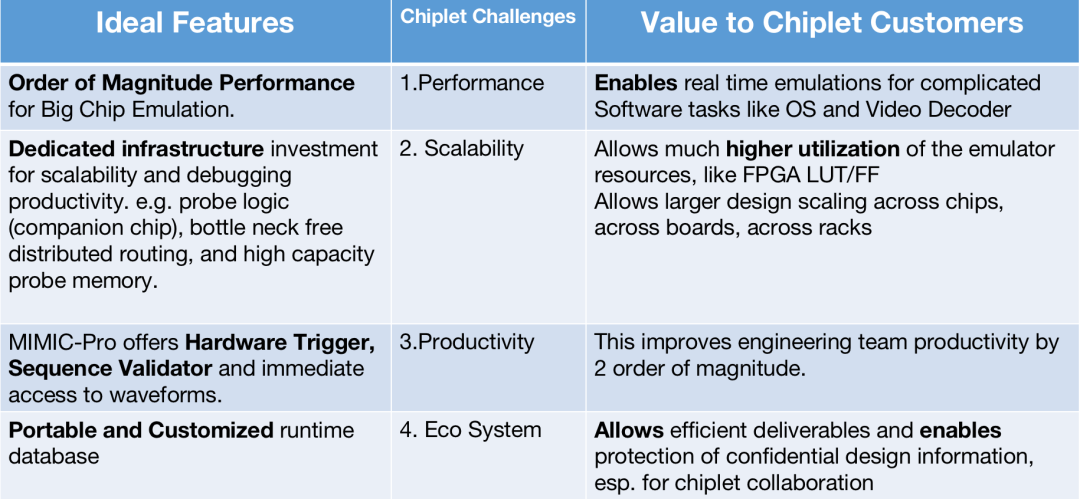

挑战 1 - 性能和功能

传统仿真器因集中式routing and clocking,随着设计规模增加,性能呈指数级下降,Chiplet技术在增加系统复杂性的同时加剧了这一挑战;

客户实时操作系统、人工智能、视频解码仿真中,为提高性能,不得不放弃仿真器提供的调试功能。

挑战 2 - 超大设计规模

小chiplet组成了大芯片系统,总设计规模高达500亿个晶体管,对仿真加速器的可扩展规模及FPGA利用率提出了更高要求;

速度为10s, 100s of Tbps的多种chiplet接口。

挑战 3 -工程效率

合理的编译时间和运行时间,与软件IDE处于同一数量级;

全局可见性和可控性,内置专用逻辑分析仪,触发器,断言,以精确定位波形,用于跨团队调试;

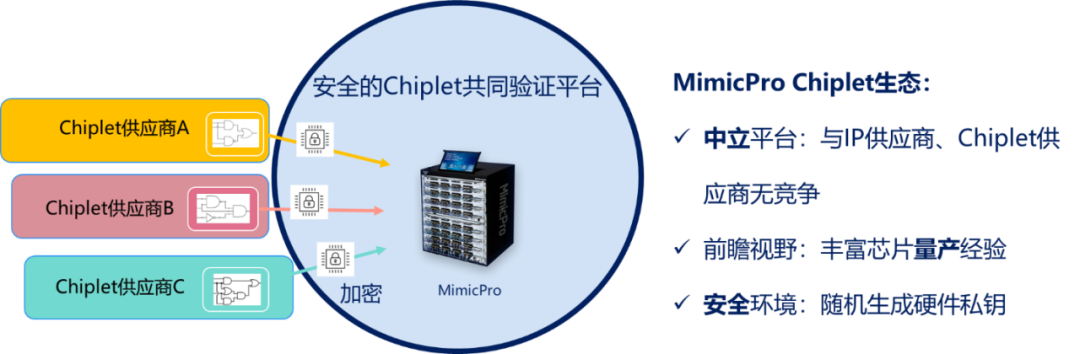

挑战 4 -多个ChipletVendor的生态系统

虚拟集成来自多个供应商的异构chiplet设计,并在一个开放和安全的平台上验证它们。

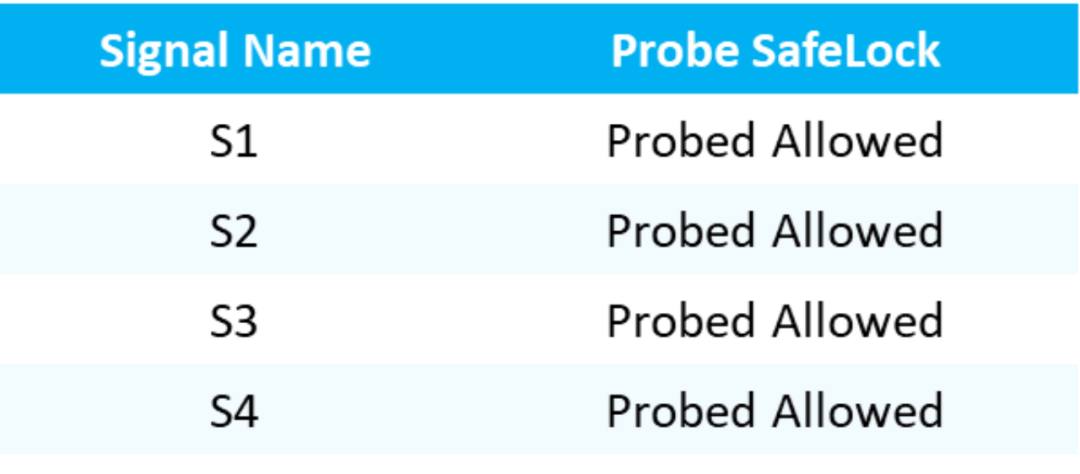

每个chiplet设计都需要有便携性,且可定义需探测的信号。

芯启源Chiplet集成平台-MimicPro系列解决方案 01

应对 1 :

MimicPro分布式routing and clocking设计

MimicPro的分布式路由和多用户时钟在跨FPGA设计中可以保持较高运行频率;

Chiplet级别的预编译提高了编译效率及运行频率。

02

应对 2 :

MimicPro高度可扩展架构

分布式routing,无系统瓶颈,性能更高;

光纤端口可实现M32 系统之间的跨机柜高速互联;

控制逻辑不消耗FPGA资源,大规模设计中实际FPGA利用率70%+。

03

应对 3 :

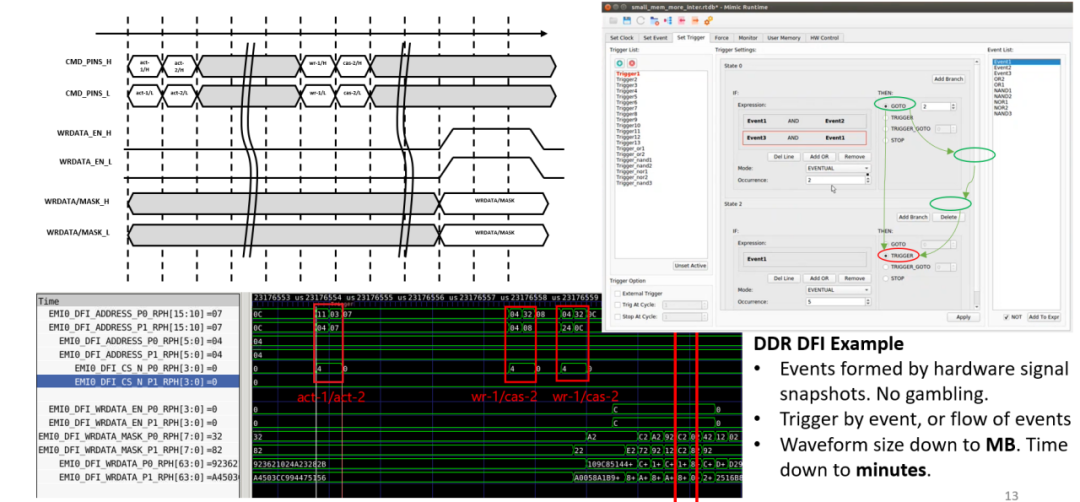

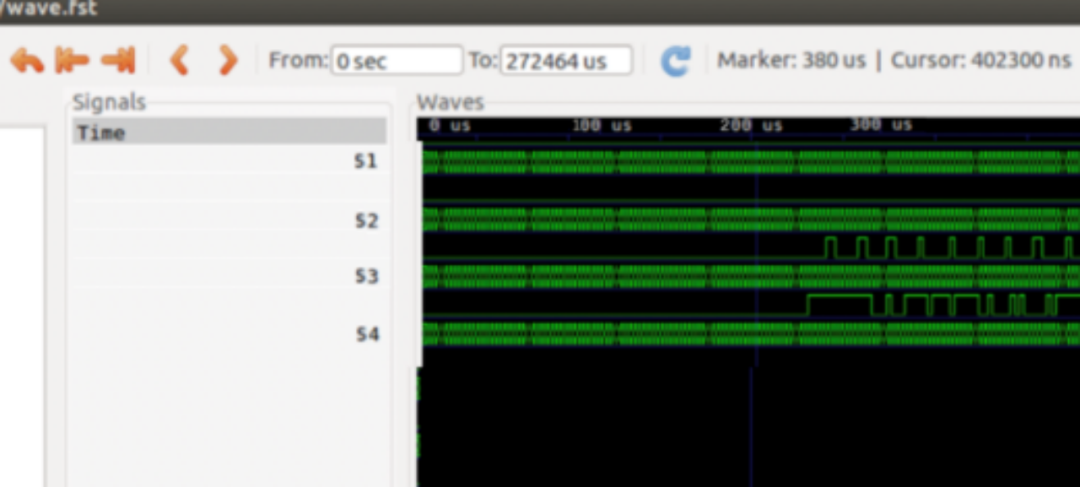

MimicPro丰富的调试功能

提供真正的HW Trigger-精确定位问题的数量级较小的波形,波形文件SizeMB vs GB;每张Solo卡搭配16GB DDR,丰富的调试/探针功能带来高的工程效率;

多周期序列捕获-能够捕捉精确的快照,以评估事件的动态流;

从序列验证到断言加速-完全加速的DV环境。

04

应对 4 :

MimicPro提供中立安全的验证平台

RTDB包括bit stream & signaling,硬件配置,探针等信息;

RunTime信息可以修改,重新映射,删除/过滤,以确保定义的调试范围;

信号披露程度完全由chiplet供应商定义。

审核编辑:刘清

-

仿真器

+关注

关注

14文章

1052浏览量

88186 -

eda

+关注

关注

72文章

3143浏览量

183718 -

视频解码

+关注

关注

1文章

56浏览量

18806 -

chiplet

+关注

关注

6文章

499浏览量

13645

原文标题:Chiplet Summit|Chiplet时代芯启源的探索之路(一)

文章出处:【微信号:corigine,微信公众号:芯启源】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

算力爆发时代IP设计面临哪些新挑战

Nullmax推出新一代基于世界模型的闭环仿真系统

浅谈复杂芯片设计中的SPICE仿真困境

先进封装时代,芯片测试面临哪些新挑战?

多Chiplet异构集成的先进互连技术

芯片可靠性面临哪些挑战

跃昉科技受邀出席第四届HiPi Chiplet论坛

攻坚农业仿真挑战:Robotec农业机器人仿真平台

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

开发无线通信系统所面临的设计挑战

TC Wafer晶圆测温系统当前面临的技术挑战与应对方案

AI 时代来袭,手机芯片面临哪些新挑战?

Chiplet仿真面临的挑战

Chiplet仿真面临的挑战

评论