文章来源:学习那些事

原文作者:前路漫漫

合金本质是金属与其他金属或非金属经混合熔化、冷却凝固后形成的具有金属性质的固体产物,而在集成电路工艺中,合金特指难熔金属与硅发生化学反应生成的硅化物(silicide)。目前常用的硅化物材料包括 TiSi₂、CoSi₂,早期工艺中则广泛采用 WSi₂。

硅化物在集成电路中的应用具有不可替代的核心价值:作为栅电极材料时,其电阻率远低于传统多晶硅,能显著改进器件开关速度,减少电流通过时的热生成,从而提升芯片整体性能;通过加热金属与硅形成的欧姆接触,是实现电信号有效传输的关键界面,该制备过程被称为退火,主要分为炉式退火和 RTP(快速热退火)两种方式;此外,硅化物还可作为电容器电极,满足器件对电容性能的严苛要求。

随着集成电路工艺特征尺寸不断缩小,器件的等效串联电阻、接触电阻等问题日益凸显,硅化物技术也随之迭代升级,从早期仅针对多晶硅栅的 polycide 技术,逐步发展到覆盖源漏区与栅区的 salicide 技术,再到满足特殊器件需求的 SAB 技术,每一代技术都针对性解决了不同工艺节点的核心痛点。

多晶硅金属硅化物(polycide)制备技术

(一)技术研发背景

当集成电路工艺特征尺寸缩小至亚微米级别时,晶体管的源、漏、栅极尺寸同步减小,导致其等效串联电阻急剧增大,严重影响芯片的信号传输速度。其中,多晶硅栅的高电阻率问题尤为突出 —— 传统多晶硅栅的高电阻会引发显著的 RC 延时,制约器件的高频工作特性,成为当时工艺升级的主要瓶颈。为解决这一问题,金属硅化物技术应运而生,其核心思路是利用金属与硅反应形成的化合物(导电特性介于硅和金属之间),降低栅极的方块电阻。

(二)核心特性与材料选择

最先应用于工业生产的硅化物技术是多晶硅金属硅化物(polycide),该技术的显著特点是仅在多晶硅栅上形成硅化物,而源、漏有源区不生成硅化物,通过 “多晶硅 + 硅化物” 的双层结构替代传统多晶硅单层结构,实现栅极电阻的降低。

polycide 技术首选硅化钨(WSi₂)作为核心材料,主要源于其优异的热稳定性 —— 在后续高温工艺中,WSi₂的阻值不会随温度变化而波动,确保器件性能的稳定性。尽管金属硅化物与硅之间会发生相互扩散,但这种扩散反而能促进 WSi₂与多晶硅形成更紧密的结合,不会对器件性能产生负面影响,这一特性进一步巩固了 WSi₂在 polycide 技术中的应用地位。

(三)详细制备工艺

薄膜沉积:首先通过 LPCVD(低压化学气相沉积)工艺沉积多晶硅薄膜,作为栅极的基础层;随后继续采用 LPCVD 工艺在多晶硅表面淀积 WSi₂薄膜。该沉积过程的反应源气体为 SiHCl₃和 WF₆,反应温度控制在 500℃左右,最终形成的 WSi₂薄膜厚度约为 1500Å,化学反应方程式如下:7SiHCl₃ + 2WF₆ → 2WSi₂ + 3SiF₄ + 14HCl。

退火处理:刚沉积完成的 WSi₂薄膜电阻率仍较高,需通过 RTP 退火工艺进行处理,使薄膜结晶质量优化,从而显著降低其电阻率,满足栅极的导电需求。

图形化工艺:沉积并退火后的双层薄膜需经过光刻和干法刻蚀形成最终的栅极结构。刻蚀过程分为两步:第一步采用 Cl₂作为刻蚀气体,去除上层的 WSi₂薄膜;第二步采用 Cl₂与 HBr 的混合气体,刻蚀下层的多晶硅,确保栅极结构的精准成型。

自对准金属硅化物(salicide)制备技术

(一)技术演进动因

当集成电路工艺特征尺寸进一步缩小至深亚微米以下时,新的技术挑战随之出现:晶体管源、漏有源区的串联电阻随尺寸缩小持续增大,同时互连接触孔的尺寸同步减小,导致接触电阻显著上升,这两大因素共同加剧了 RC 延时问题,严重制约芯片性能提升。

为同时降低有源区的串联电阻和接触电阻,产业界亟需一种能在有源区和栅区同时形成硅化物的技术。salicide 技术应运而生 —— 利用钛(Ti)、钴(Co)、镍铂合金(NiPt)等金属的特性:这些金属仅与直接接触的有源区单晶硅和栅区多晶硅发生反应生成硅化物,而不与 SiO₂等介质材料反应,使得硅化物能够自动与源区、漏区和栅区对准,因此被称为自对准金属硅化物(self-aligned silicide, salicide)。

(二)技术核心优势与基本流程

salicide 技术的核心优势在于实现了 “一次工艺、双区硅化”,在多晶硅栅表面和有源区单晶硅表面同时形成硅化物,既降低了栅极的方块电阻,又减小了有源区的串联电阻和接触电阻,从设计上大幅优化了器件的导电路径,有效降低 RC 延迟,提升芯片运行速度。此外,该技术还能增强金属与硅的附着性,形成稳定的电接触结构,提升器件的可靠性。

salicide 的基本制备流程可概括为 “沉积 - 退火 - 腐蚀” 三步:首先通过 PVD(物理气相沉积)工艺在晶圆表面均匀淀积一层金属(Ti、Co、NiPt 等);接着进行两次快速热退火(RTA)工艺,使金属与硅发生可控反应;最后通过湿法腐蚀去除未反应的多余金属,最终在有源区和栅区表面获得纯净的 salicide。根据所用金属的不同,形成的自对准金属硅化物分别为 TiSi₂(钛硅化物)、CoSi₂(钴硅化物)、NiPtSi₂(镍铂硅化物)。

不同金属硅化物的制备工艺详解

1. Ti 硅化物制备

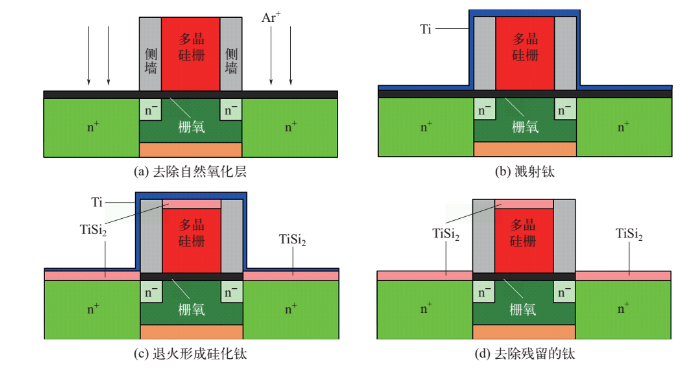

Ti 硅化物是最早应用的 salicide 材料之一,其详细制备流程及关键技术要点如下:

预处理:首先采用氨气溅射的方式去除晶圆表面的自然氧化层,确保钛与硅能直接接触发生反应;随后通过溅射工艺沉积 Ti 薄膜,部分工艺中还会在 Ti 薄膜表面再淀积一层 TiN 薄膜,其核心作用是防止 Ti 在后续退火过程中发生流动,避免硅化物厚度不均匀。

两次 RTA 退火:第一次为低温 RTA 退火,目的是初步形成硅化物;退火后通过湿法腐蚀去除未反应的 Ti 金属;第二次为高温 RTA 退火,使硅化物发生物相转变 —— 低温下形成的高阻态 Ti₃Si(电阻率 60~65μΩ・cm),在 800℃左右的高温下转变为低阻态的 TiSi₂,电阻率可降至 10~15μΩ・cm,显著提升导电性能。

工艺限制与问题:为何不直接采用一次高温 RTA 退火?核心原因是高温下硅会沿着 TiSi₂的晶粒边界快速扩散,可能在氧化硅介质层上方形成 TiSi₂,而湿法腐蚀无法去除这部分硅化物,极易导致电路短路。此外,第二次高温退火的温度并非越高越好:当温度过高时,TiSi₂会出现团块化现象,导致电阻急剧上升;且随着器件线宽减小或 Ti 硅化物厚度降低,低阻相变临界温度 T₁升高,团块化临界温度 T₂下降,可能出现 T₁≥T₂的情况,导致无法获得低阻硅化物。同时,Ti 硅化物形成过程中,硅是主要扩散物,边缘区域可参与反应的硅含量较少,导致边缘硅化物厚度较薄、薄层电阻较大,且硅的扩散还可能引发氧化物表面硅化物桥接,增加短路风险。这些问题在 0.18μm 以下工艺中尤为严重,因此 Ti salicide 仅适用于 0.5~0.25μm 特征尺寸的集成电路。

2. Co 硅化物制备

为解决 Ti 硅化物在小线宽工艺中的局限性,钴(Co)成为新一代 salicide 材料的核心选择,适用于 0.18μm~65nm 工艺节点,其技术优势及制备流程如下:

核心优势:Co 硅化物对线宽的控制精度优于 Ti 硅化物,且低温下 Co 是主要扩散物(钴向硅中的扩散速率大于硅向钴中的扩散速率),Co 会主动扩散至硅界面发生反应,从根源上避免了 Ti 硅化物的桥接现象;同时,Co 硅化物的热稳定性和电学性能更适配深亚微米工艺的需求。

物相转变特性:Co 与硅的反应具有明确的温度依赖性:第一次 RTA 退火温度控制在 300~550℃时,形成高阻态的 Co₂Si;当温度超过 550℃,Co₂Si 开始转化为中间相 CoSi;在 700℃及以上温度下,最终形成低阻态的 CoSi₂,其电阻率远低于 Co₂Si 和 CoSi,能满足器件低电阻需求。

详细制备流程:

① 自然氧化层清洗:采用专用化学溶液彻底去除晶圆表面的自然氧化层,确保后续淀积的 Co 能与衬底单晶硅和多晶硅直接接触,为硅化物的形成创造条件;

② 金属膜沉积:通过 PVD 工艺溅射一层厚度约 100Å 的 Co 膜,随后在其表面再溅射一层厚度约 250Å 的 TiN 膜,TiN 膜的核心作用是防止 Co 在退火过程中流动,保证硅化物厚度均匀性;

③ 第一次 RTA:在 550℃、氙气保护环境下进行快速热退火,使 Co 与硅发生化学反应,生成高阻态的 Co₂Si;

④ 未反应金属去除:采用湿法刻蚀工艺,将表面未反应的 TiN 膜和 Co 金属彻底去除,仅保留与硅反应生成的 Co₂Si;

⑤ 第二次 RTA:在 800℃左右、氙气保护环境下进行第二次快速热退火,使 Co₂Si 完全转变为低阻态的 CoSi₂,完成导电性能的优化;

⑥ 保护层淀积:通过 PECVD 工艺,利用 SiH₄、N₂O、He 作为反应气源,在 400℃温度下淀积一层厚度约 300Å 的 SiON 薄膜。该薄膜的核心作用是阻挡后续 BPSG(硼磷硅玻璃)层中的硼(B)、磷(P)杂质向衬底扩散,避免杂质污染导致器件阈值电压漂移等性能问题。

3. NiPt 硅化物制备

当集成电路工艺特征尺寸进入 65nm 以下节点后,Co 硅化物也面临新的挑战,镍铂合金(NiPt)硅化物凭借更优异的适配性成为主流选择,其技术背景、特性及制备要点如下:

技术研发背景:65nm 以下工艺中,杂质在 salicide 中的扩散速度显著加快,多晶硅中的掺杂杂质容易扩散到硅化物中,并进一步 “流窜” 至器件其他区域,导致多晶硅因杂质流失产生严重的空乏效应;对于 CMOS 器件,还会引发 n 型杂质与 p 型杂质的相互污染,造成 MOS 管阈值电压异常变化,影响器件性能稳定性。此外,纯镍(Ni)形成的硅化物存在明显缺陷:Ni 是主要扩散物,会导致 NiSi 深入硅衬底,引发 “硅化镍侵蚀衬底” 现象,造成器件短路和漏电问题。

材料改进与特性:为解决上述问题,产业界采用 NiPt 合金靶材(其中铂含量占 5%~10%)替代纯 Ni 靶材,最终形成 NiPtSi₂硅化物。Pt 的加入能有效抑制杂质扩散,减轻多晶硅空乏效应和 CMOS 器件杂质污染问题;同时,Pt 可显著改善 NiSi 的热稳定性,抑制其向衬底的侵蚀,降低短路和漏电风险。

制备工艺要点:NiPt 硅化物的制备同样采用两次退火工艺:首先在低温下进行第一次 RTA 退火,NiPt 合金与硅反应形成 NiPtSi;随着退火温度升高,NiPtSi 进一步反应生成 NiPtSi₂;当温度高于 400℃时,NiPtSi₂形成稳定的物相结构,其电阻率低、热稳定性好,能满足 65nm 以下工艺对低电阻、高可靠性的严苛要求。

自对准硅化物阻挡层(SAB)技术

(一)技术应用场景

在集成电路设计中,并非所有区域都需要低电阻的硅化物 —— 例如高阻值电阻器件、ESD(静电释放)保护器件等,需要通过高阻抗区域实现特定的电学功能,这与 salicide 技术降低电阻的核心目标形成矛盾。因此,需要一种能精准 “屏蔽” 特定区域、阻止硅化物形成的技术,自对准硅化物阻挡层(self-aligned block, SAB)技术应运而生。通过 SAB 技术形成的非硅化物区域(non-salicide),可用于制备高阻抗有源区电阻、高阻抗多晶硅电阻和高性能 ESD 器件,满足电路设计的多样化需求。

(二)核心原理与材料选择

SAB 技术的核心原理基于硅化物形成的特性:金属仅与多晶硅和单晶硅发生反应,而不与介质材料反应。因此,在进行 salicide 工艺前,通过淀积一层介质层覆盖需要保留高阻抗的 non-salicide 区域,可物理阻挡金属与硅的接触,从而阻止硅化物的生成;而未被介质层覆盖的区域,仍能正常进行 salicide 制备,实现 “选择性硅化”。

SAB 技术常用的介质材料包括富硅氧化物(silicon-rich oxide, SRO)、SiO₂、SiON、Si₃N₄,这些材料均具有良好的介质特性和工艺兼容性,可通过 PECVD 工艺实现高质量淀积,具体气源选择如下:

SRO:气源为 SiH₄、O₂和 Ar,核心控制参数是 SiH₄与 O₂的比率,需大于常规 SiO₂制备时的比率,以保证材料中硅的富含量;也可采用 Si₂H₆、TEOS 替代 SiH₄,用 N₂O 替代 O₂;

SiON:气源为 SiH₄、N₂O 和 Ar,通过调整各气源流量,可精准控制材料的氮氧比例,优化介质性能;

Si₃N₄:气源为 SiH₄、NH₃和 Ar,淀积过程中需控制反应温度和压力,确保薄膜的致密性和稳定性。

(三)详细工艺步骤

SAB 技术需在传统 CMOS 工艺中增加一道独立的工艺流程,具体步骤如下:

SAB 薄膜淀积:采用 PECVD 工艺在晶圆表面均匀淀积一层 SAB 介质薄膜(可根据需求选择 SRO、SiO₂、SiON 或 Si₃N₄),薄膜厚度需根据后续工艺需求精准控制,确保能有效阻挡金属与硅的接触;

SAB 光刻:通过光刻工艺在 SAB 薄膜上定义 non-salicide 区域的图形,即通过光刻胶覆盖需要保留 SAB 介质层的区域,暴露需要去除 SAB 介质层的区域(后续将形成 salicide);

SAB 刻蚀:采用干法刻蚀与湿法刻蚀相结合的混合刻蚀工艺。首先通过干法刻蚀快速去除大部分暴露的 SAB 介质层,提高刻蚀效率;随后进行湿法刻蚀,对刻蚀表面进行精细化处理 —— 若仅采用干法刻蚀,容易因刻蚀损伤导致下方硅衬底受损,进而使后续形成的 salicide 阻值偏高,湿法刻蚀可有效修复刻蚀损伤,保证硅衬底表面质量;

残留胶去除:刻蚀完成后,通过专用清洗工艺去除晶圆表面的光刻胶残留,最终形成清晰的 SAB 图案结构 ——non-salicide 区域被 SAB 介质层覆盖,salicide 区域的硅表面暴露,为后续 salicide 工艺做好准备。

-

芯片

+关注

关注

463文章

54433浏览量

469395 -

集成电路

+关注

关注

5464文章

12686浏览量

375742 -

半导体

+关注

关注

339文章

31241浏览量

266589

原文标题:半导体中的合金制备

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体中的合金制备技术详解

半导体中的合金制备技术详解

评论