与设计的其余部分相比,时序部分经常被忽视

时钟和振荡器运行您的组件并确保一切都在系统地运行。尽管时序部件很常见且很重要,但与设计的其余部分相比,它们常常被忽视。在设计时钟树时,在选择最佳时序解决方案时要考虑几个因素。我们将根据您的应用程序的形式和功能,了解选择时钟的五个常见注意事项。

1. 是同步设计还是自由运行设计?

自由运行的应用程序需要独立的时钟,没有任何特殊的锁相或同步要求。示例包括标准处理器、内存控制器、片上系统 (SoC) 和外围组件(例如 USB、PCI Express 开关)。

同步系统需要跨所有相关系统的连续通信和网络级同步。在这些应用中,基于低带宽锁相环 (PLL) 的时钟提供抖动滤波以确保维持网络级同步。例如,将所有序列化-反序列化 (SerDes) 参考时钟与高精度网络参考时钟(例如 Stratum 3 或 GPS)同步可确保所有系统节点之间的同步。同步时钟树的示例包括光传输网络 (OTN)、同步光网络和同步数字体系 (SONET/SDH)、移动回程、同步以太网和高清串行数字接口 (HD SDI) 视频传输。

考虑事项:您将使用的时钟类型取决于时序架构是自由运行还是同步。如果架构是自由运行的,则应使用时钟发生器。相反,同步设计需要抖动衰减时钟。尽管同步系统不需要具有相同的频率,但它们需要具有相同的相位。

2. 你需要什么时钟频率?

当需要多个参考频率时,时钟发生器和时钟缓冲器很有用,并且目标 IC 都在同一块电路板上,或者位于同一 IC 或现场可编程门阵列 (FPGA) 中。

时钟发生器面临的挑战是系统布局。将晶体放置在其目标 IC 附近既简单又便宜。另一方面,尽管能够降低成本,但将时钟信号从时钟发生器路由到其目标 IC 可能具有挑战性。实施仔细的设计和其他技术可以确保集中式时钟源提供相同的性能。通常,如果需要四个或更多时钟,设计人员可以通过使用时钟发生器来节省资金。

考虑事项:在考虑时钟发生器时,一定要选择能够输出与您的设计兼容的频率的发生器。Silicon Labs 的时钟发生器可以使用其ClockBuilder Pro 软件进行编程,以满足特定的频率、输出和格式要求。客户可以定制工厂编程的时钟发生器样品,通常需要两周的交货时间。

3.每个频率需要多少个?

时钟缓冲器分配输入/参考时钟的多个副本或简单派生。

参考时钟可以来自时钟发生器、XO 或系统时钟。时钟缓冲器将其输入时钟从两个输出扩展到 10 个以上。它们可以包括 I 2 C、SPI 或引脚控制功能,例如信号电平和格式转换、电压电平转换、多路复用和输入分频。这些功能通过消除组件、分压器和信号电平转换电路来节省空间和成本。

考虑事项:参考 Silicon Lab 的时序产品选择器指南,选择与您设计的输出数量(或更多)、输出格式和抖动要求相匹配的缓冲器。

4. 每个时钟需要什么样的抖动性能?

抖动性能在各种条件下各不相同,包括:

设备配置

操作频率

信号格式

输入时钟转换率和抖动

电源和电源噪声

抖动定义为时域中与理想参考时钟的时间偏差,是时序组件的关键规格。如果不加以解决,过多的时钟抖动会损害系统性能。对于 IC,抖动规格将作为时域测量给出,或者在高性能应用中更常见的是,作为 RMS 相位抖动中的频域测量给出。

考虑事项:应估计总时钟树抖动,以确定在采用时钟树之前是否有足够的系统级设计余量。如果抖动太高或指定不当,时钟性能较差的组件可能会危及整个系统。重要的是要注意时钟树的抖动不仅仅是每个组件的 MAX 规格的总和;它是每个设备的 MAX RMS 抖动的平方和的根。

参考 Silicon Labs 的相位噪声抖动计算器工具,轻松识别满足抖动要求的时钟和振荡器。

5. 每个时钟需要什么样的信号格式级别?

时钟和缓冲器有多种不同的格式,包括:

扇出:定义单个逻辑门的输出可以馈送的最大数字输入数的术语。大多数晶体管-晶体管逻辑 (TTL) 门最多可以为 10 个其他数字门或设备供电。因此,典型的 TTL 门的扇出值为 10。

低压正发射极耦合逻辑 (LVPECL):正发射极耦合逻辑 (PECL) 的功率优化版本使用 3.3V 正电源。

低压差分信号 (LVDS):不仅是物理层规范,而且是通信标准和应用程序经常添加的数据链路层。

电流模式逻辑 (CML):在标准电路板上以 312.5Mbit/s 和 3.125Gbit/s 之间的速度传输数据。

高速电流控制逻辑 (HCSL):具有两个可在 0 和 14mA 之间切换的输出引脚的差分逻辑。

低压互补金属氧化物半导体 (LVCMOS):LVCMOS的目标是缩小集成电路的器件几何尺寸,从而降低工作电压。

考虑事项:使用符合您的设计和相关要求的格式。上述每个时序部件都有许多不同的格式以支持各种设计类型。

Silicon Labs 时序解决方案

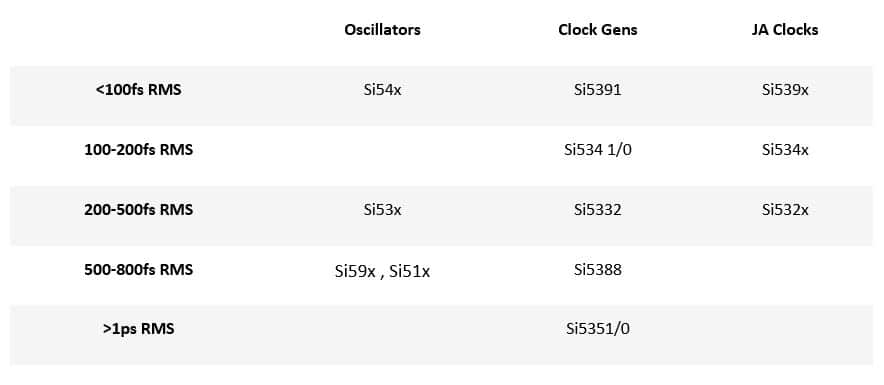

作为高性能时钟和振荡器的领导者,Silicon Labs 的计时解决方案提供业内最广泛的晶体振荡器、时钟发生器、时钟缓冲器和抖动衰减器系列产品组合(图 1)。此外,Silicon Labs 为时钟提供最大的频率灵活性以及业界最低的抖动。在购买时钟之前,一定要问自己这里列出的五个问题,以帮助缩小支持您设计的最佳选择范围。

图 1:Silicon Labs 计时解决方案组合结合了频率灵活性和一流的抖动性能。(来源:对称电子)

审核编辑hhy

-

时钟树

+关注

关注

0文章

58浏览量

11297

发布评论请先 登录

宇树UniStore正式全面开放

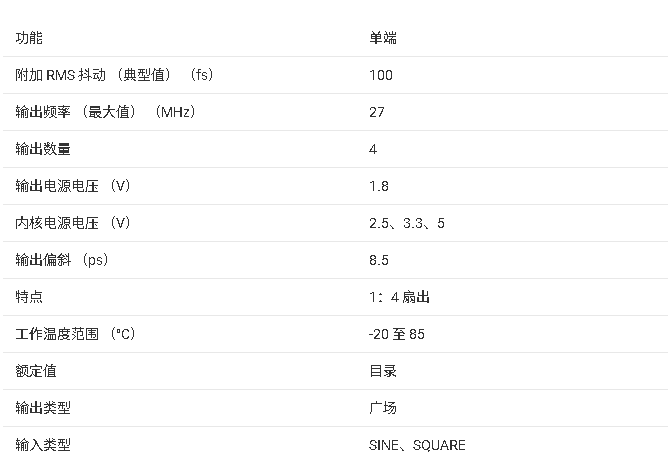

AD9522-5:高性能时钟发生器的设计与应用

AD9516 - 5 14 输出时钟发生器:高精度时钟解决方案

LMH2190:一款高性能四通道时钟树驱动器的深度剖析

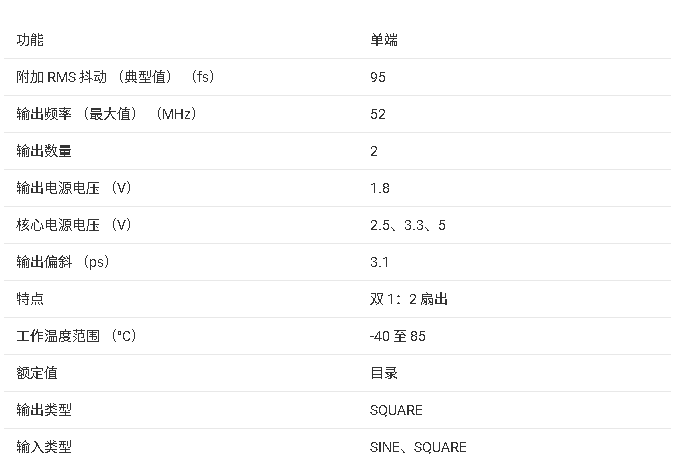

探索LMH2191:52 MHz时钟树驱动的卓越之选

时钟树解析

E203工程源码时钟树解析

时钟设计优化实战

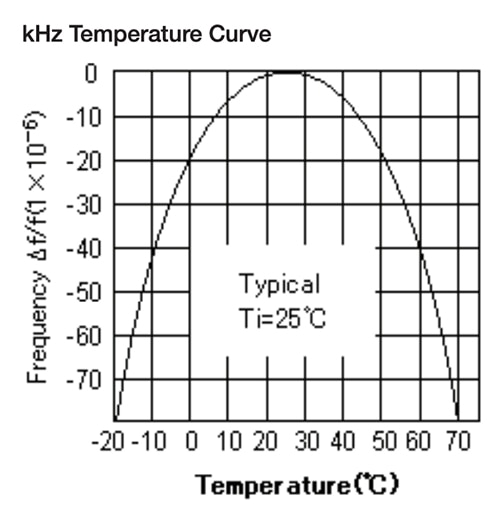

kHz 晶体选型设计师指南

LMH2191 双通道52MHz时钟树驱动器技术文档总结

时钟树设计师的 5 个问题

时钟树设计师的 5 个问题

评论