欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:校招FPGA笔试讲解

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1656文章

22299浏览量

630673

原文标题:校招FPGA笔试讲解

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

翠展微电子携手上海电机学院助力功率半导体人才培养

继本月初在上海工程技术大学的成功招聘与校企交流之后,翠展微电子校招团队接续发力,赴上海电机学院参加“2026 届毕业生英才通道启动仪式・优秀雇主颁奖仪式暨成员单位秋季招聘会”。此次行程不仅是公司聚焦

2025开放原子校源行山东大学站圆满落幕

近日,由开放原子开源基金会主办,山东大学、齐鲁软件园发展中心、中国通信学会、齐鲁开源社联合承办的开放原子校源行(山东大学站)成功举行。本次活动汇聚政企校多方力量,分享前沿开源技术,以实践赋能和思想碰撞的双轨教学模式,构筑学生开源创新高地。

招兼职pss/e仿真讲师

招兼职pss/e仿真讲师或咨询人员,如您想挣点外块,积累资源,充实生活,请联系我

要求有实际项目经历,三年以上项目经历,表达能力较好

微信15501239699 ,邮件soft@info-soft.cn

发表于 08-25 17:25

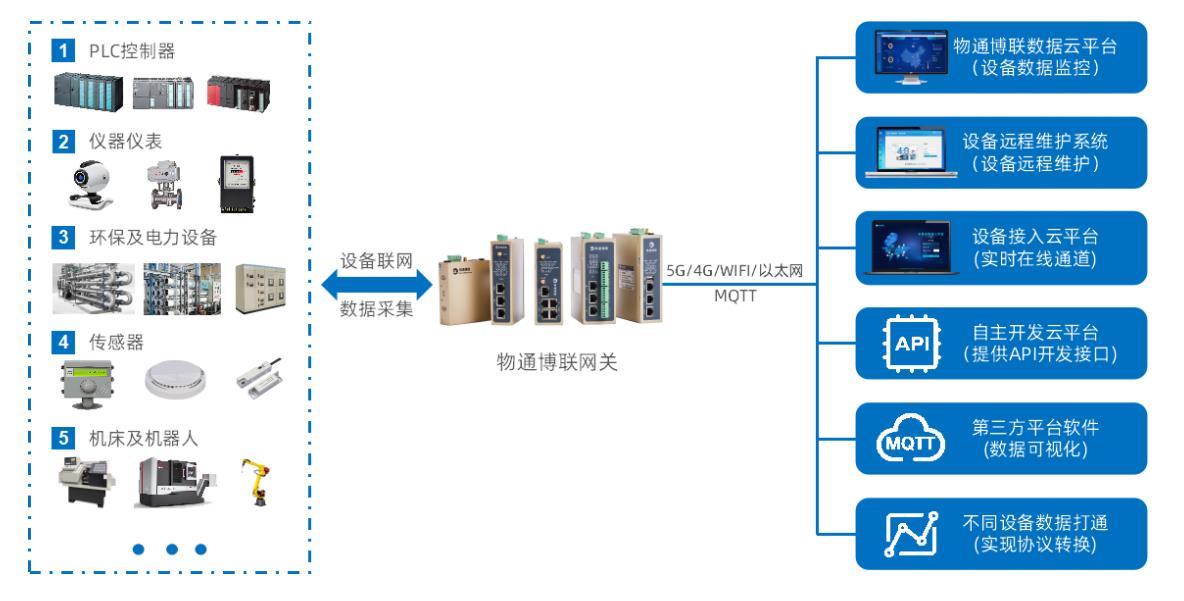

物联网解决方案之校平机PLC数据采集方案

行业背景 在金属加工行业,校平机作为矫正板材变形的关键设备,直接影响汽车钢板、家电面板等产品的精度与质量。校平机通过PLC(可编程逻辑控制器)进行精准控制,以确保板材校平的质量和效率。然而,随着工厂

2025开放原子校源行太原站成功举办

近日,开放原子“校源行”(太原站)在中北大学成功举办。工业和信息化部信息技术发展司、山西省工信厅、山西省教育厅,以及地方工信部门、高校、头部科技企业代表等600余人共话开源生态,推进开源教育。

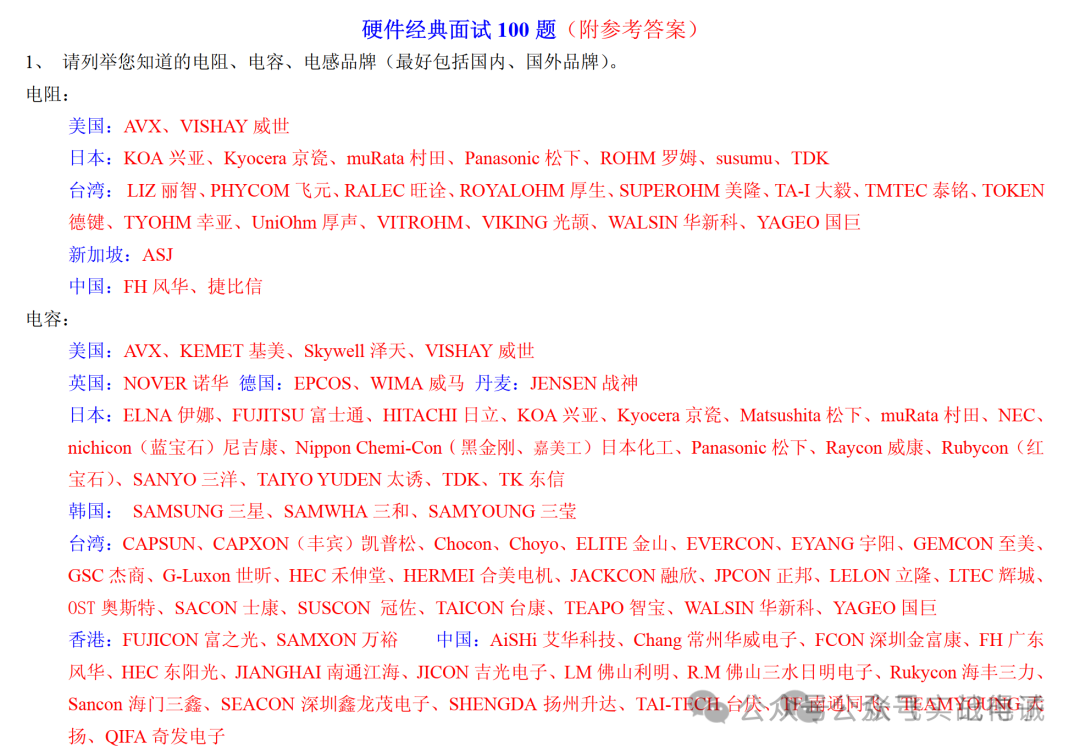

常见电子类硬件笔试题整理(含答案)

violation,画图说明,并说明解决办法。(威盛VIA2003.11.06上海笔试试题)

Setup/hold time是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号

发表于 06-27 15:05

开放原子校源行助力职业教育升级

近日,由开放原子开源基金会与杭州市经信局联合主办,浙江机电职业技术大学、浙江省工业软件产业技术联盟等机构承办的“开放原子校源行”(浙江机电职业技术大学站)活动成功举行。

开放原子校源行5月进展回顾

2025年5月,开放原子“校源行”项目在多个维度持续推进并取得显著成效:在多所高校成功举办开源主题活动,稳步推进开源人才评价机制在试点高校落地;与“开源之夏”达成战略合作,拓展高校师生参与开源实践的渠道;推进课程共建;加快开源社团建设。以下为本月“校源行”的详细运营报告。

【硬件方向】名企面试笔试真题:大疆创新校园招聘笔试题

名企面试笔试真题:大疆创新校园招聘笔试题-硬件

是几年前的题目,不过值得参考一下哦

纯分享贴,有需要可以直接下载附件获取完整资料!

(如果内容有帮助可以关注、点赞、评论支持一下哦~)

发表于 05-16 17:31

硬件工程师面试/笔试经典 100 题

分享一些常见的硬件工程师面试/笔试题。公众号后台回复关键字:100题,可获取完整的PDF。--END--免责声明:本文转自网络,版权归原作者所有,如涉及作品版权问题,请及时与我们联系,谢谢!加入粉丝

校平机PLC数据采集物联网解决方案

痛点分析 在某金属板材加工工厂中,多台校平机承担着将各种规格金属板材校平的关键任务。校平机通过PLC(可编程逻辑控制器)进行精准控制,以确保板材校平的质量和效率。然而,随着工厂生产规模

C语言笔试题

来看一个C语言笔试题,应该很少有人能给出正确答案。 #include int f(){ printf("this is f ..."); return 1;}int g(){ printf

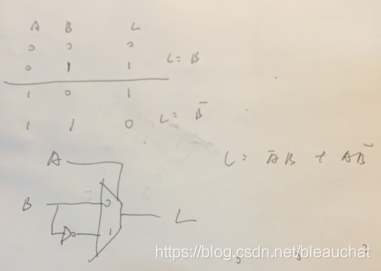

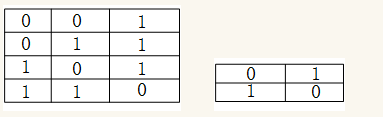

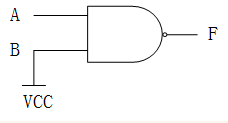

校招FPGA笔试讲解

校招FPGA笔试讲解

评论