近日,芯动科技高速接口IP三件套之明星产品--InnolinkChiplet互连解决方案,相继亮相第二届中国互连技术与产业大会、智东西Chiplet公开课。芯动科技技术总监高专分享了两场专业演讲,就行业Chiplet技术热点和芯动Innolink Chiplet核心技术,与腾讯、阿里、中兴、百度、是得科技等知名企业,以及中科院物理所、牛津大学、上海交大等学术科院领域名家交流分享,共同助推Chiplet互连技术的创新与应用。

多晶粒Chiplet技术是通过各种不同的工艺和封装技术,让多个模块芯片与底层基础芯片有机结合,形成一个大带宽、高密度的系统芯片,突破单晶圆性能和良率瓶颈,以更具性价比的路线满足产业界日益增长的对芯片性能的需求,是技术发展大势所趋。芯动作为在高速接口互连技术深耕十多年的赋能者,响应客户和市场需求,早于两年前就推出了适用多个应用场景、在先进工艺量产验证成功的自主Chiplet IP解决方案。该方案也是首套物理层兼容UCIe国际标准的Chiplet解决方案,跨工艺跨封装,目前已在全球范围内实现广泛兼容并成功商用落地,在硅基板、MCM封装基板、化合物基板以及PCB级等互联场景率先产业化,发挥Chiplet多晶粒技术的成本和性能优势,助力芯片设计企业和系统厂商实现产品成功。

“天下大势,分久必合合久必分,半导体行业亦如是。”

——芯动科技,高专

INNOSILICONChiplet发展现状技术背景和优势前景

Chiplet(芯粒)通俗来讲是对大芯片系统的拆分和重组,是系统级芯片(SoC)集成发展到后摩尔时代后,持续提高集成度和芯片算力的重要途径。Chiplet通过分解手段,将SoC中CPU、加速器等资源解耦,甚至将同种资源也拆分为更细粒度的模块,使得芯粒能够在多种设计中重用。在芯粒生态中,用户可以根据自己的需求,从各种供货商提供的芯粒中挑选自己想要的芯粒,然后组合为个性化系统。因其能够有效降低芯片开发门槛,使得芯片开发“降本增效”,业内众多巨头都在大力投入Chiplet技术的研发和落地。

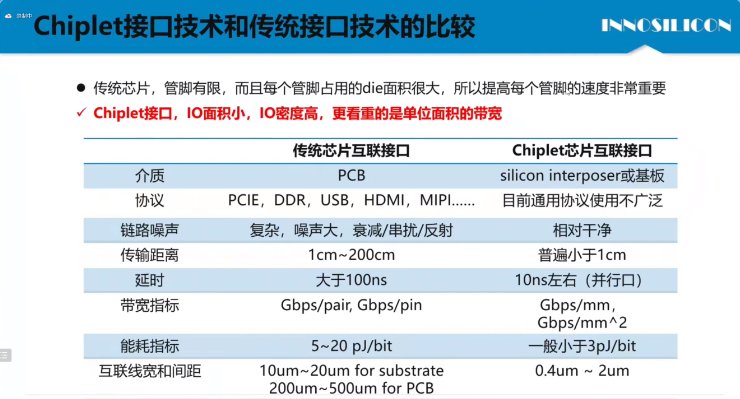

▲Chiplet接口技术和传统接口技术比较

对CPU/GPU等芯片厂商而言,Chiplet可以缩小单die缩小尺寸、降低复杂度,实现芯片设计复杂度及设计成本的下降;在当前先进工艺场景下,Chiplet“模块化剖分”的思路更有利于提高大型芯片良率、降低芯片制造成本,同时缩短开发周期和难度,便于部分模块的迭代和优化,突破die size上限。对芯片系统集成商而言,不同芯片的自由组合也将带来产品生态的开放繁荣,优势集合,构建差异化产品。对于芯片制造商Foundry而言,Chiplet的不同工艺组合将带来更多高端工艺客户和die集成业务。所以说,Chiplet优势明显,前景一片大好。

与此同时,Chiplet互连也有诸多实现难点及痛点。Chiplet互连技术对带宽需求更大,要求更低的延时和功耗,多应用场景还需要实现跨工艺、跨封装互联,同时Chiplet线宽和间距小,互联密度极高,因此技术实现更具挑战性。此外,无广泛使用的统一接口标准、片间互联导致在PCB上测试和debug困难,这些也是Chiplet应用量产亟待解决的问题。

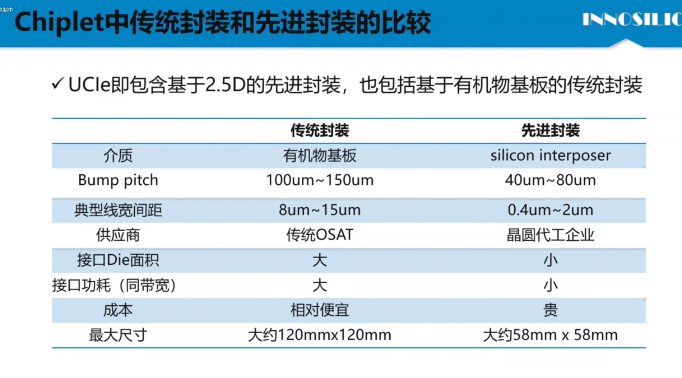

▲Chiplet中传统封装和先进封装的比较

我们所说的Chiplet互联优势主要区别于传统互联技术。传统芯片主要基于PCB介质,支持传输距离1~200cm,管脚有限,而且每个管脚占用的die面积很大,所以提高每个管脚的速度非常重要。Chiplet接口则可用于siliconinterposer或基板,传输距离普遍小于1cm,对低延时要求高,IO面积小,IO密度高,更看重的是单位面积的带宽,另外Chiplet在传统封装和先进封装上的间距、功耗、die面积、带宽、成本、尺寸需求也不一样。

INNOSILICONInnolinkChiplet芯动UCIe Chiplet解决方案基于前期在DDR、SerDes等高速接口技术的自主创新和先进工艺的量产验证,集十多年IP前后端、工艺定制、封测量产全流程之经验能力,芯动科技专门针对Chiplet互联推出了Innolink互连解决方案。

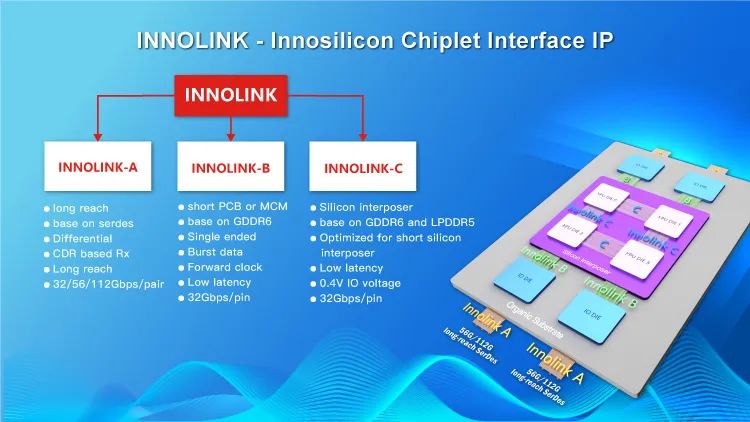

这是首个物理层兼容UCIe国际标准Chiplet超高速通讯解决方案,跨工艺、跨封装,已完成主流先进工艺开发验证并授权多个项目成功量产。该方案包括INNOLINK-A/B/C三种规格,支持硅基板、普通基板和PCB板3种互连模式,在Die to Die、Chip to Chip、Package to Package、Board to Board各种不同应用场景下,具备低延时、低功耗、高带宽密度以及高性价比、高可靠性的优势,可全栈式协助芯片设计企业和系统厂商提高SoC研发效率,降低风险,为数字时代算力需求升级提供有力支持。

▲InnolinkChipletA/B/C实现方法

▲InnolinkChipletA/B/C实现方法值得一提的是,芯动兼容UCIe国际标准的Chiplet解决方案几乎是在UCIe标准发布同一时间发布的。据高专介绍,芯动在Chiplet技术领域积累了大量的客户应用需求经验,几年前就开始了Innolink Chiplet的研发工作,率先明确InnolinkB/C基于DDR的技术路线,并于2020年的Design Reuse全球会议上首次向业界公开Innolink A/B/C技术。得益于正确的技术方向和超前的布局规划,INNOLINK-B/C的架构和方案与UCIe基本一样,都是针对标准封装和先进封装单独定义IO接口,都是单端信号,forward clock、sideband通道、datavalid信号、burst首发、Idle低功耗等均方向一致。

具体而言,INNOLINK-A是基于SerDes的互联技术,适用于较长的传输距离和较大信号衰减,可实现板卡到板卡之间的互连,支持32/56/112Gbps/pair传输速率。INNOLINK-B对应UCIe标准中的标准封装,基于DDR技术单端信号,可支持短距PCB或MCM,同时兼容Die to Die和Chip to Chip,支持32Gbps/pin传输速率。INNOLINK-C则对应UCIe标准中的先进封装,结合了GDDR和LPDDR的技术特点,针对Silicon Interposer做了优化,IO电压可低至0.4V,支持32Gbps/pin传输速率。

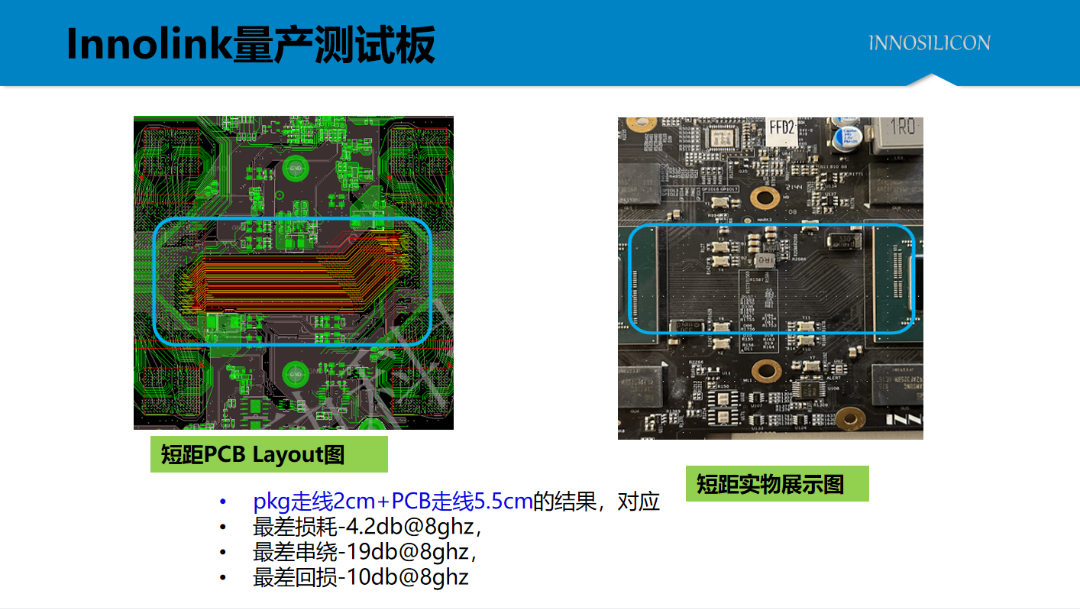

▲InnolinkChiplet量产测试板

▲InnolinkChiplet量产测试板芯动Innolink Chiplet可提供物理层方案,客户自主构建协议层,也可提供PHY&Controller打包方案,这两种方案均已授权客户量产测试。围绕着Innolink Chiplet技术,芯动同时还提供封装设计、可靠性验证、信号完整性分析、DFT、热仿真、测试方案等全栈式服务,使得芯片设计企业和系统厂商能够快速便捷地实现多Die、多芯片之间的互连,有效简化设计流程。

芯动的Chiplet也与其全系高端DDR、32/56/112G SerDes共同构成了芯动高速接口IP三件套,在全球范围内具备核心竞争力。芯动的一站式高性能、高可靠IP具有三大优势:支持最新的接口协议,诸如GDDR6/6X、HBM3/2e、LPDDR5X/5、UCIe Chiplet、HDMI2.1、USB4.0等,全面覆盖通用高速接口协议;支持最先进的FinFET工艺,在各大代工厂和各级别工艺制程全面布局;先进接口IP在先进工艺上拥有大量的量产记录和客户群,流片验证超过200次,为IP质量提供了可靠保证。

▲芯动高速接口IP三件套解决方案“

▲芯动高速接口IP三件套解决方案“作为全球一站式IP和芯片定制提供商,芯动一直坚持合规化、商业化、专业化运营,坚持以质量和口碑为发展生命线,深耕高速接口IP十六年,拥有专业知识和经验丰富的开发团队,是业界极富口碑的IP和定制服务老牌厂商。16年来,芯动服务了AMD、微软、亚马逊、高通、安盛美等全球数百知名企业,未来还将持续为全球客户提供极具竞争力的全栈式解决方案,客户至上、需求驱动,助力设计企业迅速抓住关键市场。

”

芯动科技(Innosilicon)是一站式IP和芯片定制及GPU领军企业,聚焦计算、存储、连接等三大赛道,提供跨全球各大工艺厂(台积电/三星/格芯/中芯国际/联华电子/英特尔/华力)从55纳米到5纳米全套高速混合电路IP核和IP相关芯片定制解决方案。成立16年来,芯动已赋能全球数百家知名客户,授权逾80亿颗高端SoC芯片进入规模量产,拥有100%成功率以及过十亿颗FinFET定制芯片成功量产的骄人业绩。公司在武汉、珠海、苏州、西安、北京、上海、深圳、大连、成都等地均设立了研发中心,拥有完备的研发和质量管理体系,一站式提供从规格到量产的全套解决方案。客户的成功就是我们的成功!芯动风华系列GPU瞄准商用市场,响应客户需求,通过不断升级GPU内核,打造体验流畅的GPU处理器产品。先后推出了“风华1号“””4K级多路服务器GPU、“风华2号”4K级三屏桌面和嵌入式GPU,性能强劲,跑分领先,功耗低,自带智能计算能力,全面支持国内外CPU/OS和生态,包括Linux、Windows和Android。16年来,芯动科技始终致力于赋能全球数字化创新,保持合规化运作,从IP到验证,从设计到量产,从芯片到系统,我们用各种灵活共赢的商业模式,全方位服务于全球客户及开发者,助力合作伙伴快速实现产品成功。

*了解更多IP和ASIC定制,请访问芯动官网或垂询Sales@innosilicon.com.cn;客户的成功就是我们的成功,芯动竭诚为您服务。

INNOSILICON

更多新闻,等你发现

➭芯动科技高性能计算IP“三件套”,满足新一代SoC带宽需求➭惊艳全场!风华2号桌面GPU性能领先,体验流畅,实现商用突破➭10Gbps!芯动科技最新LPDDR5/5X IP成功量产➭芯动科技发布GDDR6X显存技术➭量产验证成功!芯动科技物理层兼容UCIe国际标准的Chiplet解决方案正式发布➭国产4K级高性能GPU “风华1号”重磅发布,性能实现突破

怦然芯动 无限可能

联系方式|18502769661

Sales@innosilicon.com.cn

点击阅读原文查看直播课回放

点击阅读原文查看直播课回放

原文标题:芯动兼容UCIe标准的最新Chiplet技术解析

文章出处:【微信公众号:芯动科技Innosilicon】欢迎添加关注!文章转载请注明出处。

-

UCIe

+关注

关注

0文章

53浏览量

2037

原文标题:芯动兼容UCIe标准的最新Chiplet技术解析

文章出处:【微信号:Innosilicon,微信公众号:芯动科技Innosilicon】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构

跃昉科技受邀出席第四届HiPi Chiplet论坛

得一微电子受邀出席第四届HiPi Chiplet论坛

CMOS 2.0与Chiplet两种创新技术的区别

芯动科技与知存科技达成深度合作

小芯片(Chiplet)技术的商业化:3大支柱协同与数据驱动的全链条解析

新思科技UCIe IP解决方案实现片上网络互连

芯动科技全套IP通过ISO 26262汽车功能安全最高等级认证

技术资讯 I 完整的 UCIe 信号完整性分析流程和异构集成合规性检查

芯动兼容UCIe标准的最新Chiplet技术解析

芯动兼容UCIe标准的最新Chiplet技术解析

评论